триггера, два элемента задержки, шесть элементов И и четыре элемента ИЛИ, причем первый вход первого элемента ИЛИ соединен с пятым входом блока, второй вход - через первый элемент задержки с четвертым входом блока и первым входом второго элемента ИЛИ, второй вход которого подключен к третьему входу блока, а выход - к нулевым входам первого и второго триггеров и пятому выходу блока, первый вход первого элемента И соединен с вторым входом блока, второй вход - с третьим входом блока и первым входом второго элемента И, подключенным вторым входом к первому входу блока, выход генератора тактовых импульсов соединен с первыми входами третьего и четвертого элементов И и узла синхронизации, второй вход которого подключен к выходу первого элемента ИЛИ, а выход к второму выходу блока, единично му входу первого триггера, нулевому входу третьего триггера и первому входу третьего элемента ИЛИ, выходом соединенного с единичным входом второго триггера и десятым выходом блока, а вторым входом - с третьим выходом блока и выходом пятого элемета И, первый и второй входы которого соединены соответственно с нулеBfcOM выходом третьего триггера и. с выходом первого элемента И и единичным входом третьего триггера, единичным выходом подключенного к первому входу шестого элемента И, второй вход которого соединен с третьим входом блока, а выход - с восьмым выходом блока и первым входом четвертого элемента ИЛИ, выход которого является седьмым выходом блока, а второй вход соединен с выходом второго элемента И, выход второго триггера соединен с вторым входом четвертого элемента И, выход которог является шестым выходом блока, выход первого триггера подключен к девятому выходу блока и к второму входу третьего элемента И, выход которого соединен с четвертым выходом блока и через второй элемент задержки с первым выходом блока.

3. Устройство ПОП.1, отличающееся тем, что преобразователь кода содержит два распределителя импульсов, два регистра, две группы элементов И и элемент ИЛИ, причем группа входов первого регистра соединена с группой входов преобразователя, первые входы распределителей импульсов соединены с четвертым входом преобразователя и первым входом второго регистра, группа выходов которого соединена с первой и третьей группами выходов преобразователя, вторые входы распределителей импульсов соединены соответственно с вторым и третьим входами преобразователя, а группы выхо. дов - соответственно с первыми входами элементов И первой ивторой групп, группа выходов второго распределителя импульсов соединена с четвертой группой выходов преобразователя, а выход - с вторым выходом преобразователя, группа выходов первого регистра соединена с второй группой выходов преобразователя и вторыми входами элементов И первой группы, выходы которых соединены с группой входов элемента ИЛИ, выходом соединенного с первым входом преобразователя, группа входов второго регистра подключена к выходам элементов И второй группы, вторые входы которых соединены с вторым входом преобразователя.

.4. Устройство ПОП.1, отличающееся тем, что блок сравнения содержит группу элементов равнозначности, группу элементов И, элемент И и элемент ИЛИ, причем первый и второй входы элементов равнозначности группы соединены соответственно с первой и второй группами входов блока, а выходы - с первыми входами соответствующих элементов группы, вторые входы которых подключены к третьей группе входов блоа, а выходы - к группе входов элеента ИЛИ, соедда1енного выходом с ервым ВХОДСН4 элемента И, второй вход выход .которого являются соответстенно входом и выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1977 |

|

SU703799A1 |

| Многоканальное устройство для сопряжения | 1980 |

|

SU903852A2 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1474664A2 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1988 |

|

SU1571602A2 |

| Преобразователь кодов | 1980 |

|

SU922722A2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

- 1.

Изобретение относится к вычислительной технике, а именно к устройствам сопряжения управлянвдей вычиспительной машины (УВМ) с каналами связи, и моАет быть использовг но

при построении управляющих вычислительных комплексов.

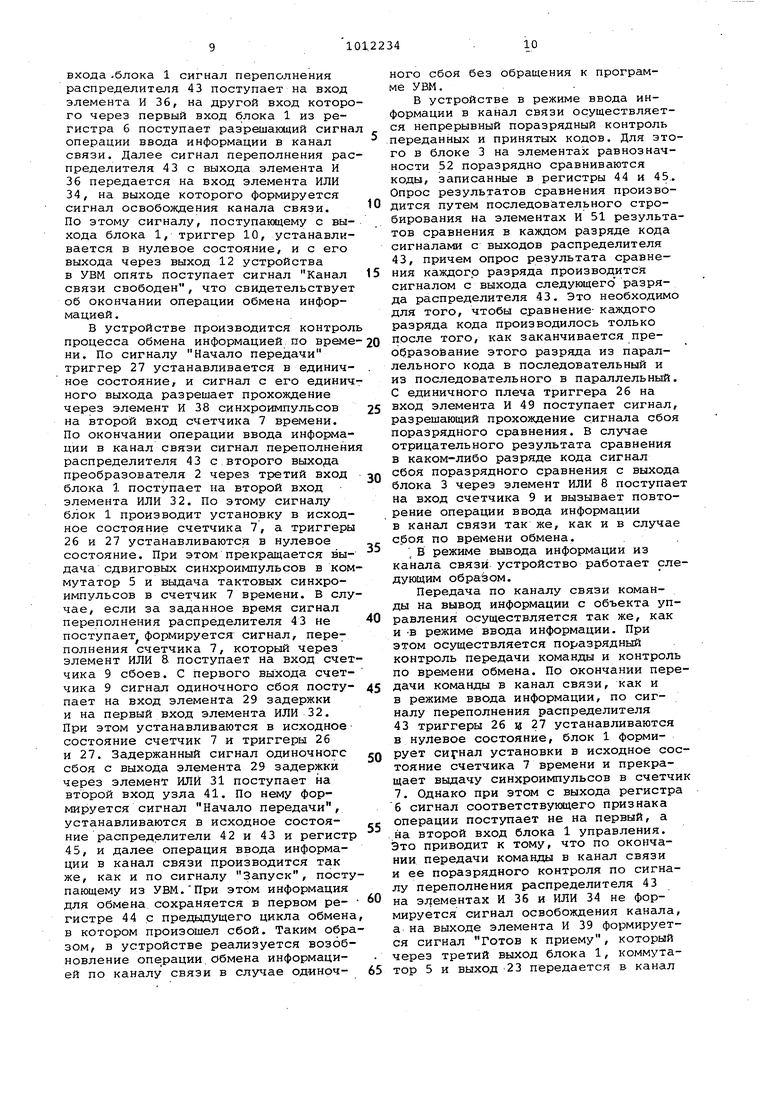

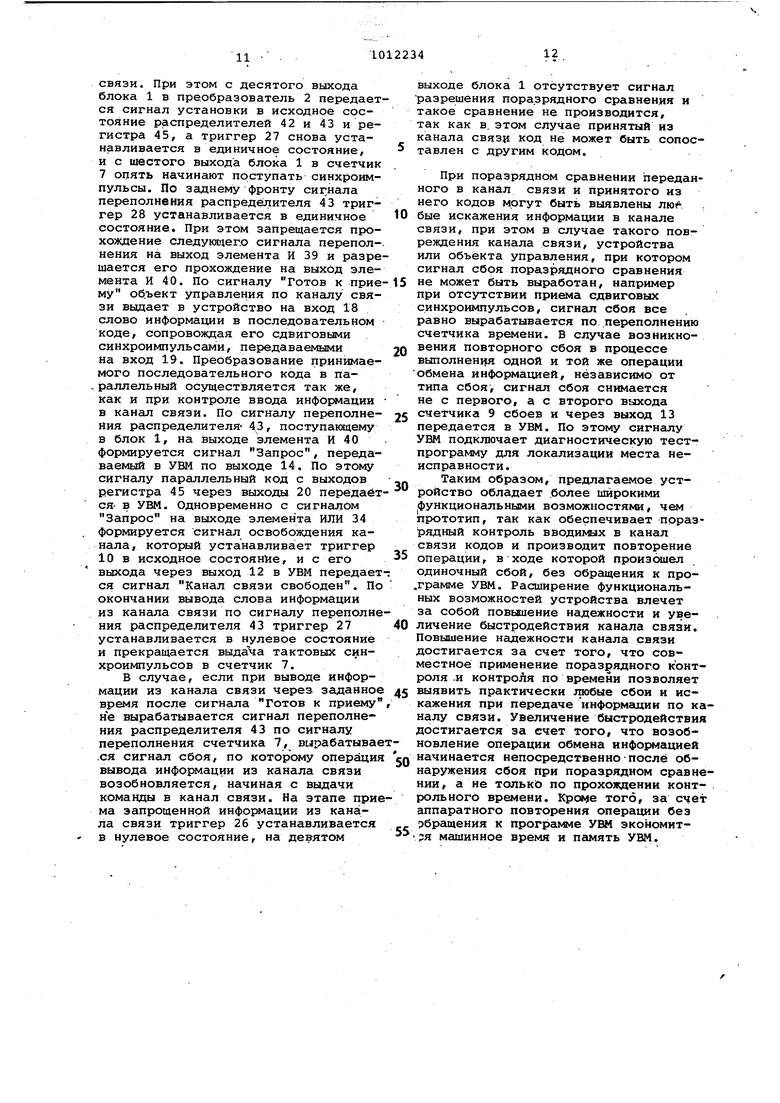

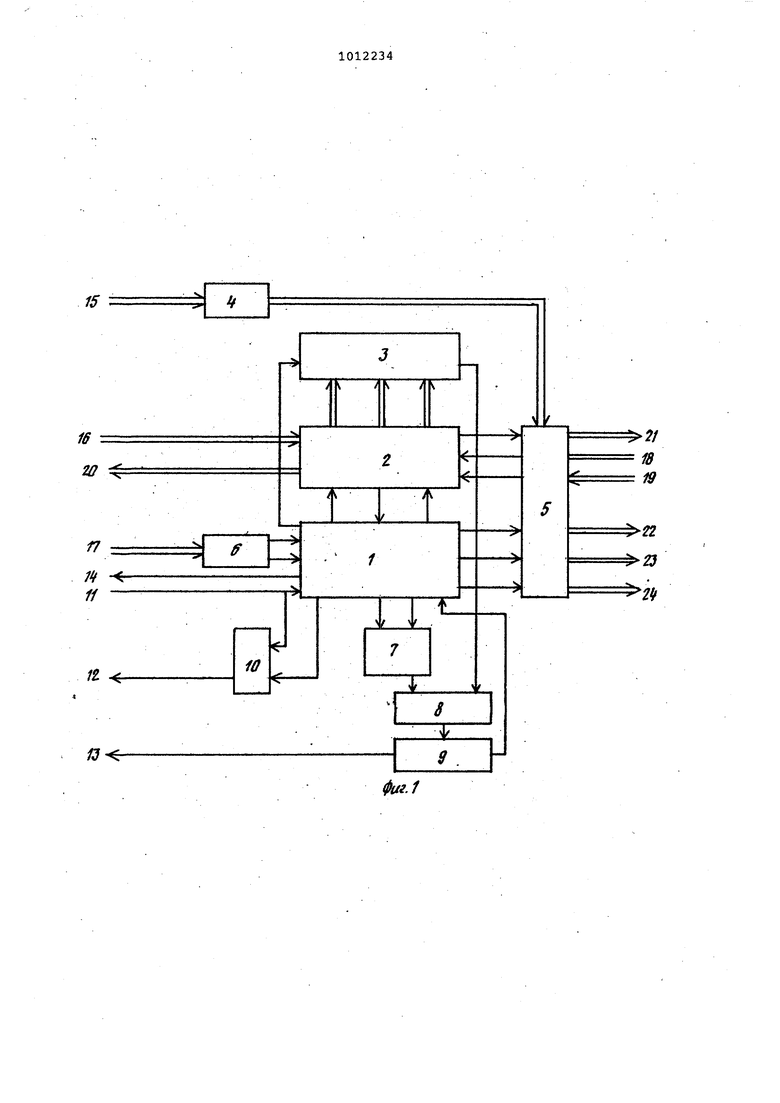

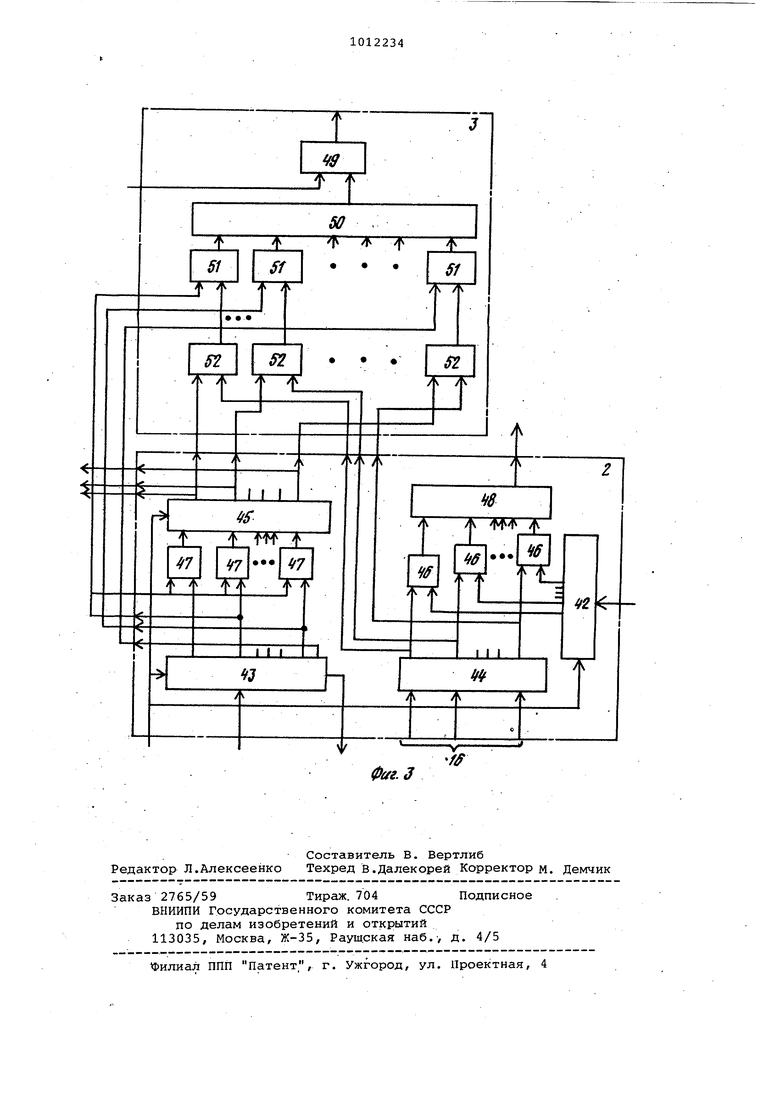

Известно-устройство для сопряжения вычислительной машины с объектами управления, содержащее регистры приема-передачи, управляющие регистры, счетчик, синхроимпульсов, блок; формирования управляющих сигналов С Недостатком данного устройства являются ограниченные функциональные возможности из-за отсутствия контроля процесса обмена информацией. Наиболее близким к предлагаемому по технической сущности является уст ройство для сопряжения вычислительной машины с каналами связи, содержащее коммутатор, первые вход и выход которого являются первыми входом и выходом устройства, а вторые вход и выход соответственно соединены непосредственно и через блок контроля с первыми выходом, и входом преобразователя кодов, вторые вход и выход которого через блок буферной памяти подключены к вторым входу и выходу устройства, первый выход блока управления соединен с адресным входом коммутатора, второй выход - через распределитель импульсов с адресным входом блока буферной памяти, а группа входов - с выходами элементов И группы, первые входы кот рых соединены с группой выходов регистра адреса, а вторые - с группой входов устройства и через регистр конца обмена с группой входов первого элемента ИЛИ, выход которого подключен к первым входам счетчика и второго элемента ИЛИ, выходом соединенного с первым входом триггера, а вторым входом - с третьим выходом устройства и выходом .счетчика, второй вход которого подключен к третьему входу устройства, а третий вход - к четвертому входу устройства и второму входу триггера, выходом соединенного с четвёртым выходом ус ройства, вход регистра адреса являе ся пятым входом устройства 2 3Недостатки этого устройства состоят в ограниченных функциональных возможностях и низкой достоверности работы. В этом устройстве используется контроль по модулю только те сообщений, которые выдаются в УВМ, причем отсутствует возможность возо новления операции обмена информацией , в процессе которой произошел сб без обращения к программе УВМ. Прим няемый в этом устройстве контроль процесса обмена информацией по времени обмена является ненадежным, не достаточно сильным, и в случае обна ружения сбоя устройство инициирует повторный обмен информацией путем .обращения к программе УВМ, что приводит к усложнению программ, нерациональному использованию машинного времени и снижению быстродействия к нала обмена информацией и всего упраБляющего комплекса в целом. Цель изобретения - расширение фу кциональных возможностей за счет анализа состояния обмена и автоматического возобновления операций обмена в случае обнаружения сбоев. Поставленная цель достигается тем, что в устройство, содержащее блок управления, преобразователь кодов, регистр адреса, коммутатор, счетчик времени, элемент ИЛИ и триггер, причем вход запуска устройства соединен с единичным входом триггера, выход которого соединен с выходом состояния устройства, выход счетчика времени соединен с. первым входом элемента ИЛИ, группа адресных входов устройства соединена с группой входов регистра адреса, первые выход и вход преобразователя кодов подключены соот,ветственно к первым входу коммутатора и выходу блока управления, второйчетвертый выходы которого соединены соответственно с вторым - четвертым входами коммутатора, первый выход преобразователя кодов соединен с первым входом коммутатора, первая - четвертая группы выходов которого соединены соответственно с первой группой информаю1ионных входов и первой, второй к третьей группами синхронизирукхцих выходов устройства, а первая и вторая группы входов - соответственно с первой информационной и синхронизирующей группами входов устройства, введены блок сравнения, счетчик сбоев и регистр признаков операций, причем группа выходов регистра адреса соединена с группой управляющих входов коммутатора, первый и второй выходы которого соединены соответственно с вторым и третьим входами преобразователя кодов, пятый и шестой выходы блока управления соединены соответственно с первым и вторым входами счетчика времени, первая - четвертая группы выходов преобразователя кодов соединены соответственно с второй информационной группой выходов устройства и с первой - третьей группами входов блока сравнения, выход которого соединен с вторым входом элемента ИЛИ, группа входов преобразователя кодов соединена с второй информационной группой входов устройства, группа входов.регистра признаков операций соединена с группой командных входов устройства, а первый и второй выходисоответственно с первом и вторым входами блока управления, третий, четвертый входы которого соединены соответственно с вторьам выходом преобразователя кодов и первьм выходом счетчика сбоев, выход элемента ИЛИ соединен с входом счетчика сбоев, второй выход которого соединен с выходом неисправности устройства, седьмой и восьмой выходы блока управления соединены соответственно с нулевым входом триггера и с выходом запроса устройства, а пятый вход - с входом запуска устройства, девятый и десятый выходы блока управления соединены соответственно с входом блока сра нения и четвертым входом преобразова теля кодов. Блок управления содержит генерато тактовых импульсов, узел синхронизации, три триггера, два элемента задержки, шесть элементов И и четыре элемента ИЛИ, причем первьай вход пер вого элемента ИЛИ соединен с пятым входом блока, второй вход - через первый элемент задержки с чeтвepты : входом блока и первым входом второго элемента ИЛИ, второй вход которого подключен к третьему входу блока, а выход - к нулевым входам первого и второго триггеров и пятому выходу блока, первый вход первого элемента И соединен с вторым входом блока, второй вход - с третьим входом блока и Первым входом второго элемента И, подключенным вторым входом к первому входу блока, выход генератора тактовых импульсов соединен с первыми вхо дами третьего и четвертого элементов И и узла синхронизации, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к второму выходу блока, единичному входу перво го триггера, нулевому входу третьего триггера и первому входу третьего элемента ИЛИ, выводом соединенного .с единичным входом второго триггера и десятым выходом блока, а вторым входом - с третьим выходом блока и выходом пятого элемента И, первый и второй входы которого соединены соответственно с нулевым выходом третьего триггера и с выходом первого элемента И и единичным входом третьего триггера, единичным выходом подключенного к первому входу шестого элемента И, в торой вход которо го соединен с третьим входом блока, а вьлход - с восьмым выходом блока и первым входом четвертого элемента ИЛИ, выход которого является седьмым выходом блока, а второй вход соединен с вьпсодом второго элемента И, выход второго триггера соединен с .вторьлм входом четвертого элемента И, выход которого является шестым выходом блока, выход первого триггера подключен к девятому вьисоду блока и к второму входу третьего элемента И, выход которого соединен с четвёртым выходом блока и через второй элемент задержки с первым выходом, блока. Преобразователь кода содержит два распределителя импульсов, два регистра, две группы элементов И и элемент ИЛИ, причем группа входов первого регистра соединена с группой входов преобразователя, первые входы распределителей импульсоз соединены с четвертым входом преобразователя и первым входом второго регистра, .группа выходов которого соединена с первой и третьей группами выходов преобразователя, вторые входы распределителей импульсов соединены соответственно с вторым и третьим входами преобразователя, а группы выходов - соответственно с первыми входами элементов И первой и второй групп, группа выходов второго распределителя импульсов Соединена с четвертой группой выходов преобразователя, а выход - с вторым выходом преобразователя, группа выходов первого регистра соединена с второй группой выходов преобразователя и вторыми входами элементов И первой группы, выходы, которых сбединены с группой входов элемента ИЛИ, выходом соединенного с первым входом преобразователя, группа входов второго регистра подключена к выходам элементов И второй группы, вторые входы которых соединены с вторым входом преобразователя. Блок сравнения содержит группу элементов равнозначности, группу элементов И, элемент И и элемент ИЛИ, причем первый и второй входы элементов равнозначности группы соединены соответственно с первой и второй группами входов блока, а выходы - с первыми входами соответствующих элементов И группы, вторые входда которых подключены к третьей группе .входов блока, а выходы - к группе входов элемента ИЛИ, соединен-, ного выходом с первым входом элемента И, второй вход и выход которого являются соответственно входом и выходом блока. Распределители импульсов представляют собой, например, последовательно соединенные счетчик и дешифратор. Наличие в преобразователе кодов двух независимых регистров и распределителей импульсов позволяет производить оДновременцр передачу кода в канал связи и прием кода из канала связи с целью контроля процесса обмена информацией. Кроме того, построение преобразователя параллельного кода в последовательный с использованием статического регистра, распределителя импульсов, группы схем И и схемы ИЛИ позволяет производить преобразование кодов без разрушения исходной информации, в отличие, например, от преобразователей построенных на регистрах сдвига. Это дает возможность организовать в устройстве аппаратное повторение операции без обращения к программе УВМ. Блок сравнения позволяет производить поразрядное сравнение переданного и принятого) из канала связи кодов и формировать .сигнал сбоя в случае отрицательного результата сравне ния. На фиг.1 представлена структурная схема устройства, на фиг.2 - функцио нальная схема блока управления, на фйг.З - функциональные схемы преобра зователя кодов и блока сравнения. . Устройство (фигЛ) содержит блок 1 управления, преобразователь 2 кодо . блок 3 сравнения, регистр 4 адреса, , коммутатор 5, регистр б признаков операций, счетчик 7 времени, элемент ИЛИ 8, счетчик 9 .сбоев, триггер 10, входы 11 устройства, выходы 12-14 устройства, входаа 15-19 первой, чет.вертой, пятой, второй и третьей груп входов, выходы- 20-24 пятой, первой, в,торой, третьей и четвертой групп выходов.. Ёлок 1 управления (фиг.2) содержит генератор 25 тактовых импульсов, триггеры 26-28, элементы 29 и 30 задержки, элементы ИЛИ 31-34, эле-менты И 35-40 и узел 41 синхронизации. Преобразователь 2 кодов (фиг.З) содержит распределители 42 и 43 .импульсов, регистры 44 и 45, элементы И 46 и 47 первой и -второй груп и элемент ИЛИ 48, а блок 3 сравнения элемент и 49, элемент ИЛИ 50, элементы И 51 группы и элементы равнозначности 52 группы. Распределитель 42 импульсов имеет разрядность, равную М, а распределитель 43 имеет М+2 разрядов, причем М+1 разрядов представлены как группа выходов распределителя 43. Из этой группы М первых разрядов соединены с первьши входами элементов И 47, разряды с второго по (М+1)-й соеди:--нены с четвертой группой выходов пре образователя 2 и с Вторыми входами -элементов И 51, число которых в груп пе равно М. ,В режиме ввода информации в объек управления по каналу связи устройств работает следующим образом. В исходном состоянии с выхода, три гера 10 через выход 12 в УВМ поступает сигнал Канал связи свободен. По этому сигналу УВМ начинает операц обмена информацией. Перед началом операции обмена по сигналу из УВМ все -элементы памяти устройства устанавливаются в исходное состояние.. По входам 15,16 и 17 в регистр 4, регистр 44 преобразователя 2 и в регистр 6 из УВМ записываются соответствующие коды. Код адреса с групп выходов регистра 4 поступает на коммутатор 5, при этом входы 18. и-19 и выходы 21-24 подключаются к выбра .ному каналу связи. С выхода регистр 6 на вход блока 1 поступает сигнал операции ввода информации в канал связи. С входа 11 на единичный вход триггера 10 и пятый вход блока 1 из УЩ поступает сигнал Запуск, по которому начинается процедура ввода информации в канал связи. При этом триггер 10 устанавливается в единичное состояние и с его. выхода и выхода 12 до окончания операции обмена информацией снимается сигнал Канал связи.-свободен. С пятого входа блока 1 сигнал Запуск через ИЛИ 31 поступает на вход узла 41, на первый аход которого поступают тактовые импульсы с генератора 25. При этом на выходе узла 41 присутствует сигнал Начало передачи, синхронизированный с тактовой Сеткой устройства, котоЕядй через коммутатор 5 -и выход 22 передается в канал связи. По этому же сигнсшу триггер 26 устанавливается в единичное состояние и с его единичного выхода разрешающий потенциал поступает на вход элемента И . 37, с выхода которого синхроимпульсы поступают на выход блока 1 управле - i ния и на вход элемента 30 задержки. С четвертого выхода блока 1 синхроимпульсы, сдвига через коммутатор 5 и выход 24 передаются ;в канал связи. 1C первого выхода блока 1 импульсы, задержанные относительно синхроимпульjcoB сдвига поступают на вход распределителя 42. Сигналы с группы выходов распределителя 42 на элементах И 36 последовательно стробируют сигналы с выходов регистра 44, и с выхода элемента ИЛИ 48 последовательный код через коммутатор 5 и выход 21 передается в канал связи. При этом каждый кодовый импульс на выходе 21 предворяется сдвиговым импульсом на выходе 24. Для контроля приема информации объектом управления из него через канал связи в устройство передается последовательный код, причем кодовые. и сдвиговые импульсы, поступающие соответственно на входы 18 и 19, задер живаются относительно передаваелвлх -кодовых и сдвиговых импульсов и могут быть несинхронизированными с такто;вой сеткой устройства. Последовательный код, принимаемый из кангша связи через коммутатор 5, поступает на .вторые входы элементов И 47, а сдвиговые синхроимпульсы - на второй вход распределителя 4-3. Сигналы с выходов распределителя 43 поступают на входал элементов И 47 и разрешают прохождение кодовых импульсов последовательно на входа регистра 45. При этом с выходов регистра 45 на первую и третью группы выходов преобразователя 2 передается параллельный, код, а после приема последнего сдвигового синхроимпульса из канала связи с. выхода распределителя 43 на вто.рой выход преобразователя 2 передается сигнал переполнения. С третьего входа -блока 1 сигнал переполнения распределителя 43 поступает на вход элемента и 36, на другой вход котор го через первый вход блока 1 из регистра б поступает разрешающий сигн операции ввода информации в канал связи. Далее сигнал переполнения ра пределителя 43 с выхода элемента И 36 передается на вход элемента ИЛИ 34, на выходе которого формируется сигнал освобождения канала связи. По этому сигналу, поступающему с вы хода блока 1, триггер 10, устанавли вается в нулевое состояние, и с его выхода через выход 12 устройства в УВМ опять поступает сигнал Канал связи свободен, что свидетельствуе об окончании операции обмена информацией. В устройстве производится контро процесса обмена информацией по врем ни. По сигналу Начало передачи триггер 27 устанавливается в единич ное состояние, и сигнал с его едини ного выхода разрешает прохождение через элемент И 38 синхроимпульсов на второй вход счетчика 7 времени. По окончании операции ввода информа ции в канал связи сигнал переполнен распределителя 43 с второго выхода преобразователя 2 через третий вход блока 1 поступает на второй вход элемента ИЛИ 32. По этому сигналу блок 1 производит установку в исходное состояние счетчика 7, а триггеры 26 и 27 устанавливаются в нулевое состояние. При этом прекращается выдача сдвиговых синхроимпульсов в ком мутатор 5 и выдача тактовых синхроимпульсов в счет-чик 7 времени. В слу чае, если за заданное время сигнал переполнения распределителя 43 не поступает формируется сигнал, переполнения счетчика 7, который через элемент ИЛИ 8. поступает на вход счет чика 9 сбоев. С первого выхода счетчика 9 сигнал одиночного сбоя поступает на вход элемента 29 задержки и на первый вход элемента ИЛИ 32. При этом устанавливаются в исходное состояние счетчик 7 и триггеры 26 и 27. Задержанный сигнал одиночногс сбоя с выхода элемента 29 задержки через элемент ИЛИ 31 поступает на второй вход узла 41. По нему формируется сигнал Начало передачи, устанавливаются в исходное состояние распределители 42 и 43 и регистр 45, и далее операция ввода информации в канал связи производится так же, как и по сигналу Запуск, посту пающему из УВМ.При этом информация для обмена сохраняется в первом регистре 44 с предыдущего цикла обмена в котором произошел сбой. Таким обра зом, в устройстве реализуется возобновление опе рации. обмена информацией по каналу связи в случае одиночного сбоя без обращения к программе УВМ. В устройстве в режиме ввода информации в канал связи осуществляется непрерывный поразрядный контроль переданных и принятых кодов. Для этого в блоке 3 на элементах равнозначности 52 поразрядно сравниваются коды, записанные в регистры 44 и 45.. Опрос результатов сравнения производится путем последовательного стробирования на элементах И 51 результатов сравнения в каждом разряде кода сигналами с выходов распределителя 43, причем опрос результата сравнения каждого разряда производится сигналом с выхода следующего разряда распределителя 43. Это необходимо для того, чтобы сравнение- каждого разряда кода производилось только после того, как заканчивается прео разо1зание этого разряда из параллельного кода в последовательный и из последовательного в параллельный. С единичного плеча триггера 26 на вход элемента И 49 поступает сигнал, разрешающий прохождение сигнала сбоя поразрядного сравнения. В случае отрицательного результата сравнения в каком-либо разряде кода сигнал сбоя поразрядного сравнения с выхода блока 3 через элемент ИЛИ 8 поступает на вход счетчика 9 и вызывает повторение операции ввода информации в канал связи так же, как и в случае сбоя по времени обмена. Ё режиме вывода информации из канала связи устройство работает следующим образом. Передача по каналу связи команды на вывод информации с объекта управления осуществляется так же, как и -в режиме ввода информации. При этом осуществляется поразрядный контроль передачи команды и контроль по времени обмена. По окончании передачи команды в канал связи, как и в режиме ввода информации, по сигналу переполнения распределителя 43 триггеры 26 и 27 устанавливаются в нулевое состояние, блок 1 формирует сигнал установки в исходное состояние счетчика 7 времени и прекращает выдачу синхроимпульсов в счетчик 7. Однако при этом с выхода регистра б сигнал соответствукицего признака операции поступает не на первый, а на второй вход блока 1 управления. то приводит к тому, что по окончании передачи команды в канал связи и ее поразрядного контроля по сигналу переполнения распределителя 43 на элементах И 36 и ИЛИ 34 не формируется сигнал освобождения канала, а на выходе элемента И 39 формируется сигнал Готов к приему, который ерез третий выход блока 1, коммутатор 5 и выход 23 передается в канал связи, при этом с десятого выхода блока 1 в преобразователь 2 передает ся сигнал установки в исходное состояние распределителей 42 и 43 и регистра 45, а триггер 27 снова устанавливается в единичное состояние, и с шестого выхода блока 1 в счетчик 7 опять начинают поступать синхроимпульсы. По заднему фронту переполнения распределителя 43 триггер 28 устанавливается в единичное состояние При этом запрещается прохоящение следующего сигнала переполнения на выход элемента И 39 и разре шается его прохождение на выход элемента И 40. По сигналу Готов к прие му объект управления по каналу связи вьщает в устройство на вход 18 слово информации в последовательном коде, сопровождая его сдвиговыми синхроимпульсами, передаваемыми на вход 19. Преобразование принимаемого последовательного кода в па.раллельный осуществляется так же, как и при контроле ввода информации в канал связи. По сигналу переполнения распределителя- 4,3, поступакнцему в блок 1, на выходе элемента И 40 формируется сигнал Запрос, передаваемый в УВМ по выходе 14. По этому сигналу параллельный код с выходов регистра 45 через выходы 20 передаёт ся- в УВМ. Одновременно с сигналом Запрос на выходе элемента ИЛИ 34 формируется сигнал освобождения канала, который устанавлива1ет триггер 10 в исходное состояние, и с его выхода через выход 12 в УВМ передает ся сигнал Канал связи свободен. По окончании вывода слова информации из канала связи по сигналу переполне ния распределителя 43 триггер 27 устанавливается в нулевое состояние и прекращается выдала тактовых синхроимпульсов в счетчик 7. В случае, если при выводе информации из канала связи через заданное время после сигнала Готов к приему не вырабатывается сигнал переполнения распределителя 43 по сигналу переполнения счетчика 7, вирабатыва ,ся сигнал сбоя, по которому операци вывода информации из канала связи возобновляется, начиная с выдачи команды в канал связи. На этапе при ма запрошенной информации из канала связи триггер 26 устанавливается в нулевое состояние, на выходе блока 1 отсутствует сигнал разрешения поразрядного сравнения и такое сравнение не производится, так как в. этом случае принятый из канала связи код не может быть сопоставлен с другим кодом. При поразрядном сравнении переданного в канал связи и принятого из него кодов могут быть выявлены . , бые искажения информации в канале связи, при этом в случае такого повреждения канала связи, устройства или объекта управления, при котором сигнал сбоя поразрядного сравнения не может быть выработан, например при отсутствии приема сдвиговых синхроимпульсов, сигнал сбоя все равно вырабатывается по. переполнению счетчика времени. В случае возникновения повторного сбоя в процессе выполнения одной и той же операции обмена информацией, независимо от типа сбоя, сигнал сбоя снимается не с первого, а с второго выхода счетчика 9 сбоев и через выход 13 передается в УВМ. По этому сигналу УВМ подключает диагностическую тестпрограмму для локализации места неисправности. Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями, чем прототип, так как обеспечивает поразрядный контроль вводимых в канал связи кодов и производит повторение операции, в ходе которой произошел одиночный сбой, без обргицения к про.грамме УВМ. Расширение функциональных возможностей устройства влечет за собой повышение надежности и увеличение быстродействия канала связи. Повышение надежности канала связи достигается за счет того, что совместное применение поразрядного контроля .и контроля по времени позволяет выявить практически любые сбои и искажения при передаче информации по каналу связи. Увеличение быстродействия достигается за счет того, что возобновление операции обмена информацией начинается непосредственно после обнаружения сбоя при поразрядном сравнении, а не только по прохождении контрольного времени. Кроме того, за счет аппаратного повторения операции без рбращения к nporpaNwe УВМ экономит ря машинное время и память УВМ.

fff

фе/г.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения вычисли-ТЕльНОй МАшиНы C Об'ЕКТАМи упРАВлЕНия | 1979 |

|

SU798784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1977 |

|

SU703799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-10—Подача