кодирования адресов каналов, выходом элемента И и дополнительным выходом синхронизатора, а выходы буферного запоминающего блока подключены к дополнительным входам блока памяти и элемента ИЛИ, причем первый вход блока сравнения соединен с дополнительным выходом блока кодирования адресов каналов, входом регистра адреса и первым входом элемента И, второй вход которого соединен с вторым входом блока формирования подряд идущих каналов и выходом элемента НЕ, к входу которого подключен выход блока сравнения, второй вход которого соединен с выходом регистра адреса..

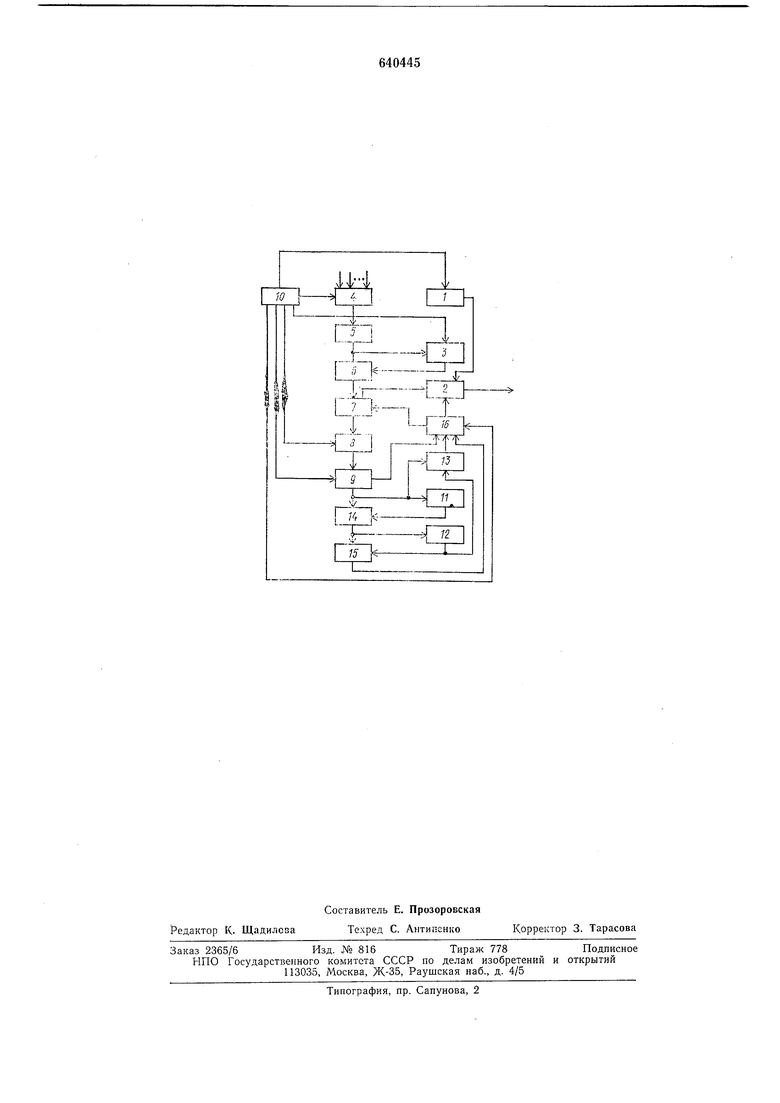

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для многоканальной передачи информации содерЖИт блок кодирования времени 1, элемент ИЛИ 2, многоканальный блок памяти 3 и последовательно соединенные коммутатор каналов 4, блок кодирования измер.ительной информации 5, анализатор сигналов 6, блок памяти 7, блок анализа пар корреляционных моментов 8 и блок кодирования адресов каналов

9,а также синхроивзатор 10, выходы которого подключены соответственно к синхровизирующим входам коммутатора каналов

4, многоканального блока памяти 3, блока анализа пар корреляционных моментов 8, блока кодирования адресов каналов 9 и блока кодирования времени 1, выход которого подключен к первому входу элемента ИЛИ 2, второй вход которого соединен с вторым выходом блока памяти 7, при этом выход блока кодирования измерительной информации 5 подключен к входу многоканального блока памяти 3, выход которого соединен со вторым входом анализатора сигналов 6, регистр адреса 11, элемент НЕ 12, элемент И 13 и последовательно соединенные блок сравнения 14, блок формирования числа подряд идущих каналов 15 и буферный запоминающий блок 16, дополнительные входы которого соединены соответственно с выходом блока кодирования адресов каналов 9, выходом элемента И 13 и дополнительным выходом синхронизатора

10,а выходы буферного запоминающего блока 16 подключены к дополнительным входам блока памяти 7 и элемента ИЛИ 2, причем первый вход блока ср авнения 14 соединен с дополнительным выходом блока кодирования адресов каналов 9, входом регистра адреса 11 и первым входом элемента И 13, второй вход которого соединен с вторым входом блока формирования числа подряд идущих каналов 15 и выходом элемента НЕ 12, к входу которого подключен выход блока сравнения 14, второй вход которого соединен с выходом регистр а адреса 11.

Устройство работает следующим образом.

Сигналы синхронизатора 10 управляют работой коммутатора каналов 4, с помощью которого на вход блока кодирования измерительной информации 5 поочередно поступают сигналы всех каналов. Блок кодирования измерительной информации 5 в соответствии с амплитудой входного сигнала вырабатывает кодовую комбинацию в виде параллельного двоичного кода. Кодовые комбинации подаются на входы анализатора сигналов 6 и многоканального блока намяти 3. С выхода многоканального блока памяти 3 одновременно снимается кодовая комбинация, отображающая значение сигнала данного канала в точке отсчета, предшествующей рассматриваемой и отстоящей на время, равное длительности периода дискретизации. В анализаторе сигналов 6 производится сравнение t-ro и (i-1)-го значений отсчетов, выраженных в ВИде кодовых комбинаций. Если абсолютная величина разности двух значений меньше шага квантования, то анализатор сигналов 6 не пропускает текущую кодовую комбинацию на вход блока памяти 7 информационных кодов.

Если же разность превышает по абсолютной величине шаг квантования, то текущая кодовая комбиеаЦия передается в блок памяти 7. После завершения анализа выборок канала с выхода синхронизатора 10 в блок анализа пар корреляционных моментов 8 поступает сигнал на разрешение выдачи результатов сравнения кодовых комбинаций сигналов между комбинация.ми пар каналов из Л. В каждом периоде дискретизации в начале сравниваются возможные кодовые комбинация 1-го канала со всеми комбинациями остальных каналов. При наличии данной кодовой комбинации 1-го канала в других любых каналах с блока анализа пар корреляционных моментов 8 в блок кодирования адресов каналов 9 последовательно выдаются сигналы для формирования кодов адресов каналов, которым принадлежит данная кодовая комбинация информационного калала. С выхода блока кодирования адресов каналов 9 код адреса f-ro канала поступает одновременно в блок сравнения 14 и регистр адреса И. В этот же момент времени с выхода регистра адреса И на второй вход блока сравнения 14 поступает код адреса (i-1)-го или (i-k}-ro каналов, где и . При этом блок сравнения 14 выдает сигнал сравнения только в том случае, когда текущий адрес канала, поступивший на ее первый вход с блока кодирования адресов каналов 9, больше на единицу предыдущего адреса, поступающего на второй вход с выхода регистра адреса 11. Сигнал сравнения с выхода блока сравнения 14 подается одновременно на блок формирования числа

подряд идущих каналов 15 и на элемент НЕ 12. Если на вход блока сравнения 14 под воздействием управляющих сигналов синхронизатора 10 продолжают поступать коды адресов каналов, отличающиеся друг от друга на единицу, то на выходе элемента НЕ 12 и блока форМированИЯ числа подряд идущих каналов 15 сигналы отсутствуют. Таким образом, при таком состоянии элемент И 13 оказывается закрытым по управляющему входу, и код текущего адреса канала с его выхода в буферный заломянающий блок 16 также не поступает. В случае поступления в блок сравнения 14 кода адреса (t-k)-To канала на выходе элемента НЕ 12 появляется управляющий сигнал, который дает разрещение на запись кода подряд прошедших каналов из элемента НЕ 12 в буферный запоминающий блок 16 и разрешает прохождение через элемент И 13 кода текущего адреса канала, отличающегося от предыдущего более чем на единицу. После того как в буферный запоминающий блок 16 будут записаны коды адресов каналов, а также коды подряд прощедших каналов с одинаковыми уровнями кв-антования, блок кодирования адресов каналов 9 дает разрешение на выдачу их из буферного запоминающего блока 16 через элемент ИЛИ 2 на выход всего устройства. Тактирование буферного запоминающего блока 16 осуществляется управляющими сигналами синхронизатора 10. Как только на выход устройства будет выдай последний код адреса канала группы, буферный запоминающий блок 16 формирует управляющий сигнал на выдачу со второго выхода блока памяти 7 информационной кодовой комбинации, принадлежащей данной группе номеров каналов, которая через элемент ИЛИ 2 также поступает на выход всего устройства. В начале каждого кадра передачи информации под воздействием сигнала синхронизатора с блока кодирования времени

1на выход устройства через элемент ИЛИ

2подается кодовая комбинация текущего времени.

Иопользован1ие предложенного устройства дает возможность уменьшить размер кадров передачи информации, это достигается за счет замены группы кодов адресов подряд идущих каналов.

Уменьшение размера кадра позволяет более эффективно использовать канал связи, уменьшать время на передачу информации по каналам или за то же исходное время передать информацию от дополнительных источников, что выгодно отличаст нредложенное устройство от прототипа.

Формула и 3 о б р е т е и и я

Устройство ДЛЯ многоканальной передачи информации, содерлхащсе блок кодирования времени, элемент ИЛИ, многоканальный блок памяти и последовательно соединенные коммутатор каналов, блок кодирования измерительной информации, анализатор сигналов, блок памяти, блок анализа иар корреляционных моментов и блок кодирования адресов каиалов, а также синхронизатор, выходы которого подключены соответственно к синхронизирующим входам коммутатора каналов, многоканального блока памяти, блока анализа пар корреляционных моментов, блока кодирования адресов каналов и блока кодирования времени, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с вторым выходом блока памяти, при этом выход блока кодирования измерительной информации подключен к входу многоканального блока памяти, выход которого соединен с вторым входом анализатора сигналов, отличающееся тем, что, с целью сокращения избыточности а1дрес юй цнформации, в него введены регистр адреса, элемент НЕ, элемент И и последовательно соединенные блок сравнения, блок формирования числа подряд идущ их каналов и буферный запоминающий блок, дополнительные входы которого соединены соответственно с выходом блока кодирования адресов каналов, выходом элемента И и дополнительным выходом синхронизатора, а выходы буферного заноминаю1цего блока подключены к дополнительным входам блока памяти н элемента ИЛИ, причем первый вход блока сравнения соединен с дополнительным выходом блока кодирования адресов каналов, входом регистра адреса и первым входом элемента И, второй вход которого соединен с вторым входом блока формирования числа подряд идущих каналов и выходом элемента НЕ, к входу которого подключен выход блока сравнения, второй вход которого соединен с выходом регистра адреса.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 402053, кл. G 08С 19/28, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1977 |

|

SU646366A1 |

| Устройство для обработки и передачи информации | 1977 |

|

SU640352A1 |

| Устройство для передачи телеметрической информации | 1978 |

|

SU734787A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU458851A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1145357A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Устройство для сжатия и передачи телеметрической информации | 1983 |

|

SU1153336A1 |

| Устройство для уплотнения многоканальных сообщений с кодо-импульсной модуляцией | 1977 |

|

SU619944A1 |

| Устройство для уплотнения многоканальных сообщений с кодоимпульсной модуляцией | 1986 |

|

SU1365106A1 |

| Многоканальное устройство для передачи информации с дельта-модуляцией | 1982 |

|

SU1166330A1 |

Авторы

Даты

1978-12-30—Публикация

1976-10-11—Подача