элементов И N каналов подключен нулевой выход триггера управления, а к вторым входам вычитающих блоков N каналов подключен выход генератора пилообразного напряжения, дополнительные выходы синхронизатора подключены соответственно к управляющим входам генератора пилообразного напряжения, анализатора, третьего элемента ИЛИ и к первому управляющему входу первого дополнительного регистра сдвига, а управляющий вход счетчика объединен с соответствующими управляющими входами триггера управления, регистра сдвига, первого дополнительного регистра сдвига, второго дополнительного регистра сдвига, дополнительного блока памяти, формирователя адресов и блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство дляпЕРЕдАчи иНфОРМАции C дЕльТА- МОдуляциЕй | 1979 |

|

SU849271A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Ультразвуковой дефектоскоп | 1988 |

|

SU1627974A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1104571A1 |

| Многоканальное устройство для передачи сигналов приращений | 1982 |

|

SU1103276A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Электронный коммутатор | 1988 |

|

SU1626444A1 |

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ, содержащее N каналов, в состав каждого из которых входят вычитающий . блок, первый вход которого является входом канала, объединенные по одному из входов первый и второй элементы И и третий элемент И, а также элементы ИЛИ, элемент задержки и синхронизатор, выходы которого подключены соответственно к управляющим входам блока памяти, счетчика, формирователя адресов и регистра сдвига, отличающееся тем, что, с целью упрощения устройства путем исключения двоичного модулятора, а из каждого канала - троичного модулятора, в него введены 2 N одновибраторов, дополнительные регистры сдвига, анализатор, дополнительные элементы И, генератор пилообразного напряжения, триггер управления, дополнительные элемент задержки и блок памяти, при этом в каждом из N каналов выход вычитающего блока подключен к объединенным входам первого и второго элементов И, выходы которых подключены соответственно к входам первого и второго одновибраторов, инверсные выходы первого и второго одновибраторов подключены к входам третьего элемента И, а прямые выходык входам первого дополнительного элемента И, выходы третьего элемента И и первого дополнительного элемента И подключены к соответствующим входам регистра сдвига, выход которого подключен к входу первого дополнительного регистра сдвига, выход которого подключен к одному из входов счетчика и к первому входу первого элемента ИЛИ, выход которого через элемент задержки подключен к соответствующим входам второго дополнительного регистра сдвига и счетчика, один из выходов которого подключен к первому входу второго элемента ИЛИ, к второму входу которого подключен второй выход анализатора, выход второго элемента ИЛИ подключен к первым входам второго, третьего . и четвертого дополнительных элементов И и через последовательно соединенные дополнительный элемент задержки и третий S элемент ИЛИ подключен к соответствующему входу счетчика, к второму входу первого элемента ИЛИ и к первому входу пятого дополнительного элемента И, выход которого подключен к соответствующему входу второго дополнительного регистра сдвига, выход которого подключен к второму входу анализатора и к второму входу третьего дополнительного элемента И, Другой выход первого дополнительного реО5 гистра сдвига подключен к второму входу О5 пятого дополнительного элемента И, выход СО 00 формирователя адресов подключен к второму входу четвертого дополнительного элемента И и к входу дополнительного блока памяти, выходы которого подключены к соответствующим объединенным входам второго дополнительного регистра сдвига и счетчика, соответствующий выход которого подключен к второму входу второго дополнительного элемента И, выходы второго, третьего и четвертого дополнительных элементов И подключены к соответствующим входам блока памяти, выход которого является выходом устройства, причем к другим входам первых элементов И N каналов подключен единичный выход триггера управления, к другим входам вторых

1

Изобретение относится к технике связи и может использоваться в системах телеметрии, телефонии, автоматизированных системах контроля и управления.

Известно многоканальное устройство для передачи информации с разпостнодискретной модуляцией, содержащее синхронизатор, двоичный модулятор и в каждом из N каналов вычитающий блок, один из входов которого является канальным входом устройства, к второму входу подключен первый выход синхронизатора, третий вход соединен с выходом интегратора, троичный модулятор, первый вход которого соединен с выходом вычитающего блока, второй вход - с вторым выходом синхронизатора, а выход троичного модулятора подключен к входу интегратора и через дополнительно введенные блок памяти, два параллельно включенных элемента И элемент ИЛИ - к соответствующему входу формирователя адресов каналов, первый выход которого соединен через блок суммирования с выходом устройства, второй и третий выходы подключены к входам двоичного модулятора, выход которого подключен к второму входу блока суммирования, причем третий выход формирователя адресов каналов, кроме того, соединен с вторым входом одного из канальных элементов И, а второй вход второго канального элемента И соединен с третьим выходом синхронизатора, кроме того, второй и третий выходы синхронизатора соединены с (N + 1) и (N + 2)-M входами формирователя адресов каналов 1.

Данное устройство позволяет производить кодирование многомерных сигналов, но при этом имеет место малая степень уплотнения информации.

Наиболее близким техническим рещением к изобретению является многоканальное устройство для передачи информации с дельта модуляцией, содержащее N каналов, в состав каждого из которых входят вычитающий блок, первый вход которого является входом канала, объединенные по одному из входов первый и второй элементы И и третий элемент И, а также элементы ИЛИ, элемент задержки и синхронизатор, выходы которого подключены соответственно к управляющим входам блока памяти, счетчика, формирователя адресов и регистра сдвига, при этом выходы первого и второго элементов И каждого канала подключены к входам элемента ИЛИ, а выход вычитающего блока подключен к

Q одному из входов троичного модулятора, выход которого через интегратор подключен к второму входу вычитающего блока, а также сумматор и двоичный модулятор, выход которого подключен к первому входу сумматора, к второму входу которого подключен первый выход формирователя адресов, второй и третий выходы которого подключены к соответствующим входам двоичного модулятора, причем второй выход формирователя адресов подключен к первому входу первого элемента И каждого

из N каналов, второй вход которого и первый вход второго элемента И соединены с соответствующими выходами блока памяти, к входам которого подключены выходы троичных модуляторов соответствующих

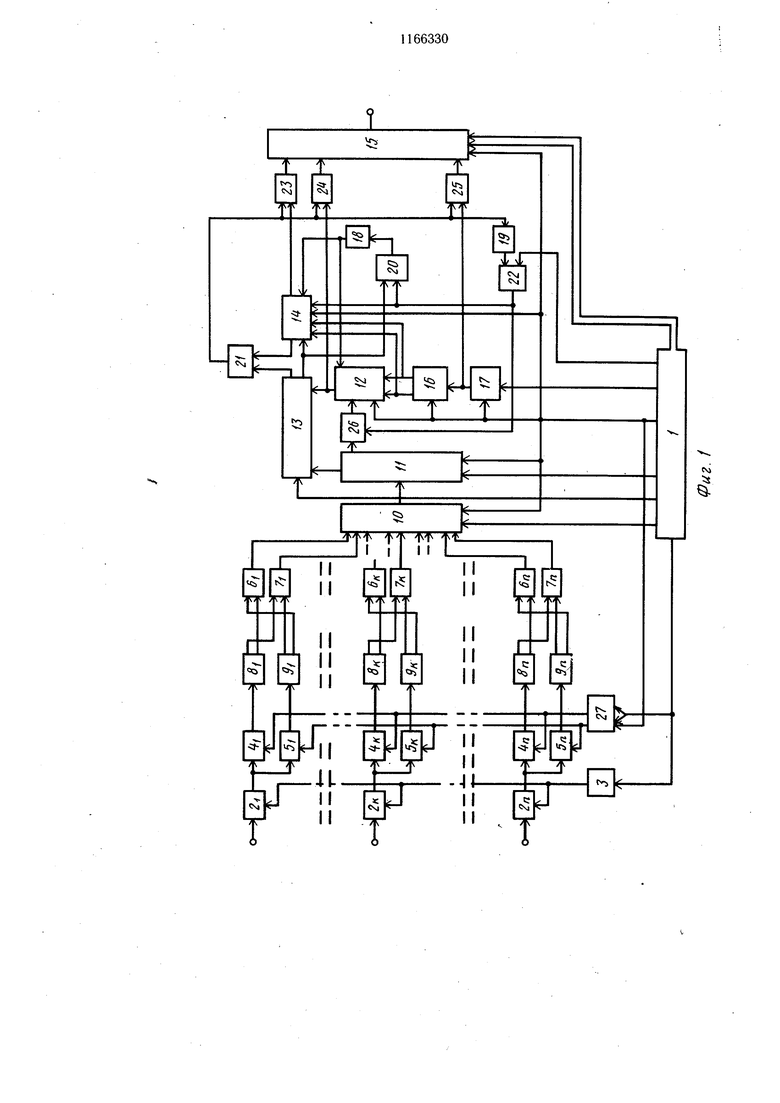

5 каналов, первый выход синхронизатора подключен к другому входу .вычитающего блока каждого из N каналов и к дополнительному входу блока памяти, второй выход синхронизатора подключен к другому входу троичного модулятора каждого из N каналов и к первому дополнительному входу формирователя адресов, второй дополнительный вход которого соединен с третьим выходом синхронизатора, соединенным с другим входои второго элемента И каждого из N каналов, последовательно соединенные элемент НЕТ, элемент НЕ и третий элемент И, в каждом из N каналов, кроме первого, один из входов элемента НЕТ и другой вход третьего элемента И подключены к выходу элемента ИЛИ, выход каждого из элементов НЕТ и выход элемента ИЛИ первого канала подключены к соответствующим входам формирователя адресов, другой вход элемента НЕТ каждого из N-1 каналов подключен к выходу элемента ИЛИ предыдущего канала, выходы третьих элементов И каждого из N-1 каналов подключены к соответствующим входам регистра сдвига к дополнительному . входу которого подключен четвертый выход синхронизатора, выход блока формирования кода числа каналов подключен к третьему входу сумматора, к четвертому входу которого подключен первый выход синхронизатора через блок формирования маркера кадра, выход регистра сдвига через последовательно соединенные дополнительный элемент НЕ и элемент задержки подключен к второму входу счетчика, к третьему входу которого и к входу синхронизатора подключен выход дополнительного элемента НЕ 2. Известное устройство содержит в каждом из N каналов троичный модулятор, а также двоичный модулятор, что усложняет многоканальное устройство для передачи информации с дельта-модуляцией. Цель изобретения - упрощение устройства путем исключения двоичного модулятора, а из каждого канала - троичного модулятора. Цель достигается тем, что в многоканальное устройство для передачи информации с дельта-модуляцией, содержащее N каналов, в состав каждого из которых входят вычитающий блок, первый вход которого является входом канала, объединенные по одному,из входов первый и второй элементы И и третий элемент И, а также элементы ИЛИ, элемент задержки и син-, хронизатор, выходы которого подключены соответственно к управляющим входам блока памяти, счетчика, формирователя адресов и регистра сдвига, введены 2N одновибраторов, дополнительные регистры сдвига, анализатор, дополнительные элементы И, генератор пилообразного напряжения, триггер управления, дополнительные элемент задержки и блок памяти, при этом в каждом из N каналов выход вычитающего блока подключен к объединенным входам первого и второго элементов И, выходы которых подключены соответственно к входам первого и второго одновибраторов, инверсные выходы первого и второго одновибраторов подключены к входам третьего элемента И, а прямые выходы - к входам первого дополнительного элемента И, выходы третьего элемента И и первого дополнительного элемента И подключены к соответствующим входам регистра сдвига, выход которого подключен к входу первого дополнительного регистра сдвига, выход которого подключен к первому входу анализатора, первый выход которого подключен к одному из входов счетчика и к первому входу первого элемента ИЛИ, выход которого через элемент задержки подключен к соответствующим входам второго дополнительного регистра сдвига и счетчика, один из выходов которого подключен к первому входу второго элемента ИЛИ, к второму входу которого подключен второй выход анализатора, выход второго элемента ИЛИ подключен к первым входам второго, третьего и четвертого дополнительных элементов И и через последовательно соединенные дополнительный элемент задержки и третий элемент ИЛИ подключен к соответствующему входу счетчика, к второму входу первого элемента ИЛИ и к первому входу пятого дополнительного элемента И, выход которого подключен к соответствующему входу второго дополнительного регистра сдвига, выход которого подключен к второму входу анализатора и к второму вхо-. ду третьего дополнительного элемента И, другой выход первого дополнительного регистра сдвига подключен к второму входу пятого дополнительного элемента И, выход формирователя адресов подключен к второму входу четвертого дополнительного элемента И и к входу дополнительного блока памяти, выходы которого подключены к соответствующим объединенным входам второго дополнительного регистра сдвига и счетчика, соответствующий выход которого подключен к второму входу второго дополнительного элемента И, выходы второго, третьего и четвертого дополнительных элементов И подключены к соответствующим входам блока памяти, выход которого является выходом устройства, причем к другим входам первых элементов И N каналов подключен единичный выход триггера управления, к другим входам вторых элементов И N каналов подключен нулевой выход триггера управления, а к вторым входам вычитающих блоков N каналов подключен выход генератора пилообразного напряжения, дополнительные выходы синхронизатора подключены соответственно к управляющим входам генератора пилообразного напряжения, анализатора, третьего элемента ИЛИ и к первому управляющему входу первого дополнительного регистра сдвига, а управляющий вход счетчика объединен с соответствующими управляющими входами триггера управления, регистра сдвига, первого дополниительного регистра сдвига, второго дополнительного регистра сдвига, дополнительного блока памяти, формирователя адресов и блока памяти. На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие его работу. Многоканальное устройство для передачи информации с дельта-модуляцией содержит синхронизатор 1, вычитающие блоки 2j-2и, генератор 3 пилообразного

напряжения, первые элементы И , вторые элементы И 5j-5, третьи элементы И , первые дополнительные элементы И 7i -7й , первые одновибраторы 8i-8ft, вторые одновибраторы 9j.-9« , регистр 10 сдвига, первый 11 и второй 12 дополнительные регистры сдвига, анализатор 13, счетчик 14, блок 15 памяти, дополнительный блок 16 памяти, формирователь 17 адресов, элемент 18 задержки, дополнительный элемент 19 задержки, первый 20, второй 21 и третий 22 элементы ИЛИ, второй 23, третий 24, четвёртый 25 и пятый 26 дополнительные элементы И и триггер 27 управления.

Предложенное устройство работает следующим образом.

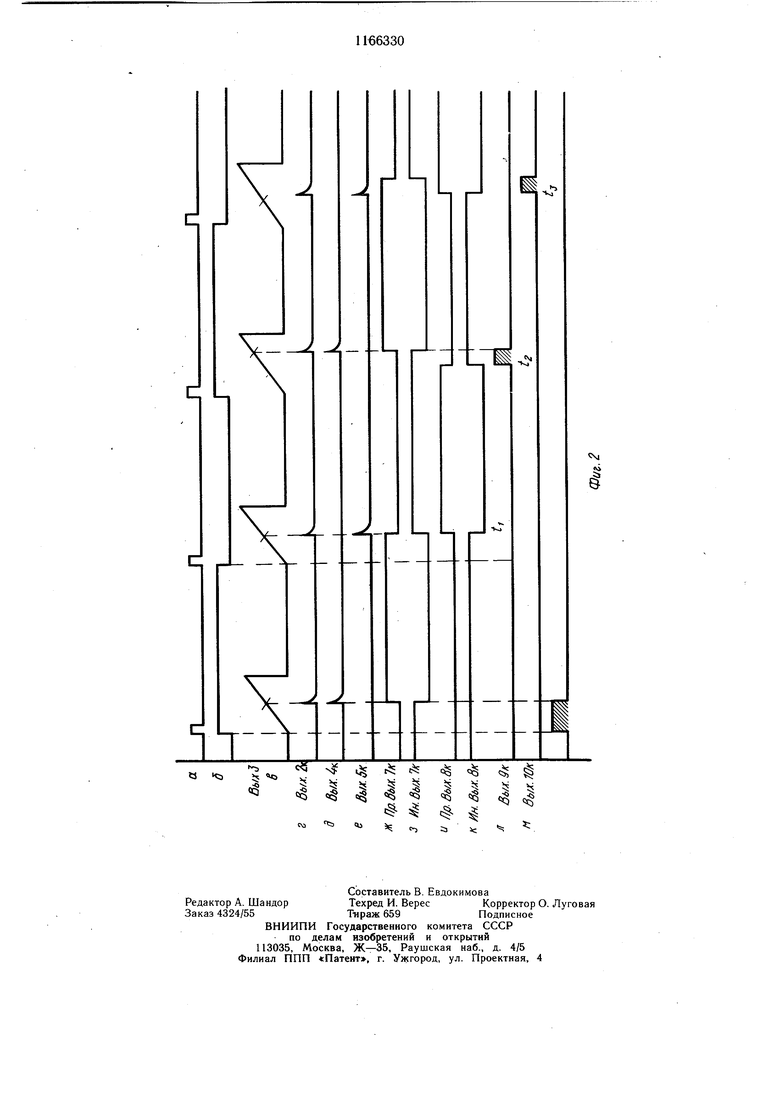

В начале работы сигналом с соответствующего выхода синхронизатора 1 устанавливаются в исходное состояние триггер 27 управления, регистр 10 сдвига,, первый 11 и второй 12 дополнительные регистры сдвига, счетчик 14, блок 15 памяти, дополнительный блок 16 памяти и формирователь 17 адресов. При пуске устройства синхронизатор 1 формирует сигнал (фиг. 2а), который запускает генератор 3, триггер 27 управления устанавливается в единичное состояние (фиг. 26) и открываются первые элементы И ,. Во всех каналах на вычитающих блоках 2 -2 параллельно сравниваются аналоговые сигналы, поступающие на первые входы вычитающих блоков 2i-2 и соответствующих каналов с пилообразным напряжением с выхода генератора 3 (фиг. 2в), поступающим на вторые входы вычитающих блоков . Для к-го канала в момент равенства аналогового, сигнала с пилообразным напряжением на выходе вычитающего блока 2jj к-го канала вырабатывается сигнал (фиг. 2г), который поступает на первые входы первого и второго элементов И 4 и 5 . Так как триггер управления находится в единичном состоянии и открыт первый элемент И 4 , то на его выходе формируется сигнал (фиг. 2 д), который запускает первый одновибратор 8 , на прямом выходе которого формируется потенциал положительной полярности (фиг. 2ж), а на инверсном выходе - потенциал отрицательной полярности (фиг. 2з). Время задержки первых и вторых одновибраторов , и 9i-9и. одинаково и равно щагу дискретизации по времени. Поэтому на каждом из них сигналы запоминаются на один такт преобразования. Параллельно с этим в начале первого такта преобразования сигнал с соответствующего выхода синхронизатора 1 записывает единицу на формирователе 17 адресов, т. е. формирует адрес первого канала. По этому адресу из дополнительного блока 16 памяти на второй дополнительный регистр

12 сдвига и счетчик 14 поступает нулевая информация, так как в начале работы устройства дополнительный блок 16 памяти обнулен. После этого сигнал с соответствую5 щего выхода синхронизатора 1 через третий элемент ИЛИ 22 и пятый дополнительный элемент И 26 осуществляет перезапись содержимого двух старщих разрядов с первого дополнительного регистра 11 сдвига на второй дополнительный регистр 12 сдви0 га, а в счетчик 14 записывается единица. Далее .этот сигнал через первый элемент ИЛИ 20, задерживаясь на элементе 18 задержки, записывает содержимое второго дополнительного регистра 12 сдвига и счет, чика 14 в дополнительный блок 16 памяти в адрес, соответствующий первому каналу. Затем сигнал с другого выхода синхронизатора 1 сдвигает содержимое первого дополнительного регистра 11 сдвига на два разряда. После этого с синхронизатора 1 0 на формирователь 17 адресов поступает сигнал, увеличивая его содержимое на единицу, и аналогично описанному происходит запись содержимого второго дополнительного регистра 12 сдвига и счетчика 14 в дополнительный блок 16 памяти в адрес, соответствующий второму каналу. Наконец содержимое второго дополнительного регистра 12 сдвига и счетчика 14 записывают в дополнительный блок 16 памяти в адрес, соответствующий N-му каналу. Q В следующем втором такте преобразования сигнал с выхода синхронизатора 1, поступая на счетный вход триггера 27 управления, устанавливает его в нулевое положение, при этом запираются первые элементы И 4i-4ц, открываются вторые 5 элементы И 5 -5 и запускается генератор 3. Аналогично описанному в момент равенства аналогового сигнала к-го канала с пилообразным напряжением на выходе вычитающего блока 2j к-го канала формируется сигнал, который через второй эле мент И 5jj (фиг. 2е) запускает второй одновибратор 9j , на прямом выходе которого формируется потенциал положительной полярности (фиг. 2ы), на инверсном выходе - потенциал отрицательной поляр5 ности (фиг. 2/с). Инверсные выходы первого и второго одновибраторов 8 и 9 поступают на входы третьего элемента И 6, а прямые выходы - на входы первого дополнительного элемента И 7, на выходах третьего и первого дополнительного элементов И 6 и 7 в моменты совпадения сигналов положительной полярности вырабатываются сигналы положительной полярности (фиг. 2л, к), которые записываются в соответствующие разряды регистра 10 сдвига.

Если разность соседних отсчетов аналогового сигнала к-го канала равна нулю, то моменты изменения состояний t первого

и второго однови.браторов Sj и 9j совпадают (фиг. 2м,и). В результате в этот момент на одних входах третьего и первого дополнительного элементов И 6 и7д появляются потенциалы положительной полярности, а на других входах - потенциалы отрицательной полярности, и на выходах указанных элементов сигналы не вырабатываются. Следовательно, состояния разрядов регистра 10 сдвига, соответствующих к-му каналу, не изменяются, и их содержимое соответствует коду 00.

ЕСЛИ разность соседних отсчетов аналоговой величины к-го канала положительна, то до момента исчезновения потенциала положительной полярности от инверсного выхода первого одновибратора 8 на первом входе третьего элемента И 6д, на его второй вход также поступает потенциал положительной полярности с инверсного выхода второго одновибратора 9 того же канала. Тогда, начиная с момента t (фиг. 2з,к), на обоих входах третьего элемента И бк имеются потенциалы положительной полярности и на его выходе вырабатывается сигнал положительной полярности, длительность которого пропорциональна значению разности соседних отсчетов аналогового сигнала. При этом на входы первого дополнительного элемента И 7д от прямых выходов первого и второго однрвибраторов 8к н 9к поступают потенциалы отрицательной полярности и на выходе этого элемента сигнал не вырабатывается.

Таким образом, с выхода третьего элемента И 6j к-го канала на соответствующий разряд регистра 10 сдвига передается единица, а с выхода первого дополнительного элемента И 7 передается ноль. Следовательно, когда знак разности соседних отсчетов к-го канала положительный, содержимое двух разрядов регистра 10 сдвига, соответствующих к-му каналу, соответствует коду 01.

Если разность соседних сигналов аналогового сигнала к-го канала отрицательна, то до исчезновения потенциала положительной полярности с прямого выхода первого одновибратора 8д на первом входе первого дополнительного элемента И 7g , на его второй вход также поступает потенциал положительной полярности с прямого выхода второго одновибратора 9 того же канала. Тогда, начиная с момента времени , на входах первого дополнительного элемента И 7jt имеются потенциалы положительной полярности. В результате этого с момента времени tj на выходе его вырабатывается сигнал положительной полярности, длительность которого пропорциональна значению разности соседних отсчетов аналогового сигнала того же канала. При этом на входы третьего элемента И 6ц с инверсных выходов первого и второго одновибраторов Sj, и 9, поступают потенциалы отрицательной полярности и на его выходе сигнал не вырабатывается.v

Таким образом, с выхода третьего эле5 мента И 6 на соответствующий разряд регистра 10 сдвига передается нуль, а с выхода первого дополнительного элемента И 7 - единица. Следовательно, когда знак разности соседних отсчетов к-го канала отрицательный, содержимое двух раз рядов регистра 10 сдвига, соответствующих к-му каналу, соответствует коду 01. Частота квантования по времени, как и в известном устройстве, выбирается такой, что разность соседних отсчетов аналоговых ,г сигналов не превосходит единицы квантования по уровню. По заверщению максимального времени преобразования, аналогично описанному, полученные сигналы разности всех каналов запоминаются на соответствующих разрядах регистра 10 сдвига. 0 Во втором такте работы устройства параллельно с определением знаков и значений разностей соседних отсчетов также происходит запись содержимого второго дополнительного регистра 12 сдвига и счетчика 14 во всех адреса дополнительного блока 16 памяти аналогично первому такту преобразования. В конце такта преобразования синхронизатор 1 формирует сигнал, обеспечивающий параллельную передачу содержимого регистра 10 сдвига в первый до0 полнительный регистр 11 сдвига.

После этого начинается очередной третий такт преобразования входных аналоговых сигналов. В начале третьего такта преобразования, когда знаки и значения

5 разностей соседних отсчетов каждого канала, определенные во втором такте, находятся в соответствующих разрядах первого дополнительного регистра 11 сдвига, параллельно с определением разностей соседних отсчетов каждого канала третьего

0 такта преобразования сигнала, с соответствующего выхода синхронизатора 1 аналогично первому и второму такту преобразования, записывает единицу на формирователь 17 адресов, т.е. формирует адрес первого канала, и по этому адресу из допоАнительного блока 16 памяти информация о знаке, значении и количестве подряд идущих одинаковых приращений, записанная во втором такте, переписывается соответственно во второй дополнительный регистр 12 сдвига и счетчик 14. После приема этой информации содержимое второго дополнительного регистра 12 сдвига соответствует нулю, а содержимое счетчика 14 соответствует единице. Затем сигнал с выхода синхронизатора 1 через третий элемент ИЛИ 22 и пятый дополнительный элемент И 26 осуществляет передачу содержимого двух старших разрядов первого дополнительного регистра I1 сдвига во второй дополнительный регистр 12 сдвига и поддерживает содержимое счетчика 14, которое соответствует единице. Далее этот сигнал, аналогично первому и второму такту, через первый элемент ИЛИ 20, задерживаясь на элементе 18 задержки, записывает содержимое второго дополнительного регистра 12 сдвига и счетчика 14 в дополнительный блок 16 памяти в адрес, соответствующий содержимому формирователя 17 адресов, т.е. первому каналу. Затем сигнал с выхода синхронизатора 1 сдвигает содержимое первого дополнительного регистра 11 сдвига на два разряда. При этом в два старших разряда первого дополнительного регистра 11 сдвига записываются знак и значение разности соседних отсчетов аналогового сигнала второго канала, определенных во втором такте преобразования. После этого сигнал с выхода синхронизатора 1, поступая на формирователь 17 адресов, увеличивает его содержимое на единицу, и, аналогично описанному, происходит запись содержимого второго дополнительного регистра 12 сдвига и счетчика в дополнительный блок 16 памяти в адрес, соответствующий второму каналу. Наконец записываются содержимое второго дополнительного регистра 12 сдвига и счетчика в дополнительный блок 16 памяти в адрес, соответствующий N-му каналу. В конце такта преобразования синхронизатор 1 формирует сигнал, обеспечивающий параллельную перезапись регистра 10 сдвига, т.е. знака и значения разностей соседних отсчетов аналоговых сигналов каждого канала, определенных в третьем такте преобразования, в первый дополнительный регистр 11 сдвига. Следовательно, начиная с третьего такта . преобразования, во все адреса дополнительного блока 16 памяти записывается информация о знаке, значении и количестве подряд идущих одинаковых приращений каждого канала, определенная в предыдущем такте преобразования. После этого начинается очередной четвертый такт преобразования входных аналоговых сигналов. В начале этого такта в первом дополнительном регистре 11 сдвига находятся знаки и значения разностей соседних отсчетов аналоговых сигналов каждого канала, определенных в третьем такте преобразования, а в адресах дополнительного блока 16 памяти - информация о знаке, значении и количестве подряд идущих одинаковых приращений, определенная во втором такте преобразования. В этом такте преобразования, аналогично предыдущим тактам, определяются знаки и значения разностей (приращений) соседних отсчетов каждого канала, которые записываются в соответствующие разряды регистра 10 сдвига и параллельно с этим сигнал с выходов синхронизатора 1 записывает единицу в формирователь 17 адресов и по этому адресу из дополнительного блока 16 памяти передаются во второй дополнительный регистр 12 сдвига и в счетчик 14 знак, значение и количество подряд идущих одинаковых приращений первого канала второго такта преобразования. После этого синхронизатор 1 формирует сигнал, который поступает на вход анализатора 13, в котором производится сравнение содержимого двух старщих разрядов первого и второго дополнительных регистров 11 и 12 сдвига, т.е. анализируются знаки и значения приращений третьего и второго тактов преобразования первого канала. Если знак и значение приращения третьего такта не отличается от знака и значения приращения Btoporo такта данного канала, то на выходе анализатора 13 вырабатывается сигнал, который увеличивает содержимое счетчика 14 на единицу. Одновременно сигнал с выхода анализатора 13 через первый элемент ИЛИ 20, элемент 18 задержки переписывает содержимое второго дополнительного регистра 12 сдвига и счетчика 14 в дополнительных блок 16 памяти в адрес, соответствующий содержимому формирователя 17 адресов, т. е в адрес первого канала. Если знак и значение приращения третьего такта преобразования отличается от знака и значения приращения второго такта преобразования данного канала, то от поразрядного анализа содержимого двух старщих разрядов первого и второго дополнительных регистров 11 и 12 на выходе анализатора 13 вырабатывается сигнал, ко-, торый переписьшает содержимое счетчика 14, второго дополнительного регистра 12 сдвига, формирователя 17 адресов через первый элемент ИЛИ 20, третий и четвертый дополнительные элементы И соответственно в блок 15 памяти. Этот же сигнал, аналогично описанному, задерживаясь на дополнительном элементе 19 задержки, через третий элемент ИЛИ записывает в счетчик -14 единицу; переписывает содержимое двух старщих разрядов первого дополнительного регистра 11 сдвига во второй дополнительный регистр 12 сдвига и через первый элемент ИЛИ 20 и элемент 18 задержки переписывается содержимое второго дополнительного регистра 12 сдвига и счетчика 14 в дополнительный блок 16 памяти в адрес, соответствующий содержимому формирователя 17, т.е. второму каналу. Затем сигнал с выхода синхронизатора 1 сдвигает содержимое первого дополнительного регистра 11 сдвига на два разряда, при этом на два старщих разряда первого дополнительного регистра 11 сдвига поступает знак и значение разности соседних отсчетов аналогового сигнала третьего канала. После этого сигнал

с выхода синхронизатора 1, поступая на вход формирователя 17 адресов, увеличивает его содержимое на единицу и описанный процесс повторяется для третьего канала.

Наконец, когда содержимое формирователя 17 адресов соответствует N-му каналу, по этому адресу из дополнительного блока 16 памяти информация о знаке, значении и количестве подряд идущих одинаковых приращений N-ro канала записывается соответственно во второй дополнительный регистр 12 сдвига и в счетчик 14. При этом на двух старших разрядах первого дополнительного регистра 11 сдвига записываются знак и значение приращения N-ro канала третьего такта преобразования. По сигналу с выхода синхронизатора 1 анализатором 13 производится сравнение содержимого двух старших разрядов первого дополнительного регистра 1I сдвига и второго дополнительного регистра 12 сдвига, т.е. аналогично описанному анализируется знак и значение прираш,ений третьего и второго тактов преобразования ,Ы-го канала.

Начиная с пятого такта преобразования устройство работает аналогично четвертому такту преобразования. В случае, когда количество подряд идущих приращений равно единице, устройство работает аналогично описанному, а в тех случаях, когда количество подряд идущих одинаковых приращений больше, чем максимальное значение содержимого счетчика 14, происходит переполнение указанного счетчика 14. При этом на выходе его старшего разряда вырабатывается сигнал, который аналогично сигналу с другого выхода анализатора 13 переписывает содержимое счетчика 14, второго дополнительного регистра 12 сдвига, формирователя 17 адресов через второй элемент ИЛИ 21, второй 23 третий 24 и четвертый 25 дополнительные элементы И соответственно на блок 15 памяти. Этот же сигнал, задержанный дополнительным элементом 19 задержки, через третий элемент ИЛИ 22 записывает в счетчик 14 единицу, через пятый дополнительный элемент И 26 переписывает содержимое двух старших разрядов первого дополнительного регистра 11 сдвига во второй дополнительный регистр 12 сдвига и через первый элемент ИЛИ 20, элемент 18 задержки переписывается содержимое второго дополнительного регистра 12 сдвига и счетчика 14 в дополнительный блок 16 памяти в адрес, соответствующий содержимому формирователя 17 адресов, т.е. номеру канала, для которого наблюдалось переполнение счетчика 14.

Блок 15 памяти состоит из регистров, которые запоминают «словом состоящее из номера канала, знака, значения и количества подряд идущих одинаковых приращений, с которые передаются из формирователя 17 адресов, второго дополнительного регистра 12 сдвига и счетчика 14 соответственно. После каждой такой передачи по сигналу с соответствующего выхода синхронизатора 1 содержимое регистра блока 15 памяти

0 переписывается на следующий регистр, и этим.самым для приема следующего «слова освобождается первый регистр. По мере накопления определенного объема информации в блоке 15 памяти на выходе синхронизатора 1 вырабатывается серия сигналов, которые осуществляют передачу содержимого блока 15 памяти в линию связи.

В результате такой работы устройства в линию связи передается информация только в моменты, когда знак и значение приращений текущего такта преобразования отличаются от знака и значения приращения предыдущего такта преобразования. Благодаря этому происходит значительное сжатие информации, так как в реальных сигналах в больщинстве случаев увеличение или уменьшение сигнала в одном направлении продолжается в течение десятков, а иногда и сотен шагов преобразования, а в некоторых случаях входной сигнал в определенные отрезки времени вообще не изQ меняется. При этом некоррелированность входных сигналов абсолютно не влияет на сжатие объема кодированной информации.

Вследствие накопления информации в блоке 15 памяти не только происходит многократное сжатие объема информации, но и производится передача ее в линию связи по порциям, что также значительно уменьшает общее время передачи информации в линию связи.

Таким образом, в каждом текущем такте работы устройства параллельно с преобразованием и определением знака и значения разности соседних отсчетов всех входных сигналов данного щага также

5 производится определение и передача в линию связи количества подряд идущих одинаковых приращений предыдущих шагов. При этом по сравнению с известным устройством в предлагаемом в два раза повышается быстродействие и для каждого канала вместо интегратора и троичного модулятора используется два одновибратора и элементы И, что значительно упрощает устройство и улучшает технологичность его изготовления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 474112, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство для передачи информации с дельта-модуляцией | 1975 |

|

SU604168A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-07-07—Публикация

1982-04-05—Подача