(54) УСТРОЙСТВО ДЛЯ ДОПУСКСВ.ОГО КОНТРОЛЯ ПАРАМЕТРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство допускового контроля параметров | 1985 |

|

SU1251034A1 |

| Многоканальное устройство для контроля параметров | 1978 |

|

SU911539A2 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Анализатор временных интервалов между импульсами | 1980 |

|

SU900431A1 |

| Многоканальное устройство для контроля параметров | 1978 |

|

SU744616A1 |

| Устройство для контроля дискретного объекта | 1984 |

|

SU1218398A1 |

| Устройство для контроля радиоэлектронных блоков | 1980 |

|

SU945851A1 |

| Устройство для допускового контроля и классификации параметров | 1977 |

|

SU647658A1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

| Устройство для контроля импульсных трансформаторов в составе электронных блоков | 1987 |

|

SU1471158A1 |

1

Изобретение относится к контрольно-измерительной технике и может быть испопьзсдааио при контроле дискретных устройств, в частности электронных вычислительных машин.

Иэвестньхе устройства для допуск(шого контроля построены с использованием либо арифметических д, либо аналоговых 2j узлов. Это усложняет устройства и снижает их надежность.

Наиболее близким по технической сущности к предлагаемому является устройство для допуск(ого контроля параметров, содержащее блок управления, выходы которого соединены со входами входного коммутатора и через выходной коммутатор со входами блока индикации з.

Недостатком этого устройства 5тляется его сложность и низкая надежность.

Цель изобретения - упрощение устройства и повышение его надежности достигается тем, что устройство содержит формирователи импульсов, элементы И, инвертор, триггеры и дешифраторы, выходы блока управления соединены со входами первого триггера, единичный выход которого подключен к перкому входу первого элемента И, второй ВХОД которого через первый формирователь импульссяа соединен со входом инвертора и с выходом входного коммутатора, нулевой выход первого триггера через второй формирователь импульсов

подключен к первому входу второго элемента И, второй вход и выход которого соединены соответственно с выходом инвертора и с единичным входом второго триггера, нулевой вход которого и нулевой

вход третьего триггера подключены к выходу бл(жа управления, первые входы первого и второго дешифраторов соединены с нулевым выходом третьего триггера, вторые входы первого и второго

дешифраторов подсоединены соответственно к единичному и нулевому выходам второго триггера, единичный вход третьего триггера соединен с выходом

ервого элемента И, а единичный выод третьего триггера и выходы дешифаторов подключены ко входам выходого коммутатора.

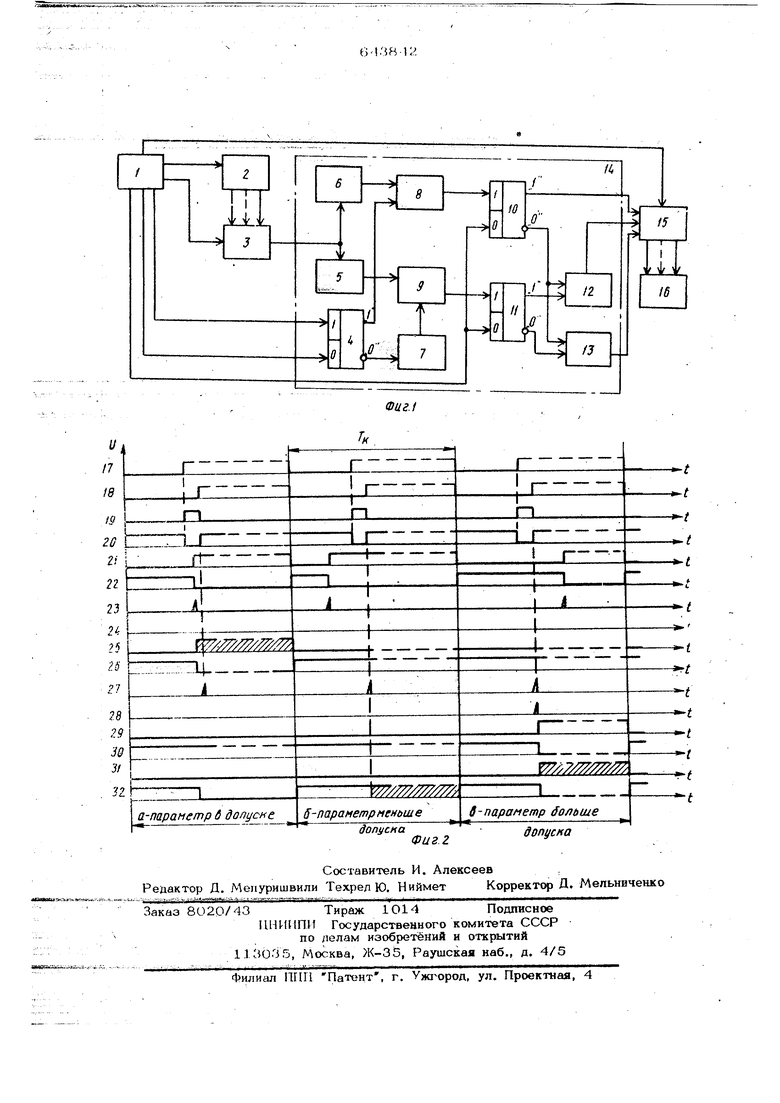

На фиг.1 представлена блок-схема5

редложенного устройства; на фиг. 2 - ременные диаграммы работы устройста, соответствующие различным услоихгм контроля (в допуске, меньше доуска, больше допуска).Ю

В состав бл{ж-схемы (см. фиг. 1) входят блок управления 1, источник контролируемых параметров 2, входной коммутатор 3, первый триггер 4, инвертор 5, первый 6 и второй 7 формиро- 15 ватели импульсов, первый 8 и второй 9 элементы И, третий 10,и второй 11 триггеры, первый 12 и второй 13 дешифраторы, блок логической-обработки 14, выходной коммутатор 15 и блок20

индикации 16.

На фиг. 2 обозначены нижняя граница поля допуска - 17; верхняя граница поля допуска - 18; единичный выход триггера 4 - 19; нулевой выход тригге- 25 ра 4-2О; выход входного коммутатора 21; выход инвертора 5-22; выход первого формирователя импульсов 623; выход элемента И 8 - 24; единичный к нулевой выходы триггера 10-25, 30 26; выход фсфмирователя импульсов 7-27; выход элемента И 9-28; единичный и нулевой выходы триггера 11-,29, 30; выходы дешифраторов 12 и 13-31, 32; Т, к -такт контроля параметра.35

Устройство (см. фиг. 1) работает следующим образом. Блок управления 1 в такте, контроля 1 -того парамет{эа формирует yn-i равляюшие сигналы, по которым входной 0 коммутатор 3 подключает от источника контролируемых параметров 2 на вход блока логической обработки 14 контролируемый I -тый параметр, при этом выходной коммутатор 15 подключает45

соответствующие ячейки памяти блсяса 16 для индикации результатов контроля 1 - того параметра. В начале каждого такта контроля блок управления 1 выдает управляющий сигнал, устанавли- 50 ваюший в исходное (нулевое) состояние триггеры 10 и 11. Затем блок управления 1 выдает сигналы в виде вре, менных интервалов, характеризующие начало и конец поля допуска, на еди-55

ничный и нулевой входы триггера 4. На его выходах формируются разнополярные сигналы в виде временных интервалов.

длительность которых пропориионал.ьН|а полю, допуска.

Временной интервал с единичного выхода триггера 4 поступает для сравнения с контролируемым параметром на один из входов элемента И 8. На второй вход элемента И 8 поступает короткий импульс окончания параметра с формирователя 6, на который с входного коммутатора 3 поступает временной |Интервал контролируемого параметра Одновременно временной интервал контролируемого параметра через инвертор 5 поступает для сравнения с верхней границей поля допуска на один из вход(Ж элемента И 9. На второй вход элемента И 9 с нулевого выхода триггера 4 через формирователь 7 поступает кий импульс верхней границы поля допуска. Элемент И 8 осущес-геляет сравнение временного положения поля дЪ- пуска с коротким импульсом (жончания параметра. .Если короткий импульс сжон- чания параметра пшадает во временной ийтервал, пропорциональный пошо дст1уск то на выходе элемента И 8 появляется короткий импульс, поступающий на единичный вход триггера 16 и уст навлибает его в едийячное состо1гаие. При aTWvi Hia едшшчном выходе триггера 10 формируется положительный сигнал в допуске (см. фиг. 2а), который поступает на соответс пзующую ячейку блока индикации 16 через вьгходной ио мутатор 15. Сигналы не в дсшуске (бошие дсэтуска, меньше допуска ), бпокируются по входам дешифраторов 12 и 13, связанным с нулевым выходом триггера 10.

В случае, если короткий импульс окончания :контролируемого параметра не попадает во временной интервал, пропорциональный погао допуска, на выходе элемента И 8 сигнал отсутствует, и триггер 10 остается в нулевом состоянии.

При этом на единичном выходе триггера 1О сигнал в допускетакже отсутствует.

Одновременно элемент И 9 ocjraeciBляет сравнение временнсяо положения контролируемого napaivreTpa с верхней границей поля допуска, представленной коротким импульсом. Если контролируемый параметр совпадает с верхней границей поля допуска или превышает ее, то на выходе элемента И 9 появляется короткий импульс, который установит 56 триггер 11 в единичное состояние. При этом возможны два случая. В первом случае контролируемый параметр совпадает с верхней -границей поля допуска. При этом выходные сигналы с триггера 11, поступающие на первые входы деш1ф ратора 12 и 13, заблокирсдааны по вторым входам сигналом, снимаемым с нуле вого выхода триггера 10. С выходов дешифраторов 12 и 13 сигналы больше допуска или меньше допуска на выходной коммутатор не поступают. Во втором случае, если контролируемый параметр выходит за поле допуска (триггер 10 находится в нулевом состоянии, дешифраторы 12 и 13 открыты сигналом не в допуске с нулевого выхода триггера 10. При этом си1 нал, снимаемый с единичного выхода триггера 11, поступает на вт(ой вход дешвфрат(а 12, на шлходе формируется сигнал больше допуска , поступающий на блок индикации 16 через выходной коммутатор 15. Сигнал с нулевсяО выхода триггера 11 закртдвает деши фатсф 13, формирующий сипнал меньше допуска (см. фиг. 2 в график 26). Еслн контролируемый параметр мень ше доттуска (см, фиг. 26), то триггерь 1О и 11,остаются в нулевом состоянии, при этом на их единичных выходах сигналы отсутствуют, а с нулевых выходе на дешифратора 13 поступеаот положительные сигналы. На выходе дешифратора 13 формируется выз одной сигнал меньше дрп5ска, поступающий через выходной коммутат1ф 15 на соответствующую ячейку вндикаиви блока 16. После (жончания контроля f параметра блок управления 1 формирует такт контроля следующего парамет ра, и работа устройства по допусковсму контролю следующего.параметра повторяется. Использование предлагаемого устройства для допускового контроля обеспечивает по сравнению с существующими устройствами следукшие преимутиесгтва: - меньшее кояячество примененных в устройстве элементов. Так, для построения устр{йстеа сравнения при 1в-разргднс сетке вычислителя прототип имеет триггеров в 16 раз бол1г2ше, а других логических элементов несколько раз больше; - увеличение надежности устройства и уменьшение его стоимсюти из-за умен1гшения количаства связей и элементов. Формула изобретения Устройство для допусксжсто контроля параметре, содержащее блик управления, выходы которого соединены со входами входного коммутатора и через выходной коммутатор со входами блока индикации, отличающееся тем, что, с целью упрощения и повышения надежности устройства, оно содержит формирователи импульсов, элементы И, инвентор, .тригге1нл и дешифраторы, выходы бл1жа управления соединены со входами первого триггера, единичный вьосод котфого подключен к первому входу первстро элемента И, второй вход котфого через формирсюатель импульсов соединен со входом инвертора и с выхоД(Я«( входного к (шмутатора, нулевой выход первого трВЕГгера через второй формирователь импульсов подключен к входу второго элемента И, втор(й вх{щ и выход которото соединены cooTBOTCi eHHD с шлходом инвертора It едн1шчным входом второго т|шггера, нулевой вход sot4)poro и нулевМ вхсщ третьего триггера подключены к выходу блока управления, входы первого в вт(ого деш1фраторов соединены с нулевым выходом третьего триггера, вторые входы .первого н ВТ1 peto (ю подсоедвнены соохве гственно-Б е;швв шому и нулевому выходам второго т|яятера, единичный вход третьего триггере соедин ен с выходом первого зйемента И а единнчшдй шдход третьего тртггера и выходы Дешифратс с® подключены ко входам вы- , ходного к(ялмута {. Источника няформапяа, принятые во внимание при экспертизе:, 1. Авторское свидетельство СССР Мг 310246, 606 F 7/00, 1968. 2,Автоматический контроль радиоэлектроннот о и электротехнического оборудования.Йод ред. В. М. Шляндина 1, Энергня, 1972, стр. 87 3.Авторское свидетельство СССР № 363982, кл G06 F 15/46, 1971.

Авторы

Даты

1979-01-25—Публикация

1976-09-16—Подача