г«,J2%ri JIС 1Цг, // . Ч И гз; Т

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля операционных усилителей в электронных блоках | 1988 |

|

SU1674018A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ МОТОРНЫМИ ПРИВОДАМИ РАЗЪЕДИНИТЕЛЕЙ КОНТАКТНОЙ СЕТИ | 2004 |

|

RU2274904C2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Система бесперебойного питания | 1990 |

|

SU1807546A1 |

| Агрегат гарантированного питания | 1990 |

|

SU1742942A1 |

| Статический преобразователь с устройством для его управления | 1986 |

|

SU1403215A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля металлизированных переходов печатной платы | 1985 |

|

SU1308955A1 |

| Устройство для управления регулируемым преобразователем переменного напряжения в переменное | 1990 |

|

SU1739452A1 |

| Устройство для контроля температуры погружного электродвигателя и давления на приеме насоса | 1989 |

|

SU1652525A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля параметров импульсных трансформаторов. Цель изобретения - расширение функциональных возможностей устройства и повышение производительности труда за счет автоматической перекоммутации выводов вторичной обмотки и выводов первичной и вторичной обмоток трансформатора между собой. Устройство содержит генератор 1 импульсов, усилитель 2, пиковые детекторы 3,8,17, компараторы 4,5,6,9,18, резистор 7, блок 10 индикации, кнопку 11, блок 12 управления, блок 13 памяти, коммутатор 14, блок 15 перекоммутации, блок 19 защиты. За счет введения пикового детектора 17, компаратора 18, коммутатора 14, блока 15 перекоммутации, блока 12 управления устройство обеспечивает автоматическую перекоммутацию выводов вторичной обмотки и первичной и вторичной обмоток трансформатора между собой для их правильного включения перед началом контроля параметров. Это повышает производительность труда и расширяет функциональные возможности устройства. В описании приведены примеры реализации блока 12 управления, коммутатора 14 и блока 15 перекоммутации. 3 з.п. ф-лы, 4 ил.

4

СП

СХ5

блок 12 управления, блок 13 памяти, коммутатор 14, блок 15 перекоммутации, блок 19 защиты. За счет введения пикового детектора 17, компаратора 18, коммутатора 14, блока 15 перекоммутации, блока 12 управления устройство обеспечивает автоматическую перекоммутацию вьшодоз вторичной обмотки и первичной и вторичной об1

Изобретение относится к контрольно-измерительной технике и предназначено для контроля импульс.ных трансформаторов в составе электронных блоков , а также отдельных трансформаторов вне электронных блоков и может использоваться в автоматизированных контрольно-измерительных комплексах.

Цель изобретения - расширение функциональных возможностей устройства и Повьш1ение производительности труда за счет автоматической перекоммутации выводов вторичной обмотки и выводов первичной и вторичной обмоток трансформатора между собой.

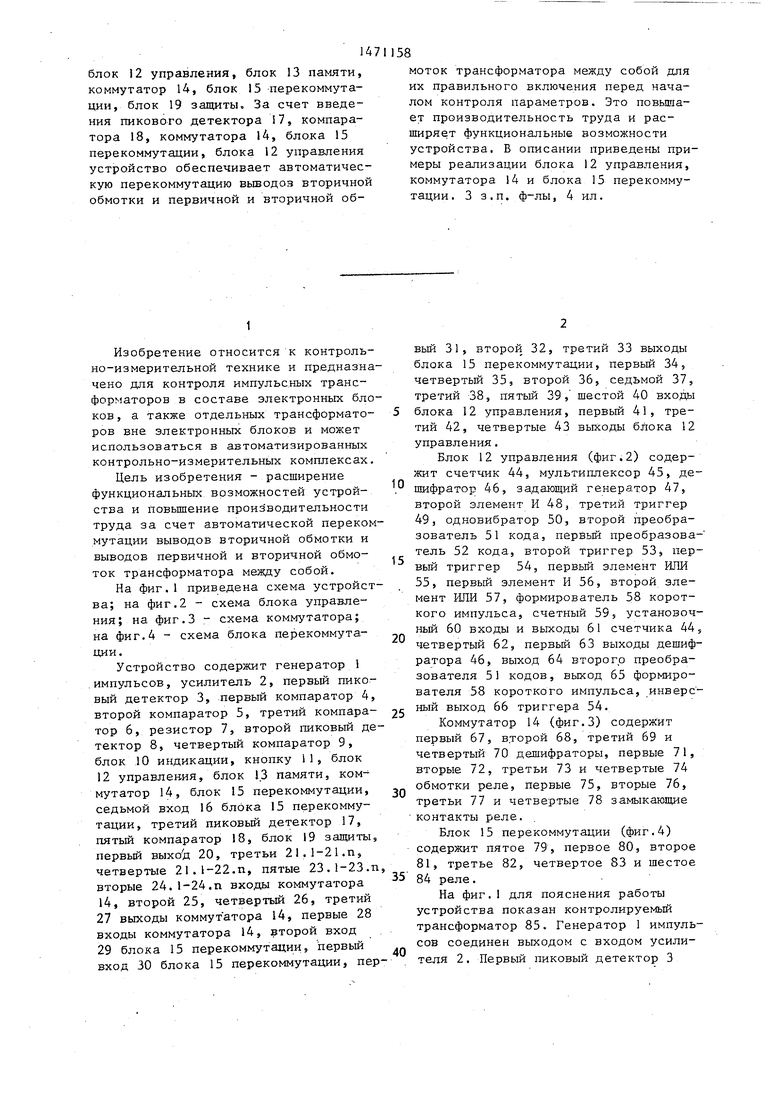

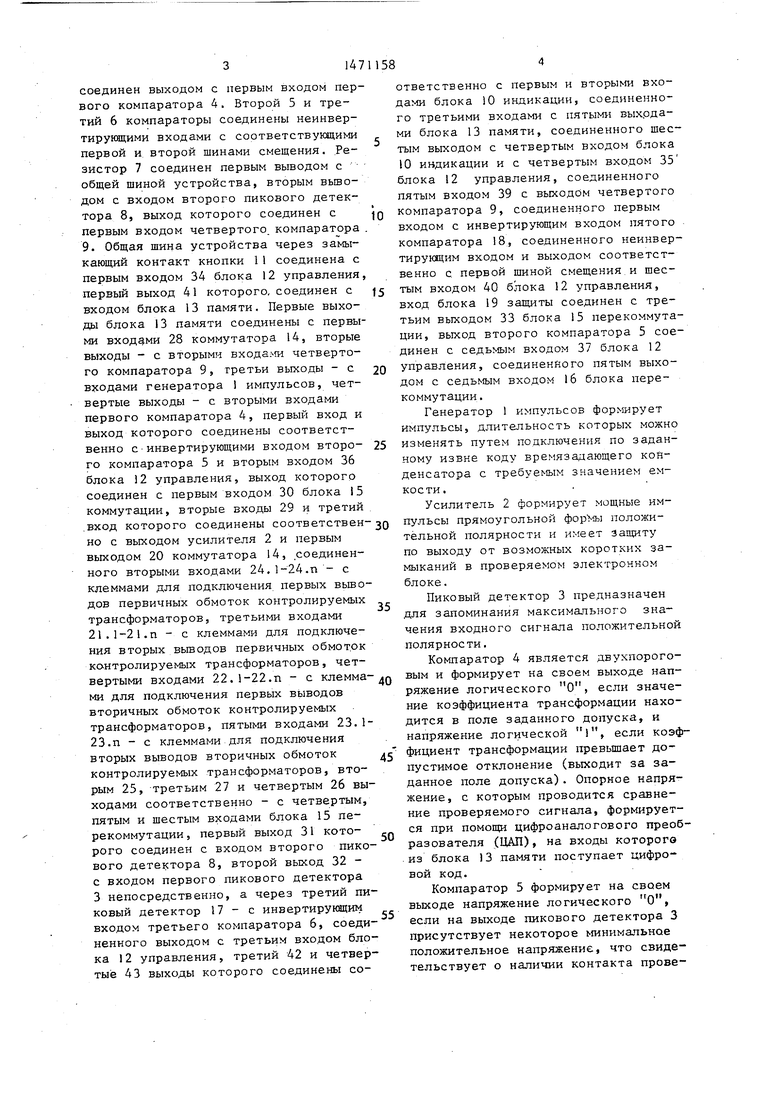

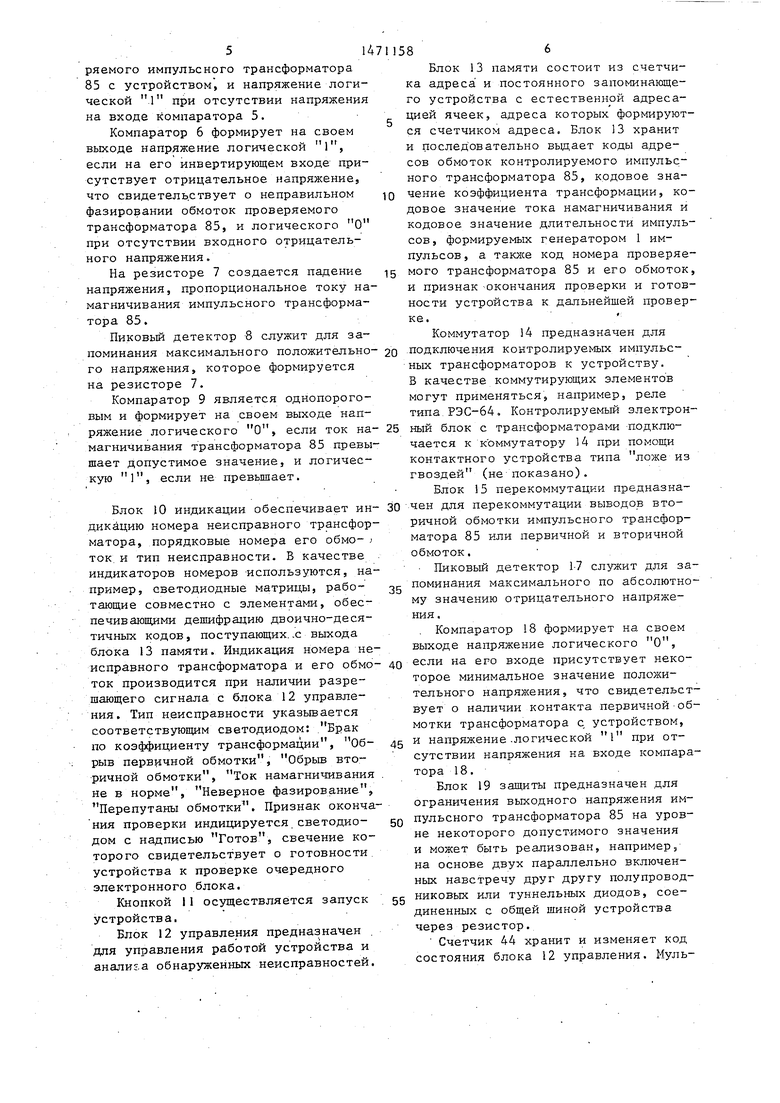

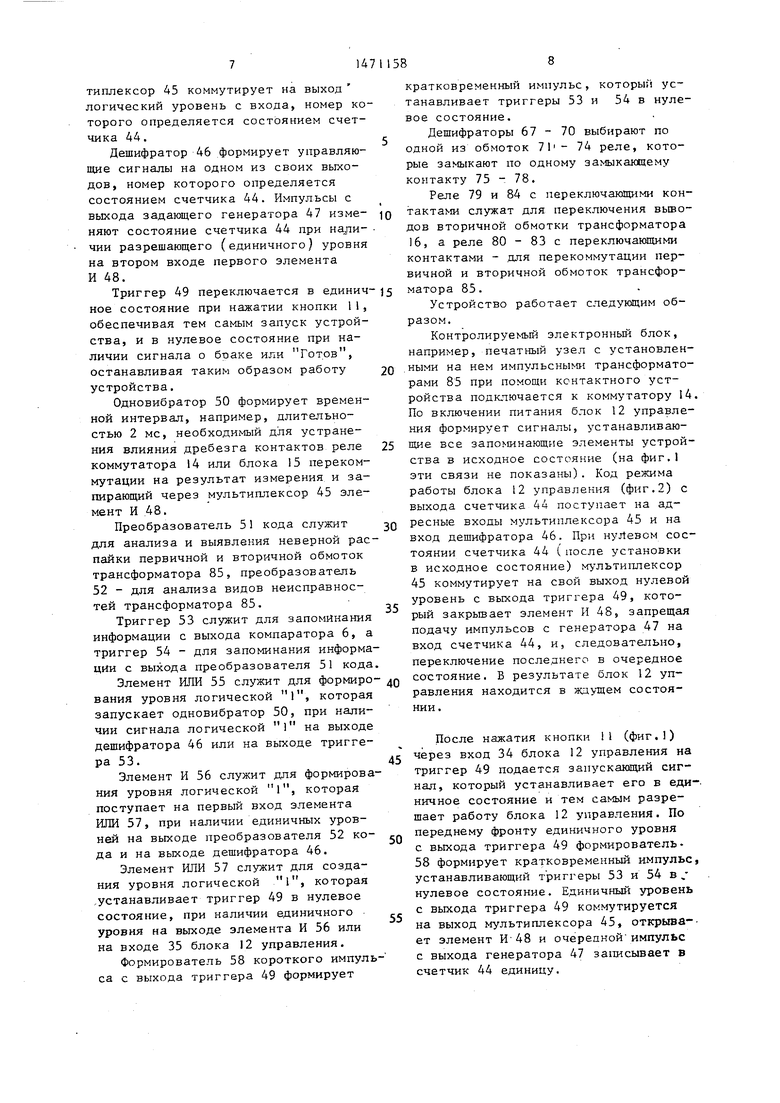

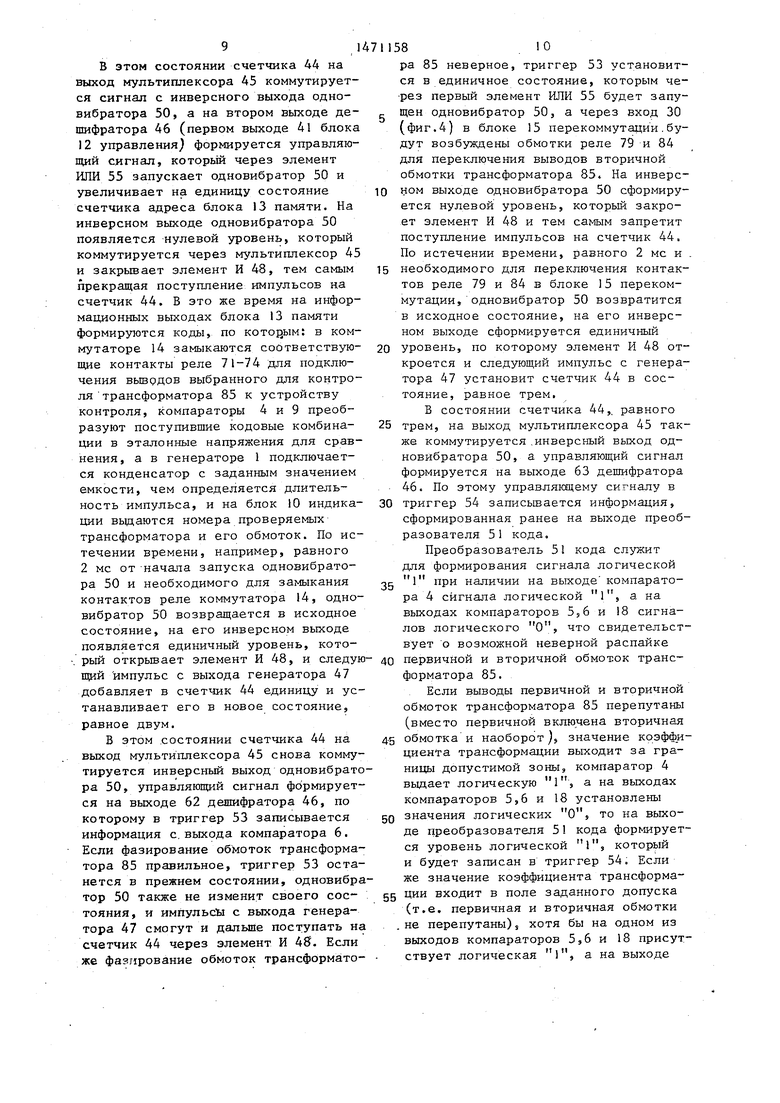

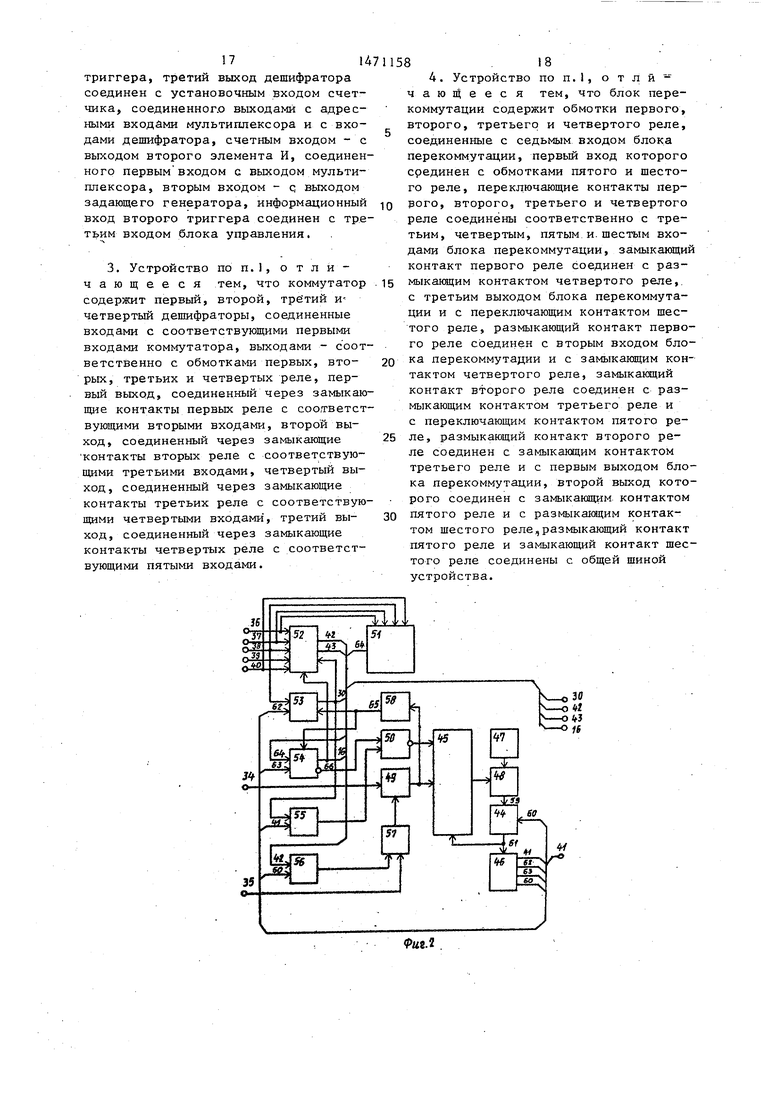

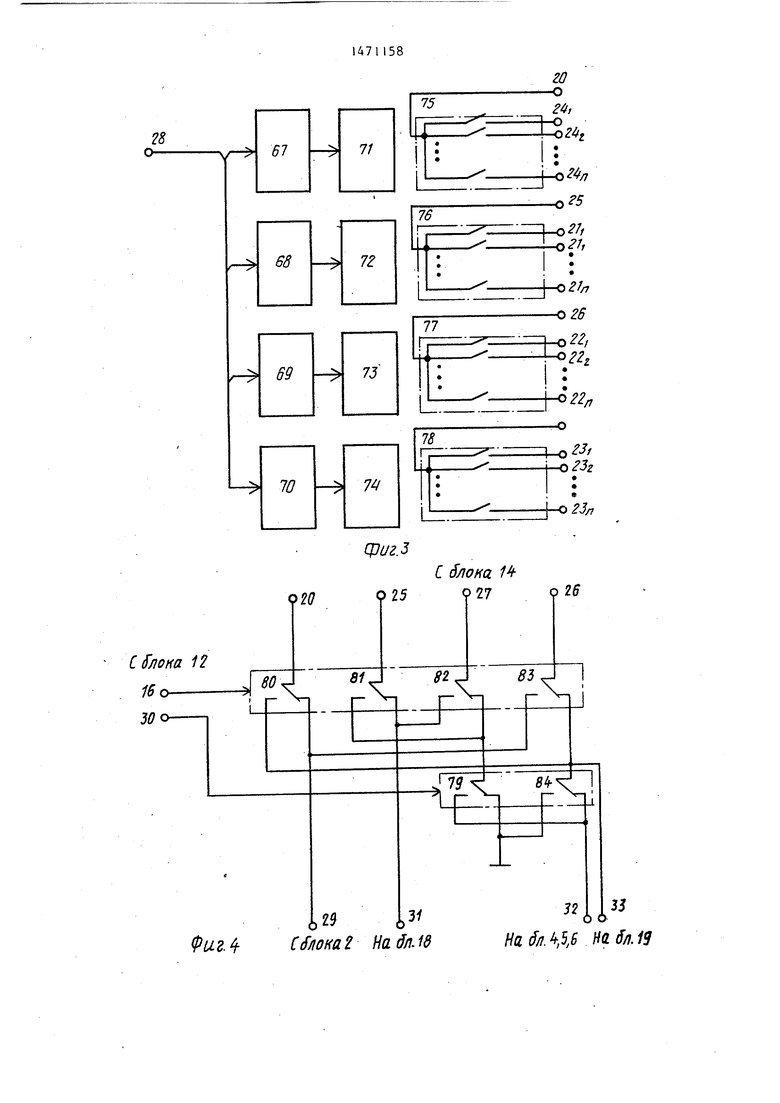

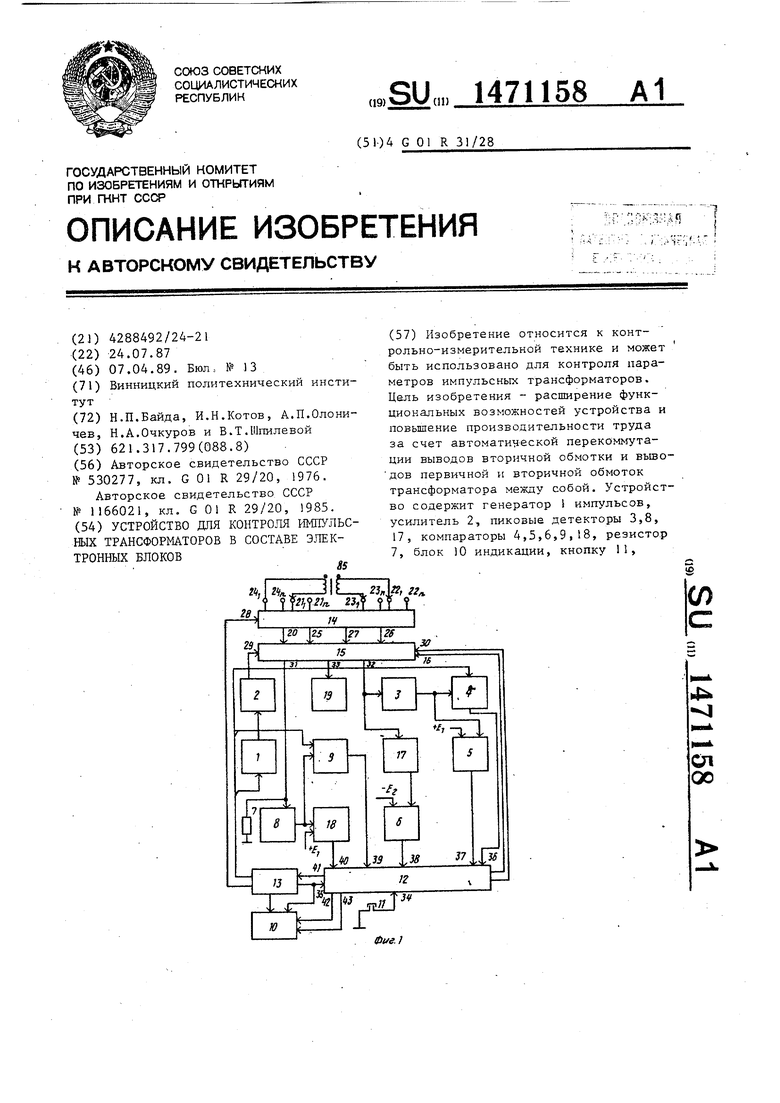

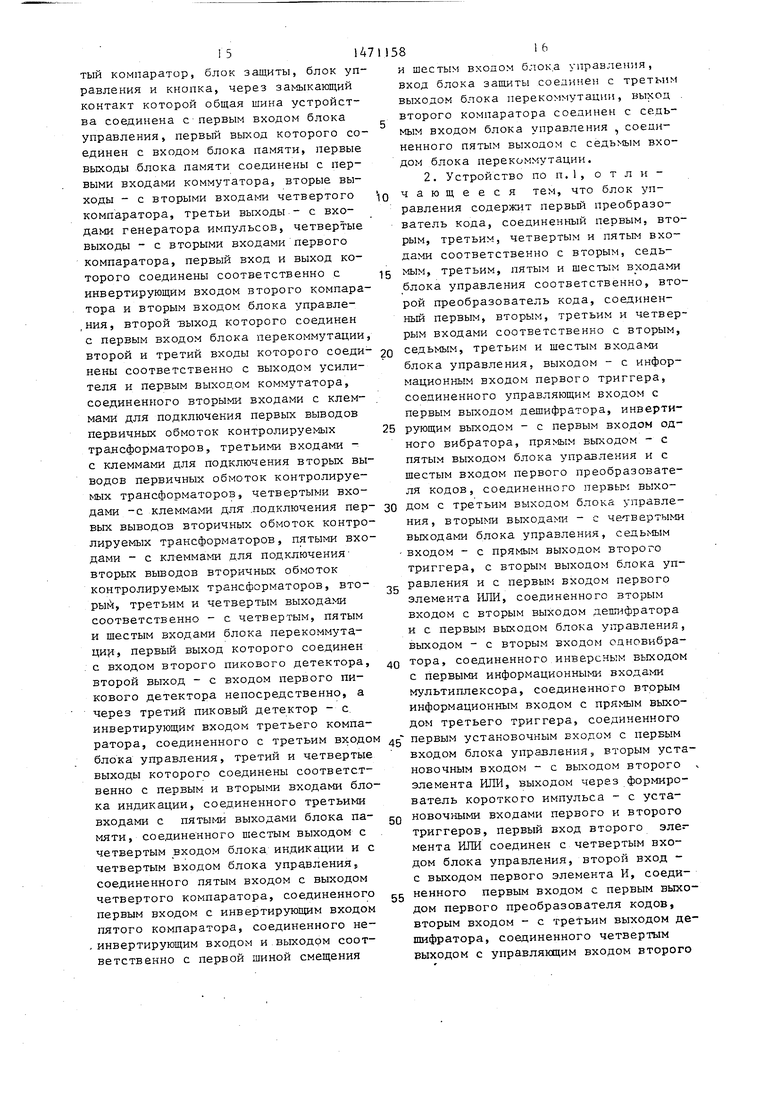

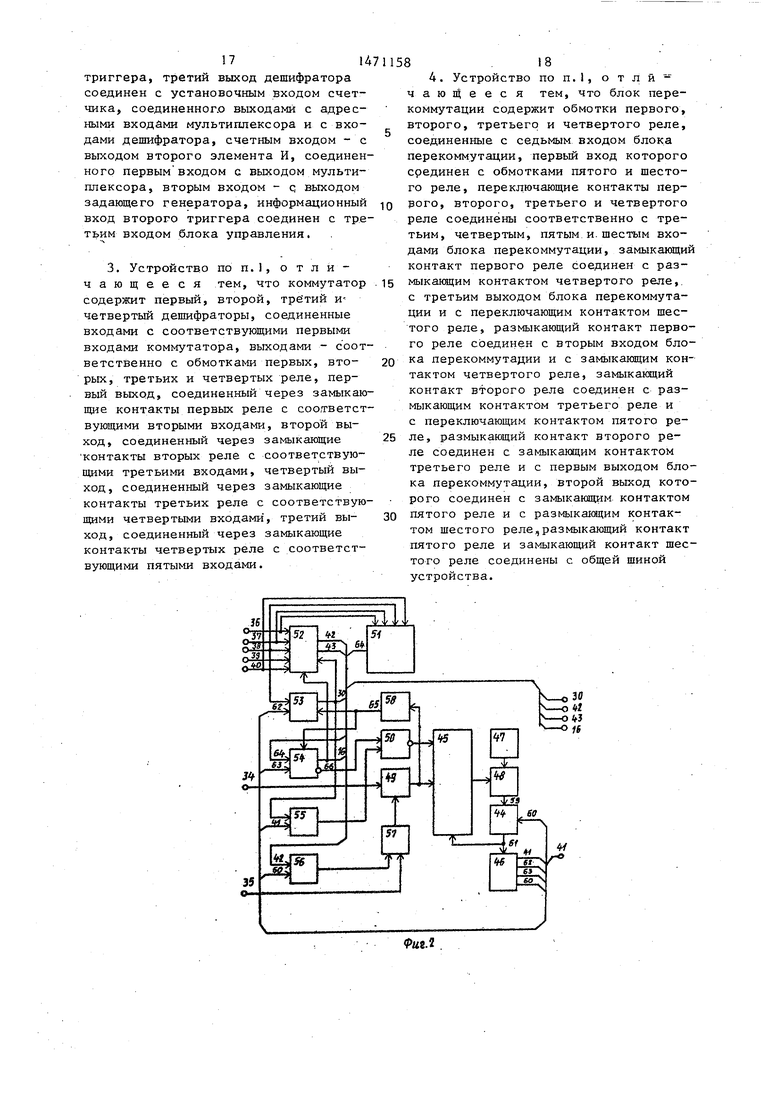

На фиг.1 приведена схема устройства; на фиг.2 - схема блока управления; на фиг.З - схема коммутатора; на фиг.4 - схема блока перекоммутации.

Устройство содержит генератор 1 .импульсов, усилитель 2, первый пиковый детектор 3, первый компаратор 4, второй компаратор 5, третий компаратор 6, резистор 7, второй пиковый детектор 8, четвертый компаратор 9, блок 10 индикации, кнопку 11, блок 12 управления, блок 1.3 памяти, ком- мутатор 14, блок 15 перекоммутации, седьмой вход 16 блока 15 перекоммутации, третий пиковый детектор 17, пятый компаратор 18, блок 19 защиты, первьй выхо д 20, третьи 21. 1-21.п, четвертые 21.1-22.п, пятые 23.1-23.п вторые 24.1-24.п входы коммутатора 14, второй 25, четвертый 26, третий 27 выходы коммутатора 14, первые 28 входы коммутатора 14, второй вход 29 блока 15 перекоммутации, первый вход 30 блока 15 перекоммутации, пермоток трансформатора между собой для их правильного включения перед началом контроля параметров. Это повьшга- ет производительность труда и расширяет функциональные возможности устройства, Б описании приведены примеры реализации блока 12 управления, коммутатора 14 и блока 15 перекоммутации . 3 3.п. ф-лы, 4 ил.

5

0

5

0

5

0

вый 31, второй 32, третий 33 выходы блока 15 перекоммутации, первый 34, четвертьш 35, второй 36, седьмой 37, третий 38, пятый 39, шестой 40 входы блока 12 управления, первый 41, третий 42, четвертые 43 выходы блока 12 управления.

Блок 12 управления (фиг.2) содержит счетчик 44, мультиплексор 45, дешифратор 46, задающий генератор 47, второй элемент И 48j третий триггер 49, одновибратор 50, второй преобразователь 51 кода, первый преобразова- тель 52 кода, второй триггер 53, первый триггер 54, первьш элемент ИЛИ 55, первый элемент И 56, второй элемент ИЛИ 57, формирователь 58 короткого импульса, счетный 59s установочный 60 входы и выходы 61 счетчика 44, четвертый 62, первьй 63 выходы дешифратора 46, выход 64 второго преобразователя 51 кодов, выход 65 формирователя 58 короткого импульса, инверсный выход 66 триггера 54.

Коммутатор 14 (фиг.З) содержит первый 67, второй 68, третий 69 и четвертый 70 дешифраторы, первые 71, вторые 72, третьи 73 и четвертые 74 обмотки реле, первые 75, вторые 76, третьи 77 и четвертые 78 замыкающие контакты реле.

Блок 15 перекоммутации (фиг,4) содержит пятое 79, первое 80, второе 81, третье 82, четвертое 83 и шестое 84 реле.

На фиг, 1 для пояснения работы устройства показан контролируемый трансформатор 85. Генератор 1 импульсов соединен выходом с входом усилителя 2, Первый пиковый детектор 3

соединен выходом с первым входом первого компаратора 4. Второй 5 и третий 6 компараторы соединены неинвер- тируклцими входами с соответствугадими первой и второй шинами смещения. Резистор 7 соединен первым выводом с общей шиной устройства, вторым вьшо- дом с входом второго пикового детектора 8, выход которого соединен с первым входом четвертого, компаратора . 9. Общая шина устройства через замыкающий контакт кнопки 11 соединена с первым входом 34 блока 12 управления, первый выход 41 которого, соединен с входом блока 13 памяти. Первые выходы блока 13 памяти соединены с первыми входами 28 коммутатора 14, вторые выходы - с вторыми входа. четвертого компаратора 9, третьи выходы - с входами генератора 1 импульсов, четвертые выходы - с вторыми входами первого компаратора 4, первый вход и выход которого соединены соответственно синвертирующими входом второго компаратора 5 и вторым входом 36 блока 12 управления, выход которого соединен с первым входом 30 блока 15 коммутации, вторые входы 29 и третий вход которого соединены соответственно с выходом усилителя 2 и первым выходом 20 коммутатора 14, соединенного вторыми входами 24.1-24.п - с клеммами для подключения первых вьшо- дов первичных обмоток контролируемых трансформаторов, третьими входами 2l.l-2i,n - с клеммами для подключения вторых вьшодов первичных обмоток ко-нтролируемых трансформаторов, четвертыми входами 22.1-22.П - с клемма ми для подключения первых выводов вторичных обмоток контролируемых трансформаторов, пятыми входами 23 23.п - с клеммами для подключения вторых выводов вторичных обмоток контролируемых трансформаторов, вторым 25, третьим 27 и четвертым 26 выходами соответственно - с четвертым, пятым и шестым входами блока 15 перекоммутации, первый выход 31 которого соединен с входом второго пикового детектора 8, второй выход 32 с входом первого пикового детектора 3 непосредственно, а через третий пиковый детектор 17 - с инвертирукяцим входом третьего компаратора 6, соединенного выходом с третьим входом блока 12 управления, третий 42 и четвертые 43 выходы которого соединены со110

15

20

25

30

35

40

45

50

55

ответственно с первым и вторыми вхо дами блока 10 индикации, соединенного третьими входами с пятым 5 выходами блока 13 памяти, соединенного шестым выходом с четвертым входом блока 10 индикации и с четвертым входом 35 блока 12 управления, соединенного пятым входом 39 с выходом четвертого компаратора 9, соединенного первым входом с инвертирующим входом пятого компаратора 18, соединенного неинвер- тирунвдим входом и выходом соответственно с первой шиной смещения.и шестым входом 40 блока 12 управления, вход блока 19 защиты соединен с третьим выходом 33 блока 15 перекоммутации, выход второго компаратора 5 соединен с седьмым входом 37 блока 12 управления, соединенного пятым выходом с седьмым входом 16 блока перекоммутации.

Генератор 1 импульсов формирует импульсы, длительность которых можно изменять путем подключения по заданному извне коду времязадающего конденсатора с требуемым значением емкости.

Усилитель 2 формирует мощные импульсы прямоугольной форМ положительной полярности и имеет по выходу от возможных коротких замыканий в проверяемом электронном

блоке.

Пиковый детектор 3 предназначен для запоминания максимального значения входного сигнала положительной полярности.

Компаратор 4 является двухпорого- вым и формирует на своем выходе напряжение логического О, если значение коэффициента трансформации находится в поле заданного допуска, и напряжение логической l, если коэффициент трансформации превьшает допустимое отклонение (выходит за заданное поле допуска). Опорное напряжение, с которым проводится сравнение проверяемого сигнала, формируется при помощи цифроанапогового преобразователя (ЦАП), на входы которого из блока )3 памяти поступает цифровой код.

Компаратор 5 формирует на своем выходе напряжение логического О, если на выходе пикового детектора 3 присутствует некоторое минимальное положительное напряжение, что свидетельствует о наличии контакта прове

ряемого импульсного трансформатора 85 с устройством , и напряжение логической 1 при отсутствии напряжения на входе компаратора 5.

Компаратор 6 формирует на своем выходе напряжение логической 1, если на его инвертирующем входе присутствует отрицательное напряжение, что свидетельствует о неправильном фазировании обмоток проверяемого трансформатора 85, и логического О при отсутствии входного отрицательного напряжения.

На резисторе 7 создается падение напряжения, пропорциональное току намагничивания импульсного трансформатора 85.

Пиковьй детектор 8 служит для запоминания максимального положительно го напряжения, которое формируется на резисторе 7.

Компаратор 9 является однопорого- вым и формирует на своем выходе напряжение логического О, если ток намагничивания трансформатора 85 превышает допустимое значение, и логическую 1, если не превышает.

Блок 10 индикации обеспечивает ин- дикацию номера неисправного трансформатора, порядковые номера его обмо- ток. и тип неисправности. В качестве индикаторов номер-ов используются, например, светодиодные матрицы, рабо- тающие совместно с элементами, обеспечивающими депшфрацию двоично-десятичных кодов, поступающих, .с выхода блока 13 памяти. Индикация номера неисправного трансформатора и его обмо ток производится при наличии разрешающего сигнала с блока 12 управления. Тип неисправности указьюается соответствующим светодиодом: Брак по коэффициенту трансформации, Об- рыв первичной обмотки, Обрьш вторичной обмотки, Ток намагничивания не в норме, Неверное фазирование, Перепутаны обмотки. Признак оконча ния проверки индицируется.светодио- дом с надписью Готов, свечение которого свидетельствует о готовности устройства к проверке очередного электронного блока.

Кнопкой I1 осуществляется запуск устройства.

Блок 12 управления предназначен . для управления работой устройства и анализа обнаруженных неисправностей.

10

20

7П586

Блок 13 памяти состоит из счетчика адреса и постоянного запоминающего устройства с естественной адресацией ячеек, адреса которых формируются счетчиком адреса. Блок 13 хранит и послед овательно вьщает коды адресов обмоток контролируемого импульс;- ного трансформатора 85, кодовое значение коэффициента трансформации, кодовое значение тока намагничивания и кодовое значение длительности импульсов, формируемых генератором 1 импульсов , а такхсе код номера проверяемого трансформатора 85 и его обмоток, и признак -окончания проверки и готовности устройства к дальнейшей проверке.

Коммутатор 14 предназначен для .подключения контролируемых импульсных трансформаторов к устройству. В качестве коммутирующих элементов могут применяться, например, реле типа,РЭС-64. Контролируемый электронный блок с трансформаторами подклю15

25

чается к коммутатору 14 при помощи контактного устройства типа ложе из гвоздей (не показано).

Блок 15 перекоммутации предназначен для перекоммутадии выводов вторичной обмотки импульсного трансформатора 85 или первичной и вторичной обмоток.

Пиковый детектор 1-7 служит для запоминания максимального по абсолютному значению отрицательного напряжения.

Компаратор 18 формирует на своем выходе напряжение логического О, если на его входе присутствует некоторое минимальное значение положительного напряжения, что свидетельствует о наличии контакта первичнойобмотки трансформатора с, устройством, и напряжение.логической l при отсутствии напряжения на входе компаратора 18.

Блок 19 защиты предназначен для ограничения выходного напряжения импульсного трансформатора 85 на уровне некоторого допустимого значения и может быть реализован, например, на основе двух параллельно включенных навстречу друг другу полупроводниковых или туннельных диодов, соединенных с общей щиной устройства через резистор.

Счетчик 44 хранит и изменяет код состояния блока 12 управления. Мультиплексор 45 коммутирует на выход логический уровень с входа, номер которого определяется состоянием счетчика 44.

Дешифратор 46 формирует управляющие сигналы на одном из своих выходов, номер которого определяется состоянием счетчика 44. Импульсы с выхода задающего генератора 47 изме- няют состояние счетчика 44 при нали- чии разрешающего (единичного) уровня на втором входе первого элемента И 48.

Триггер 49 переключается в единич- ное состояние при нажатии кнопки I1, обеспечивая тем самым запуск устройства, и в нулевое состояние при наличии сигнала о браке или Готов, останавливая таким образом работу устройства.

Одновибратор 50 формирует временной интервал, например, длительностью 2 мс, необходимый для устранения влияния дребезга контактов реле коммутатора 14 или блока 15 перекоммутации на результат измерения и запирающий через мультиплексор 45 элемент И 48.

Преобразователь 51 кода служит для анализа и выявления неверной распайки первичной и вторичной обмоток трансформатора 85, преобразователь 52 - для анализа видов неисправностей трансформатора 85.

Триггер 53 служит для запоминания информации с выхода компаратора 6, а триггер 54 - для запоминания информации с выхода преобразователя 51 кода

Элемент ИЛИ 55 служит для формиро вания уровня логической 1, которая запускает одновибратор 50, при наличии сигнала логической 1 на выходе дешифратора 46 или на выходе триггера 53.

Элемент И 56 служит для формирования уровня логической 1, которая поступает на первый вход элемента ИЛИ 57, при наличии единичных уровней на выходе преобразователя 52 ко- да и на выходе дешифратора 46.

Элемент ИЛИ 57 служит для создания уровня логической Г , которая ,устанавливает триггер 49 в нулевое состояние, при наличии единичного уровня на выходе элемента И 56 или на входе 35 блока 12 управления.

Формирователь 58 короткого импул са с выхода триггера 49 формирует

кратковременный импульс, который устанавливает триггеры 53 и 54 в нулевое состояние.

Дешифраторы 67 - 70 выбирают по одной из обмоток 71 - 74 реле, которые замыкают по одному замыкающему контакту 75 - 78.

Реле 79 и 84 с переключающими контактами служат для переключения вьшо- дов вторичной обмотки трансформатора 16, а реле 80 - 83 с переключающими контактами - для перекоммутации первичной и вторичной обмоток трансформатора 85.

Устройство работает следующим образом.

Контролируемый электронный блок, например, печатный узел с установлен- .ными на нем импульсными трансформаторами 85 при помощи контактного устройства подключается к коммутатору 14 По включении питания блок 12 управления формирует сигналы, устанавливающие все запоминающие элементы устройства в исходное состояние (на фиг.1 эти связи не показаны). Код режима работы блока 12 управления (фиг.2) с выхода счетчика 44 поступает на адресные входы мультиплексора 45 и на вход дешифратора 46. При нулевом состоянии счетчика 44 (после установки в исходное состояние) мультигшексор 45 коммутирует на свой выход нулевой уровень с выхода триггера 49, который закрьшает элемент И 48, запрещая подачу импульсов с генератора 47 на вход счетчика 44, и, следовательно, переключение последнего в очередное состояние. В результате блок 12 управления находится в ждущем состоянии.

После нажатия кнопки 11 (фиг.1) через вход 34 блока 12 управления на триггер 49 подается запускающий сигнал, который устанавливает его в еди ничное состояние и тем самым разрешает работу блока 12 управления. По переднему фронту единичного уровня с выхода триггера 49 формирователь- 58 формирует кратковременный импульс устанавливающий триггеры 53 и 54 в , нулевое состояние. Единичный уровень с выхода триггера 49 коммутируется на выход мультиплексора 45, открывает элемент И-48 и очередной импульс с выхода генератора 47 записывает в счетчик 44 единицу.

10

91471

В этом состоянии счетчика 44 на ыход мультиплексора 45 коммутируетя сигнал с инверсного выхода одно- ибратора 50, а на втором выходе де- g ифратора 46 (первом выходе 41 блока I2 управления} формируется управляюий сигнал, которьш через элемент ЛИ 55 запускает одновибратор 50 и увеличивает на единицу состояние четчика адреса блока 13 памяти. На нверсном выходе одновибратора 50 появляется нулевой уровень, который коммутируется через мультиплексор 45 закрьшает элемент И 48, тем самым прекращая поступление импульсов на счетчик 44. В это же время на информационных выходах блока 13 памяти формируются коды, по которым: в коммутаторе 14 замыкаются соответствующие контакты реле 71-74 для подключения вьшрдов выбранного для контроля трансформатора 85 к устройству контроля, компараторы 4 и 9 преобразуют поступившие кодовые комбинации в эталонные напряжения для сравнения, а в генераторе 1 подключается конденсатор с заданным значением емкости, чем определяется длительность импульса, и на блок 10 индикации выдаются номера проверяемых трансформатора и его обмоток. По истечении времени, например, равного 2 мс от-начала запуска одновибратора 50 и необходимого для замыкания контактов реле коммутатора 14, одно- вибратор 50 возвращается в исходное состояние, на его инверсном выходе появляется единичный уровень, кото- рый открьшает элемент И 48, и следующий импульс с выхода генератора 47 добавляет в счетчик 44 единицу и устанавливает его в новое состояние, равное двум.

В этом состоянии счетчика 44 на выход мультиплексора 45 снова коммутируется инверсный выход одновибратора 50, управляющий сигнал формируется на выходе 62 дешифратора 46, по которому в триггер 53 записывается информация с, выхода компаратора 6. Если фазирование обМоток трансформатора 85 правильное, триггер 53 останется в прежнем состоянии, одновибратор 50 также не изменит своего состояния, и импульсы с выхода генератора 47 смогут и дальше поступать на счетчик 44 через элемент И 48. Если же фазпрование обмоток трансформато

5

0

ра 85 неверное, триггер 53 установится в единичное состояние, которым че- рез первый элемент ИЛИ 55 будет запущен одновибратор 50, а через вход 30 (фиг.4) в блоке 15 перекоммутации.будут возбуждены обмотки реле 79 и 84 для переключения выводов вторичной обмотки трансформатора 85. На инверсном выходе одновибратора 50 сформируется нулевой уровень, который закроет элемент И 48 и тем самым запретит поступление импульсов на счетчик 44. По истечении времени, равного 2 мс и . необходимого для переключения контактов реле 79 и 84 в блоке 15 перекоммутации, одновибратор 50 возвратится в исходное состояние, на его инверсном выходе сформируется единичный уровень, по которому элемент И 48 откроется и следующий импульс с генератора 47 установит счетчик 44 в состояние, равное трем,

Б состоянии счетчика 44,, равного 5 трем, на выход мультиплексора 45 также коммутируется.инверсный выход одновибратора 50, а управляющий сигнал формируется на выходе 63 дешифратора 46. По этому управлякщему сигналу в триггер 54 записьшается информация, сформированная ранее на выходе преобразователя 51 кода.

Преобразователь 51 кода служит для формирования сигнала логической 1 при наличии на выходе компарато0

5„

ра 4 сигнала логической 1, а на

выходах компараторов 5,6 и 18 сигналов логического О, что свидетельствует о возможной неверной распайке

0 первичной и вторичной обмоток трансформатора 85.

Если выводы первичной и вторичной обмоток трансформатора 85 перепутаны (вместо первичной включена вторичная

4-5 обмотка и наоборот, значение коэффициента трансформации выходит за границы допустимой зоны, компаратор 4 выдает логическую 1, а на выходах компараторов 5,6 и 18 установлены

50 значения логических О, то на выходе преобразователя 51 кода формируется уровень логической 1, который и будет записан в триггер 54. Если же значение коэффициента трансформа55 Ции входит в поле заданного допуска (т.е. первичная и вторичная обмотки . не перепутаны), хотя бы на одном из выходов компараторов 5,6 и 18 присутствует логическая l, а на выходе

преобразователе 51 кода сформирован логический О. Триггер 54 после его стробирования с выхода 63 дешифратора 46 остается в исходном состоянии, одновибратор 50 также не изменяет своего состояния, импульсы с выхода генератора 47 и дальше поступают на счетчик 44 через элемент И 48.

Если же в триггер 54 записана логическая 1, т.е. первичная и вторичная обмотки трансформаторов 85 , перепутаны между собой, сигнал с инверсного выхода 66 этого триггера запустит одновибратор 50, а через выход блока 12 управления и вход 16 блока 15 перекоммутации будут возбуждены обмотки реле 80-83 для переключения выводов первичной и вторичной обмоток трансформатора между собой. На инверсном выходе одновибра- тора 50 формируется нулевой уровень, который закрывает элемент И 48, и тем самым запрещает дальнейшее поступление импульсов на счетчик 44. По .истечении времени, равного 2 мс и необходимого для переключения контактов в группе реле 80 - 83 в блоке 15 перекоммутации, одновибратор 50 возвращается в исходное состояние, на его инверсном выходе формируется уровень логической 1, по которому открывается элемент И 48 и следующий импульс с генератора 47 устанавливает счетчик 44 в состояние, равное четырем.

Преобразователь 52 кода формирует на выходе 42 блока 12 сигнал разреше- ния индикации при обнаружении брака, а на остальных выходах - сигналы Брак по коэффициенту трансформации, Обрыв первичной обмотки, Обрыв вторичной обмотки, Ток намагничивания не в норме, Неверное фазирование, Перепутаны обмотки. Сигнал ; Брак по коэффициенту трансформации формируется (фиг.1 и 2). при наличии логической 1 на информационном входе 36 блока 12 управления и логичес- ких нулей на входах 37,38 и 40. Сигнал Обрыв первичной обмотки формируется при наличии логической 1 на входе 40 блока 12 управления. Сигнал Обрьш вторичной обмотки формирует39 блока 12 управления. Сигнал Неверное фазирование формируется при наличии единичного уровня на прямом выходе триггера 53. Сигнал Перепутаны обмотки формируется при наличии единичного уровня на прямом выходе триггера 54 и логического О на входе 36 блока 12 управления. При на- ТО личии хотя бы одного из перечисленных сигналов на выходе формирователя 52 кода, соединенном с входом элемента И 56, формируется сигнал, свидетельствующий о браке в проверяемом 15 трансформаторе (логическая 1).

Опрос элемента И 56 производится сигналом с дешифратора 46, который формируется следующим образом.

Б состоянии счетчика 44, равном 20 четырем, на выход мультиплексора 45 коммутируется выход триггера 49, а на входы 60 счетчика 44 с выхода дешифратора 46 поступает сигнал, который устанавливает счетчик 44 в исход- 25 ное (нулевое) состояние. Этот же сигнал поступает на вход элемента И 56. Если на первом выходе преобразователя 52 кода присутствует логическая 1, что свидетельствует о браке в 30 проверяемом трансформаторе 85, передний фронт управляющего сигна/ia через открытый элемент И 56 и элемент ИЛИ 57 установит триггер 49 в нулевое состояние, которым через мультиплексор 45 будет закрыт элемент И 48.

35

Поступление импульсов с генератора

47 на счетчик 44 будет приостановлено, устройство перейдет в ждущее состояние. Одновременно с одного из выхо40 дов преобразователя 52 кода через выход 42 блока 12 управления на блок 10 индикации поступит сигнал разрешения индикации номера неисправного трансформатора и его обмоток, а с ос45 тальных выходов преобразователя 52 кодов через выходы 43 с блока 12 уп--- равления на блок 10 индикации поступают сигналы видов неисправностей трансформатора 85.

50 После нажатия кнопки I1 устройство переходит к контролю следукщего импульсного трансформатора 85 в составе электронного-блока. Если конт- ролируемый трансформатор 85 исправен

ся при наличии логической 1 на вхо- 55 на

де 37 блока 12 управления и логичес- вателя 52 кода формируется логичес

кого о

II с:;нал т;кна- кий О, который закрывает элемент на входе 4U. ncwi ,г.отп пызсопа леш

магничивания не в норме формируется при наличии логического О на входе

IVWjrl V/ у i-s. - л -

И 56, сигнал с третьего выхода дешиф ратора 46 не изменяет состояние триг

; 39 блока 12 управления. Сигнал Неверное фазирование формируется при наличии единичного уровня на прямом выходе триггера 53. Сигнал Перепутаны обмотки формируется при наличии единичного уровня на прямом выходе триггера 54 и логического О на входе 36 блока 12 управления. При на- О личии хотя бы одного из перечисленных сигналов на выходе формирователя 52 кода, соединенном с входом элемента И 56, формируется сигнал, свидетельствующий о браке в проверяемом 5 трансформаторе (логическая 1).

Опрос элемента И 56 производится сигналом с дешифратора 46, который формируется следующим образом.

Б состоянии счетчика 44, равном 20 четырем, на выход мультиплексора 45 коммутируется выход триггера 49, а на входы 60 счетчика 44 с выхода дешифратора 46 поступает сигнал, который устанавливает счетчик 44 в исход- 25 ное (нулевое) состояние. Этот же сигнал поступает на вход элемента И 56. Если на первом выходе преобразователя 52 кода присутствует логическая 1, что свидетельствует о браке в 30 проверяемом трансформаторе 85, передний фронт управляющего сигна/ia через открытый элемент И 56 и элемент ИЛИ 57 установит триггер 49 в нулевое состояние, которым через мультиплексор 45 будет закрыт элемент И 48.

35

Поступление импульсов с генератора

47 на счетчик 44 будет приостановлено, устройство перейдет в ждущее состояние. Одновременно с одного из выхо40 дов преобразователя 52 кода через выход 42 блока 12 управления на блок 10 индикации поступит сигнал разрешения индикации номера неисправного трансформатора и его обмоток, а с ос45 тальных выходов преобразователя 52 кодов через выходы 43 с блока 12 уп--- равления на блок 10 индикации поступают сигналы видов неисправностей трансформатора 85.

50 После нажатия кнопки I1 устройство переходит к контролю следукщего импульсного трансформатора 85 в составе электронного-блока. Если конт- ролируемый трансформатор 85 исправен.

55 на

кий О, который закрывает элемент ,г.отп пызсопа леш

IVWjrl V/ у i-s. - л -

И 56, сигнал с третьего выхода дешифратора 46 не изменяет состояние триг13

гера 49 (на прямом выходе триггера 49 остается единичный уровень). В этом случае процесс контроля очередного импульсного трансформатора продолжается автоматически.

После О1 ончания проверки импульс- ных трансформаторов в составе электронного блока единичный сигнал с выхода блока-13 памяти поступает через вход 35 блока 12 управления и через элемент ИЛИ 57 на триггер 49 и своим передним фронтом -устанавливает триггер 49 в нулевое состояние, на блок 10 индикации, где возбуждает светодиод с надписью Готов, на счетчик адреса в блоке 13 памяти и своим передним фронтом устанавливает этот счетчик адреса в нулевое состояние. В нулевом состоянии счетчика адреса на всех выходах блока 13 памяти формируются нулевые уровни, кроме шестого выхода, соединенного с блоком 10 индикации. Единичньш сигнал с этого выхода поддерживает свечение светодиода с надписью Готов, что свидетельствует о нахождении устройства в ждущем состоянии и готовности его к проверке очередного электронного блока.

Коммутатор 14 (фиг.З) работает следующим образом.

Коды адресов точек подключения обмоток контролируемого трансформатора 85 с выхода блока 13 памяти поступают на входы дешифраторов 67 - 70, выходные сигналы которых возбуждают по одной: обмотке 71-74 реле. Возбужденные обмотки реле вызьшают замыкание по одному контакту из контактов 75 - 78. Выбранный контакт 75 реле подключает первый вывод первичной обмотки трансформатора 85 через вход 24.1 и выход 20 коммутатора 14 и через блок 15 перекоммутации к выходу усилителя 2. Второй вывод первичной обмотки трансформатора 85 выбранным контактом 76 реле подключается через вход 21.1, выход

25коммутатора 14 и через.блок 15 перекоммутации к входу пикового детектора 8 и к резистору 7. Первый вывод вторичной обмотки трансформатора 85 выбранным контактом 77 реле подключается через вход 22.1, выход

26коммутатора 14 и далее через блок 15 перекоммутации к входам пиковых детекторов 3 и 17, а также через выход 33 блока 15 перекоммута. 711581

ции к входу блока 19 защиты. Второй вывод вторичной обмотки трансформатора 85 выбранным контактом 78 реле соединяется через вход 23.1, выход 27 коммутатора 14 (в блоке 15 перекоммутации) с общей шиной устройства. Влок 15 перекоммутации (фиг.4) работает следующим образом.

10 Если фазирование обмоток трансформатора 85 неверное, из блока 12 управления на вход 30 блока 15 перекоммутации поступает управляющий сигнал, по которому возбуждаются обмотки ре15 ле 79 и 84 и происходит перекоммутация первого и второго выводов вторичной обмотки трансформатора 85 между собой. При неверной установке первичной и вторичной обмоток трансформато20 ра 85 из блока-12 управления на вход 16 блока 15 перекоммутации поступает управляющий сигнал, по которому возбуждаются обмотки реле 80 - 83 и происходит перекоммутация выводов пер25 вичной и вторичной обмоток трансформатора 85 между собой.

Таким образом, предлагаемое устройство обеспечивает автоматическую перекоммутацию выводов обмоток транс30 форматора 85 в случае его неправильной установки с перепутьюанием вьгео- дов, что повьшает производительность труда и расширяет функциональные возможности устройства,

35

Формула изобретения

40 электронных блоков, содержащее генератор импульсов, соединенный выходом, с входом усилителя, первый пиковьй , детектор, соединенный выходом с первым входом первого компаратора, вто45 рой и третий -компараторы, неинвертирующие входы которых соединены с соответствующими первой и второй шинами смещения, резистор, соединенный первым вьшодом с общей шиной устройства,

50 вторым выводом - с входом второго пикового детектора, выход которого соединен с первым входом четвертого компаратора, блок индикации, отличающееся тем, что, с целью

55 расширения функциональных возможностей устройства и повьшзения производительности труда, в него введены ком- мутатор, блок перекоммутации, блок памяти, третий пиковый детектор, пя15

тый компаратор, блок защиты, блок управления и кнопка, через замыкающий контакт которой общая шина устройства соединена с первым входом блока управления, первый выход которого соединен с входом блока памяти, первые выходы .блока памяти соединены с первыми входами коммутатора, вторые выходы - с вторыми входаьм четвертого компаратора, третьи выходы - с входами генератора импульсов, четвертые выходы - с вторыми входами первого компаратора, первый вход и выход которого соединены соответственно с инвертирующим входом второго компаратора и вторым входом блока управле- ,ния, второй -выход которого соединен с первым входом блока перекоммутации.

10

15

и шестым входом блока управления, вход блока защиты соединен с третьим выходом блока перекоммутации, выход второго компаратора соединен с седьмым входом блока управления , соединенного пятым выходом с седьмым входом блока перекоммутации.

С Л Л , VJ J JJ. - --j: . - j

второй и третий входы которого соеди- 20 седьмым, третьим и шестым входами

т-1-ттч 5-о1-гот-гт а TSF IvnnDM С И НШ

нены соответственно с выходом усили теля и первым выходом коммутатора, соединенного вторыми входами с клеммами для подключения первых выводов первичньк обмоток контролируемых трансформаторов, третьими входами - с клеммами для подключения вторых выводов первичных обмоток контролируемых трансформаторов, четвертыми вхоблока управления, выходом - с информационным входом первого триггера, соединенного управляющим входом с первым выходом дешифратора, инверти- 25 рующим выходом - с первым входом одного вибратора, прямым выходом - с пятым выходом блока управления и с щестым входом первого преобразователя кодов, соединенного первым выхоМЫХ ТрО-ИСфииМСИ , -11 .- -.

дами -с клеммами для .подключения пер- ЗО Дом с третьим выходом блока управле- вых выводов вторичных обмоток контро- ния, вторыми выходахш - с четвертыми лируемых трансформаторов, пятыми вхо- выходами блока управления, дами - с кл-еммами для подключения- вторых выводов вторичных обмоток

входом - с прямым выходом второго триггера, с вторым выходом блока упВТОиЫЛ ЬЛиЗ гэ 1 w JTi-liii -. -

контролируемых трансформаторов, вто- 35 Р вления и с первым входом первого

. .- „,, ППи ,опын(ННПГО ЗТОПЫМ

рый, третьим и четвертым выходами соответственно - с четвертым, пятым и шестым входами блока перекоммута,- , первый выход которого соединен с входом второго пикового детектора, второй выход - с входом первого пикового детектора непосредственно, а через третий пиковый детектор - с. инвертирующим входом третьего компа40

элемента ИЛИ, соединенного вторым входом с вторым выходом дешифратора и с первым выходом блока управления, выходом - с вторым входом одновибра- тора, соединенного инверсным выходом с первыми информационными входами мультиплексора, соединенного вторым информационным входом с прямым выходом третьего триггера, соединенного

50

инвертирующим i „ ..„„„,,,,«

ратора, соединенного с третьим входом 45 первым установочным входом с первым блока управления, третий и четвертые входом блока управления, вторым уста- выходы которого соединены соответственно с первым и вторыми входами блока индикации, соединенного третьими входами с пятыми выходами блока памяти, соединенного шестым выходом с четвертым входом блока; индикации и с четвертым входом блока управления; соединенного пятым входом с выходом четвертого компаратора, соединенного первым входом с инвертирующим входом пятого компаратора, соединенного не, инвертирующим входом и.выходом соот ветственно с первой шиной смещения

новочным входом - с выходом второго элемента ИЛИ, выходом через формирователь короткого импульса - с установочными входами первого и второго триггеров, первый вход второго элемента ИЛИ соединен с четвертым входом блока управления, второй вход - с выходом первого элемента И, соединенного первым входом с первым выходом первого преобразователя кодов, вторым входом - с третьим выходом дешифратора, соединенного четвертым выходом с управляющим входом второго

1158

10

15

и шестым входом блока управления, вход блока защиты соединен с третьим выходом блока перекоммутации, выход второго компаратора соединен с седьмым входом блока управления , соединенного пятым выходом с седьмым входом блока перекоммутации.

седьмым, третьим и шестым входами

т-1-ттч 5-о1-гот-гт а TSF IvnnDM С И НШ

блока управления, выходом - с информационным входом первого триггера, соединенного управляющим входом с первым выходом дешифратора, инверти- рующим выходом - с первым входом одного вибратора, прямым выходом - с пятым выходом блока управления и с щестым входом первого преобразователя кодов, соединенного первым выхо -.

Дом с третьим выходом блока управле- ния, вторыми выходахш - с четвертыми выходами блока управления,

входом - с прямым выходом второго триггера, с вторым выходом блока упР вления и с первым входом первого

„,, ППи ,опын(ННПГО ЗТОПЫМ

элемента ИЛИ, соединенного вторым входом с вторым выходом дешифратора и с первым выходом блока управления, выходом - с вторым входом одновибра- тора, соединенного инверсным выходом с первыми информационными входами мультиплексора, соединенного вторым информационным входом с прямым выходом третьего триггера, соединенного

„ ..„„„,,,,«

первым установочным входом с первым входом блока управления, вторым уста-

новочным входом - с выходом второго . элемента ИЛИ, выходом через формирователь короткого импульса - с установочными входами первого и второго триггеров, первый вход второго элемента ИЛИ соединен с четвертым входом блока управления, второй вход - с выходом первого элемента И, соединенного первым входом с первым выходом первого преобразователя кодов, вторым входом - с третьим выходом дешифратора, соединенного четвертым выходом с управляющим входом второго

1714

триггера, третий выход дешифратора соединен с установочным входом счетчика, соединенного выходами с адресными входами мультиплексора и с входами дешифратора, счетным входом - с выходом второго элемента И, соединенного первым входом с выходом мультиплексора, вторым входом - Q выходом задающего генератора, информационный вход второго триггера соединен с третьим входом блока управления.

пятого реле и с размыкакщим контактом шестого реле,размыкающий контакт пятого реле и замыкающий контакт шестого реле соединены с общей шиной устройства.

|3в ,tft

4t3

46

фиг.з

С блока 1

016

| Измеритель коэффициента трансформации | 1974 |

|

SU530277A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля электрических параметров импульсных трансформаторов | 1984 |

|

SU1166021A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-04-07—Публикация

1987-07-24—Подача