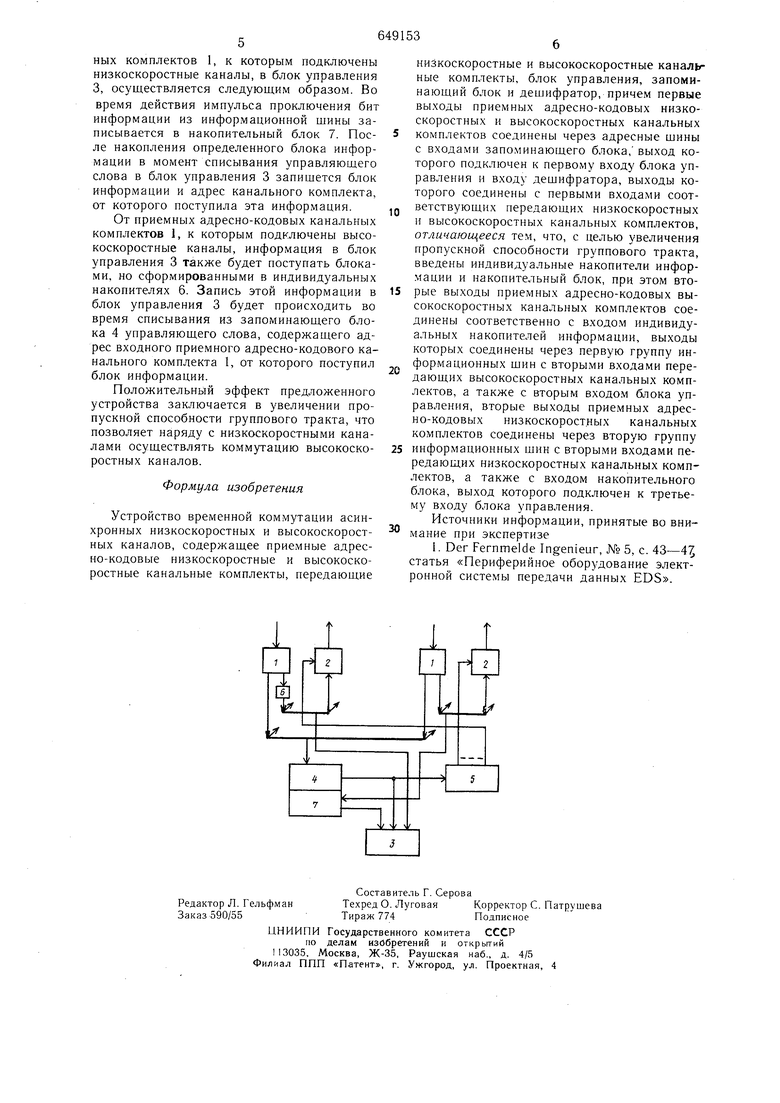

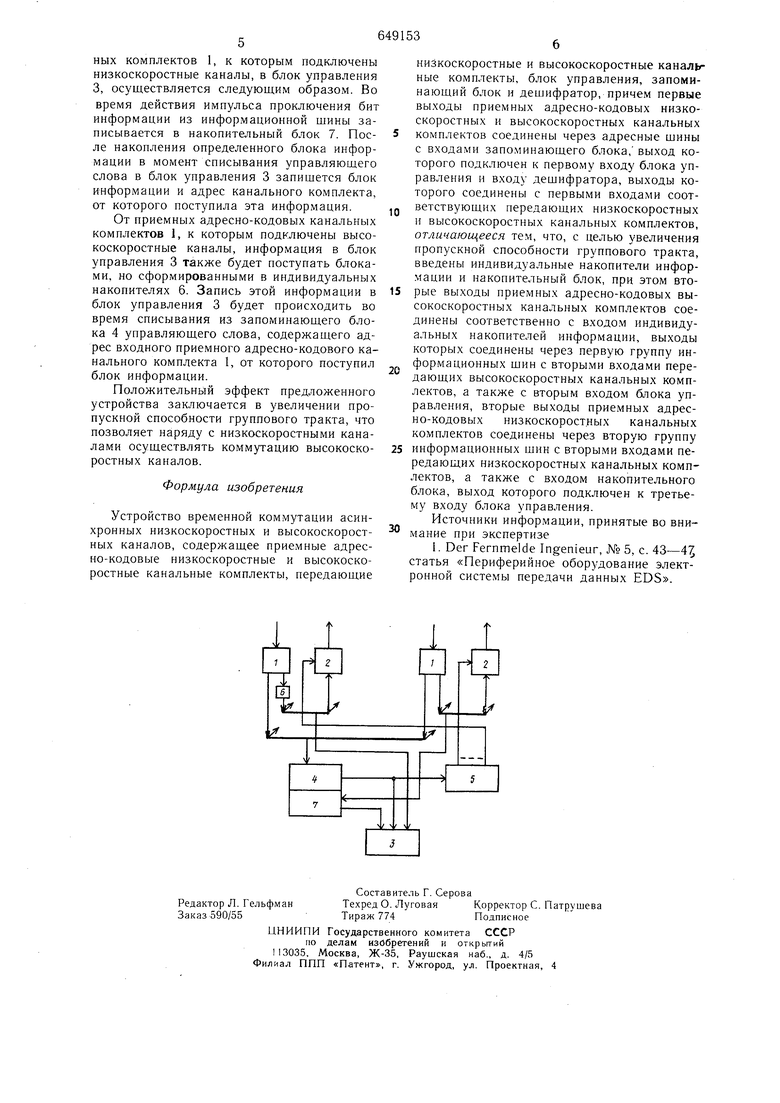

ных комплектов соединены через вторую группу информационных шин с вторыми входами передающих низкоскоростных канальных комплектов, а также с входом накопительного блока, выход которого подключен к третьему входу блока управления. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство временной коммутации асинхронных низкоскоростных и ВЫСОКОСКОрОСТных каналов, содержит приемные адресно-кодовые низкоскоростные и высокоскоростные канальные комплекты 1, передающие низкоскоростные и высокоскоростные канальные комплекты 2, блок управления 3, запоминающий блок 4 и дещифратор 5, причем первые выходы приемных адресно-кодовых низкоскоростных и высокоскоростных канальных комплектов 1 соединены через адресные щины с входами запоминающего блока 4, выход которого подключен к первому входу блока управления 3 -тл входу дещифратора 5, выходы которого соединены с первыми входами соответствующих передающих низкоскоростных и высокоскоростных канальных комплектов 2, индивидуальные накопители 6 информации и накопительный блок 7, при этом вторые выходы приемных адресно-кодовых высокоскоростных канальных комплектов 1 соединены соответственно с входом индивидуальных накопителей 6 информации, выходы которых соединены через первую группу информационных шин с вторыми входами передающих высокоскоростных канальных комплектов 2, а также с вторым входом блока управления 3, вторые выходы приемных адресно-кодовых низкоскоростных канальных комплектов 1 соединены через вторую группу информационных шин с вторыми входами передающих низкоскоростных канальных комплектов 2, а также с входом накопительного блока 7, выход которого подключен к третьему входу блока управления 3. Устройство работает следующим образом. Приемный адресно-кодовый канальный комплект 1 обеспечивает выдачу адреса управляющего слова соответствующего канала в запоминающем блоке 4 на адресную щину, а также бит информации - на индивидуальный накопитель б или информационную щину в соответствии с тем, какой канал подключен к выходному канальному комплекту, высокоскоростной или низкоскоростной. Запоминающий блок 4 содержит управляющие слова канальных комплектов, в которые при установлении соединений записыватотся адреса передающих канальных комплектов 2. Эта информация хранится в запоминающем блоке 4. Управляющее слово также содержит накопленный блок информации, поступивший от приемных адресно-кодовых канальных комплектов 1, к которым подключены низкоскоростные каналы. Эта информация хранится в накопительном блоке 7. Выход запоминающего блока 4 соединен с входом дешифратора 5 управления передающих канальных комплектов 2, который обеспечивает дешифрацию адреса этих комплектов из двоичной системы в десятичную и управляет списыванием информации из передающего канального комплекта 2 в канал. Передающие канальные комплекты 2 обеспечивают преобразование сигналов в требуемую форму для передачи в канал связи. Информационная шина является групповым трактом, по которому в момент действия импульса проключения передаются блоки или биты информации. Адресная шина является групповым трактом, по которому в момент изменения фронта импульса поступающей информации передается адрес приемного адресно-кодового канального комплекта 1. Блок управления 3 осуществляет прием и обработку информации, поступающей по каналам связи, и управляет установлением соединения между приемными адресно-кодовыми канальными комплектами 1 и передающими канальными комплектами 2. Индивидуальный накопитель 6 информации обеспечивает накопление блока информации, например, бита, поступающего от приемного адресно-кодового канального комплекта 1, к которому подключен высокоскоростной канал. Приемный адресно-кодовый канальный комплект 1, к которому подключены низкоскоростные каналы, при появлении на его входе очередного требования (элемента информации) обеспечивает выдачу адреса управляющего слова соответствующего канала в запоминающем блоке 4 на адресную щину, а также считывает бит информации в информационную шину. При появлении на адресной шине кодовой комбинации из запоминающего блока 4 под воздействием импульса проключения считывается управляющее слово, содержащее адрес передающего канального комплекта 2, к которому подключен низкоскоростной канал. После дешифрации .адреса в дешифраторе 5 на управляющие входы передающих канальных комплектов 2 поступает сигнал, обеспечивающий списывание информации в канал связи, при этом биты преобразуются в сигналы требуемой формы. Процесс коммутации высокоскоростных каналов отличается тем, что в индивидуальном накопителе 6 происходит накопление определенного блока информации, а по информационной щине передается не бит, а блок информации. Процесс передачи информации, поступающей от приемных адресно-кодовых каналь

| название | год | авторы | номер документа |

|---|---|---|---|

| Канальное устройство объединенного коммутатора каналов и сообщений | 1975 |

|

SU531295A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Временной коммутатор асинхронныхиМпульСНыХ СигНАлОВ | 1979 |

|

SU809629A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство временной коммутации асинхронных импульсных каналов | 1975 |

|

SU581593A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| СИСТЕМА СВЯЗИ, НАПРИМЕР ТЕЛЕФОННОЙ, С ЦЕНТРАЛЬНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU428620A3 |

| Цифровое коммутационное устройство | 1985 |

|

SU1378088A1 |

| Устройство для временной коммутации асинхронных импульсных каналов | 1976 |

|

SU566382A1 |

Авторы

Даты

1979-02-25—Публикация

1976-06-07—Подача