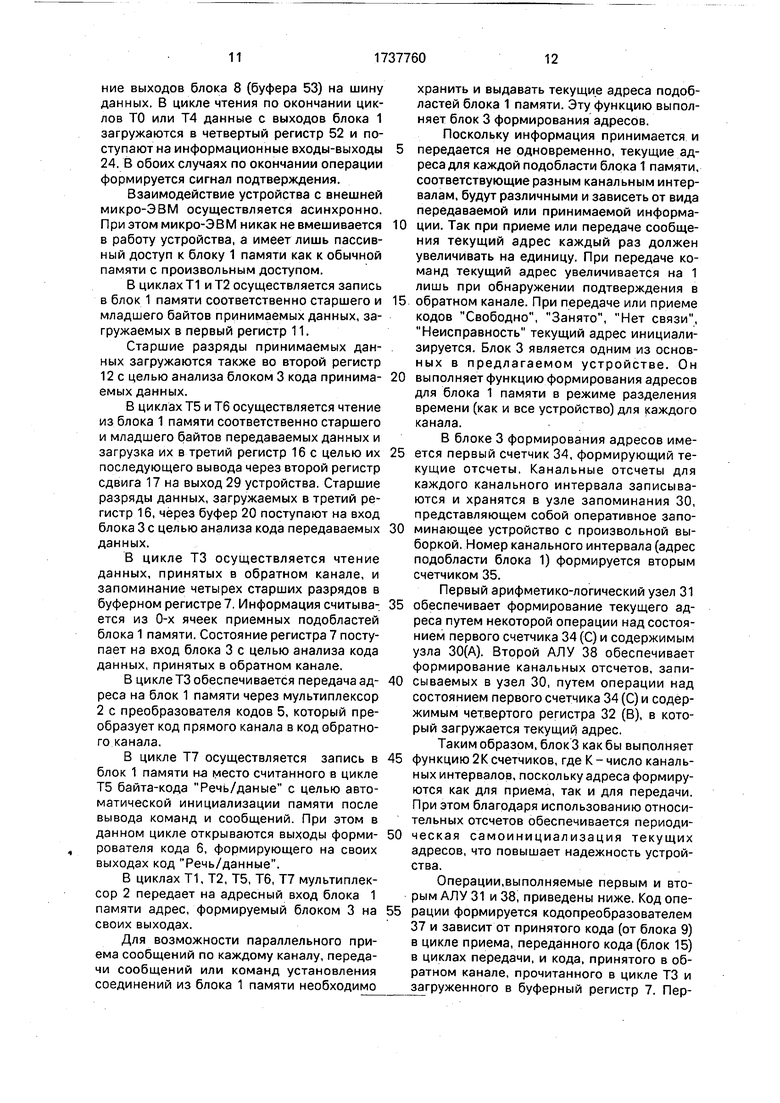

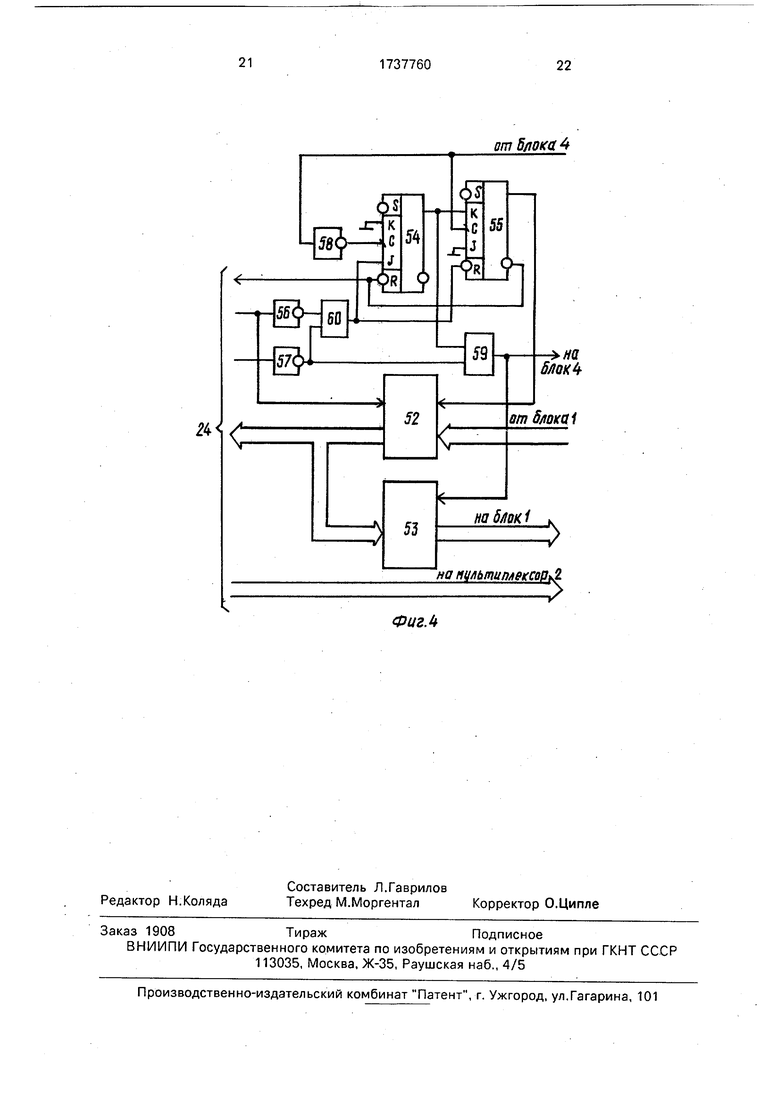

вход 26 тактовой синхронизации, первые информационные входы 27, вторые информационные входы 28, информационные выходы 29.

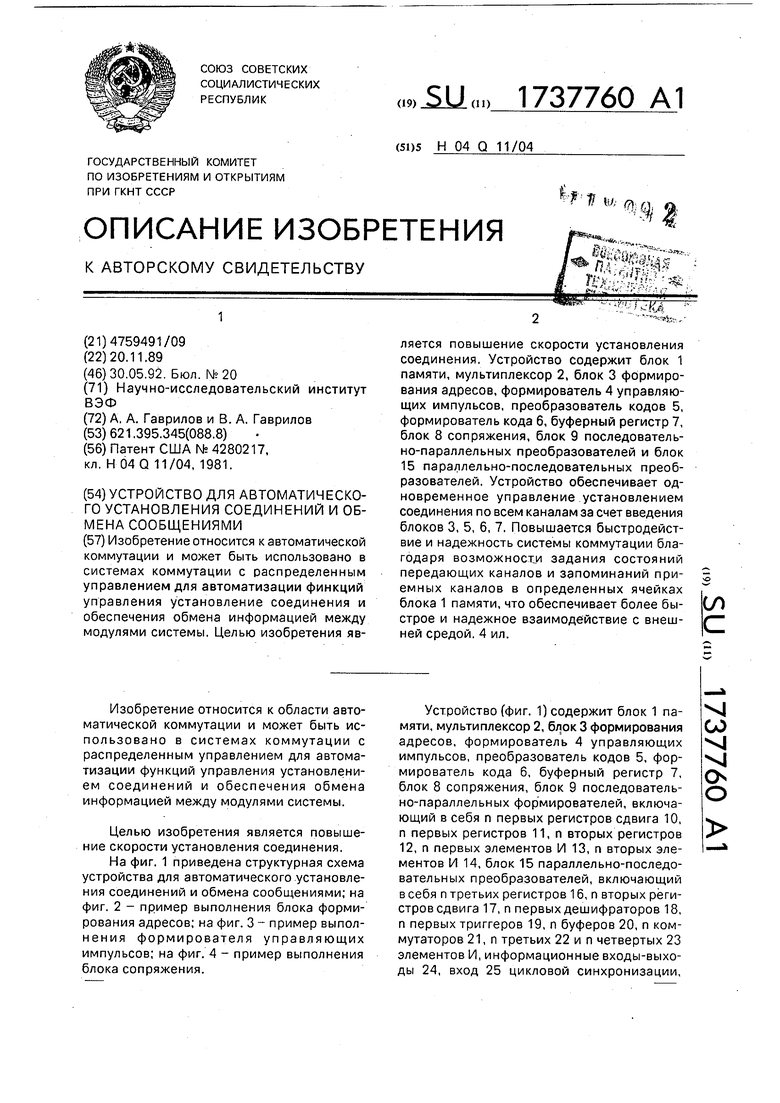

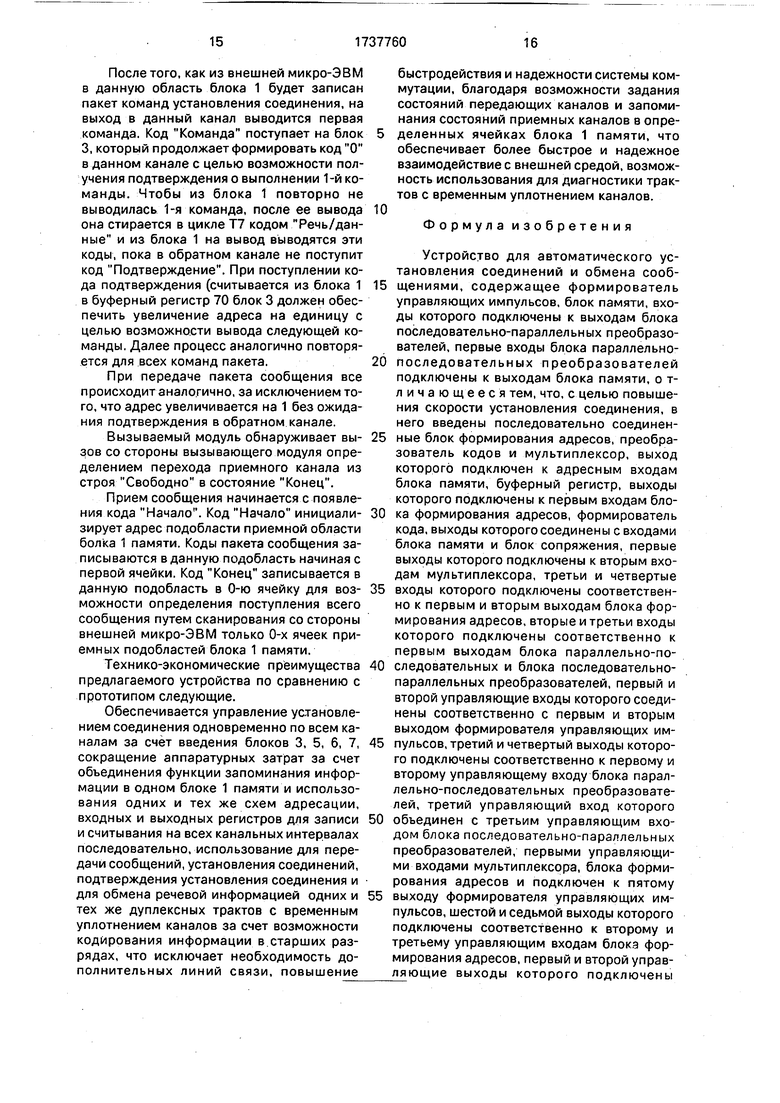

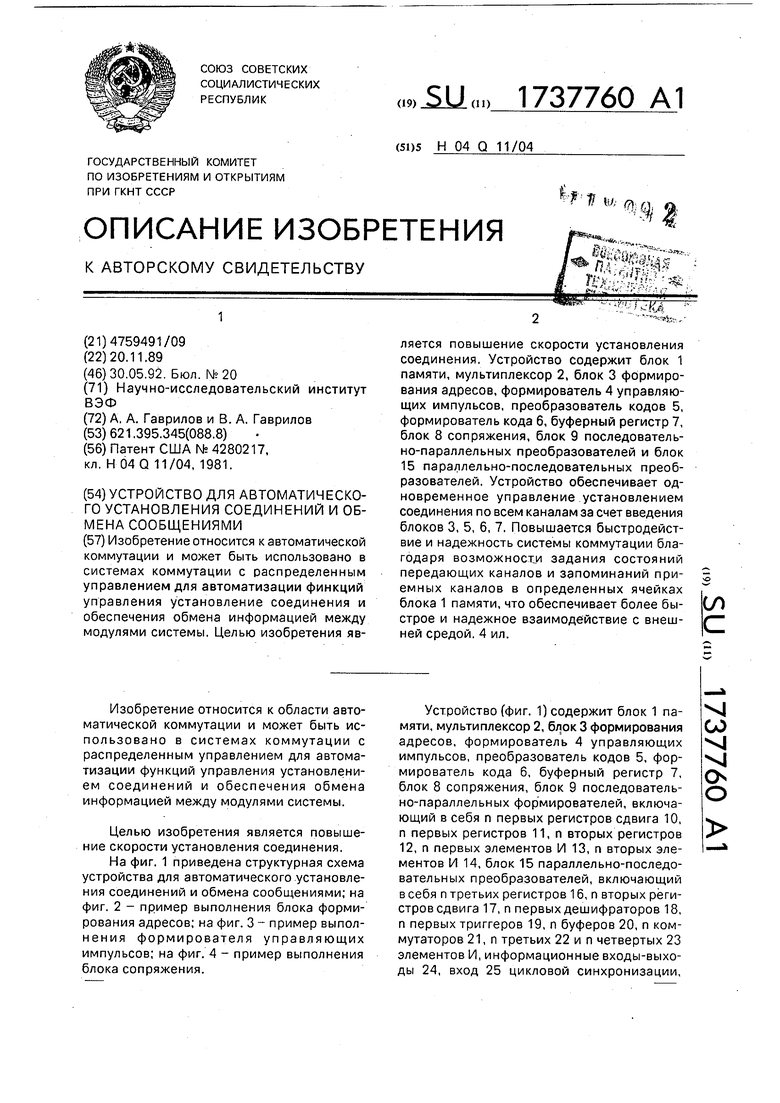

Блок 3 формирования адресов (фиг. 2) содержит узел 30 запоминания, первый арифметико-логический узел (АЛУ) 31, четвертый регистр 32, пятый элемент И 33, первый 34 и второй 35 счетчики, формирователь 36, кодопреобразователь 37, второй ариф- метико-логический узел (АЛУ) 38.

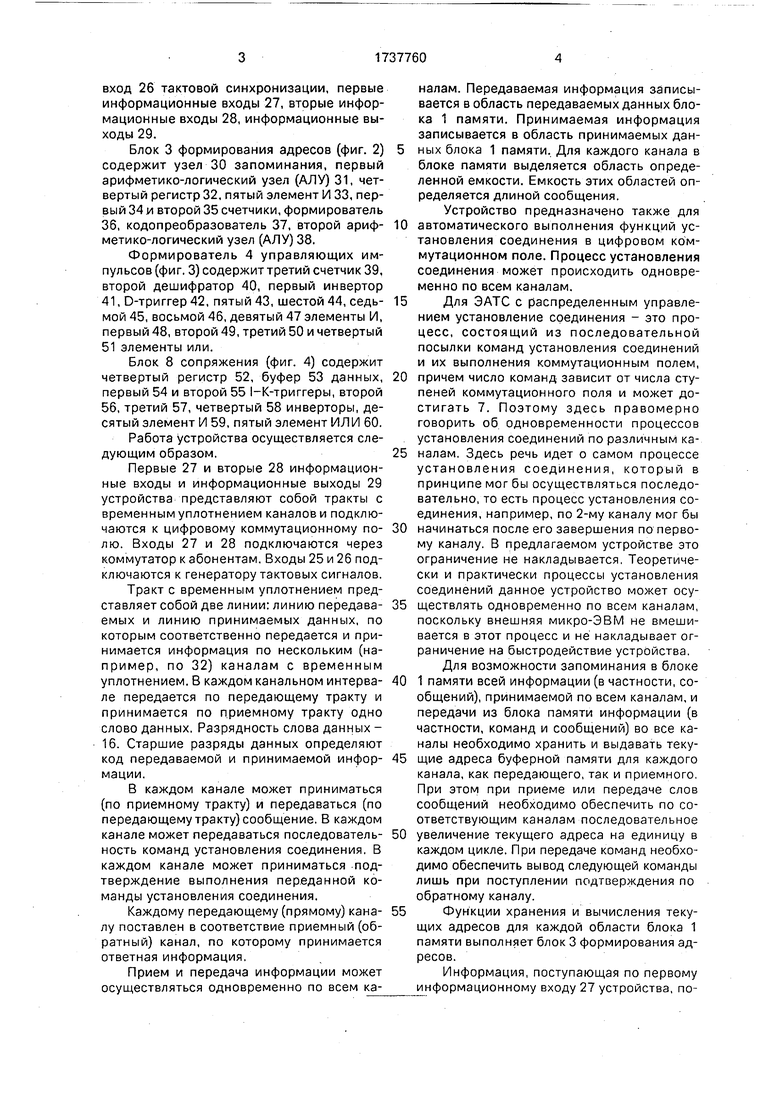

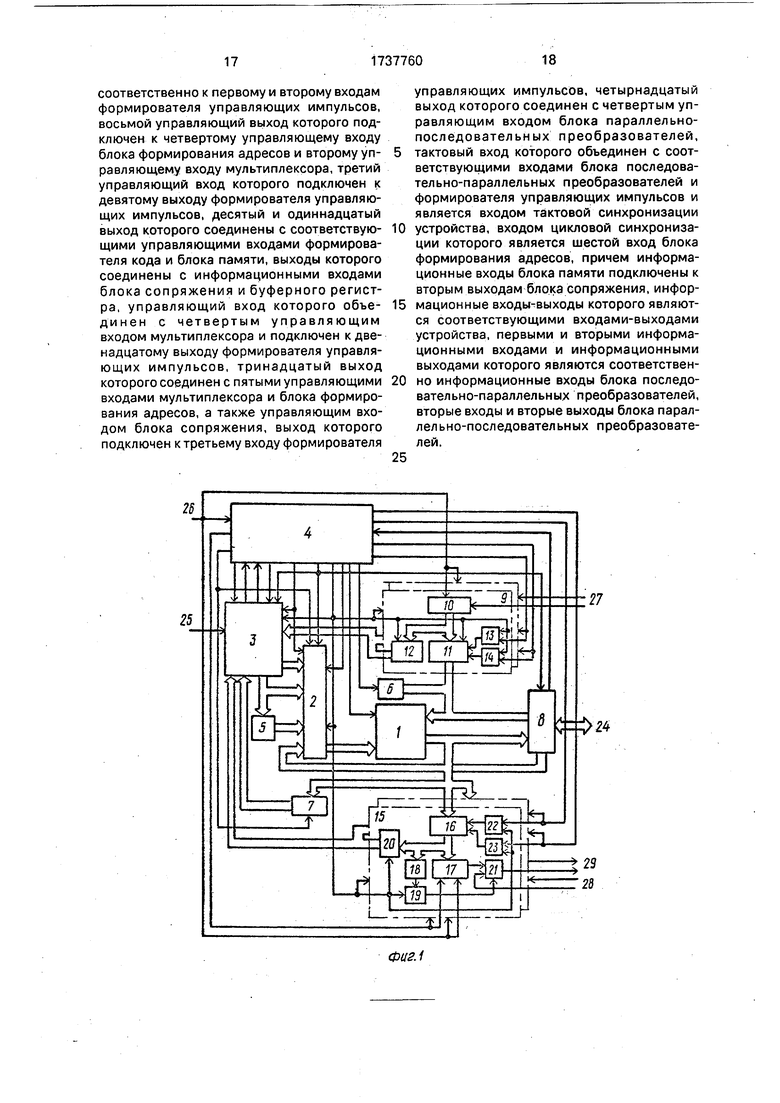

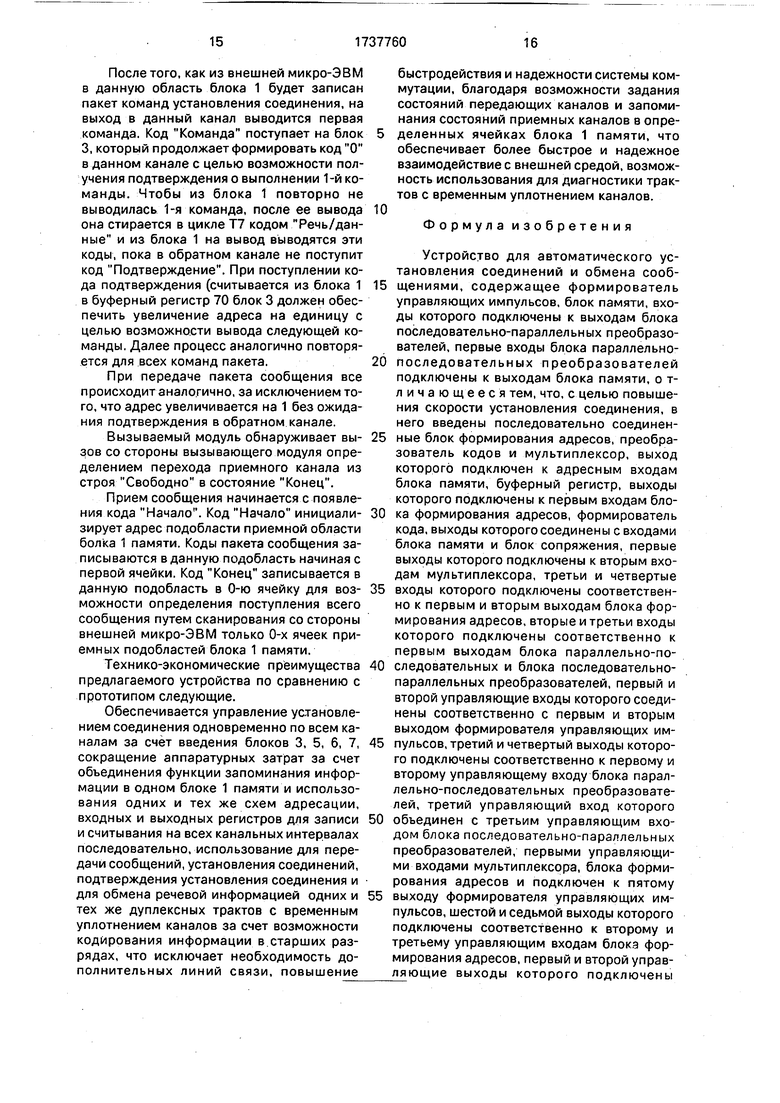

Формирователь 4 управляющих импульсов (фиг. 3) содержит третий счетчик 39, второй дешифратор 40, первый инвертор 41, D-триггер 42, пятый 43, шестой 44, седь- мой 45, восьмой 46, девятый 47 элементы И, первый 48, второй 49, третий 50 и четвертый 51 элементы или.

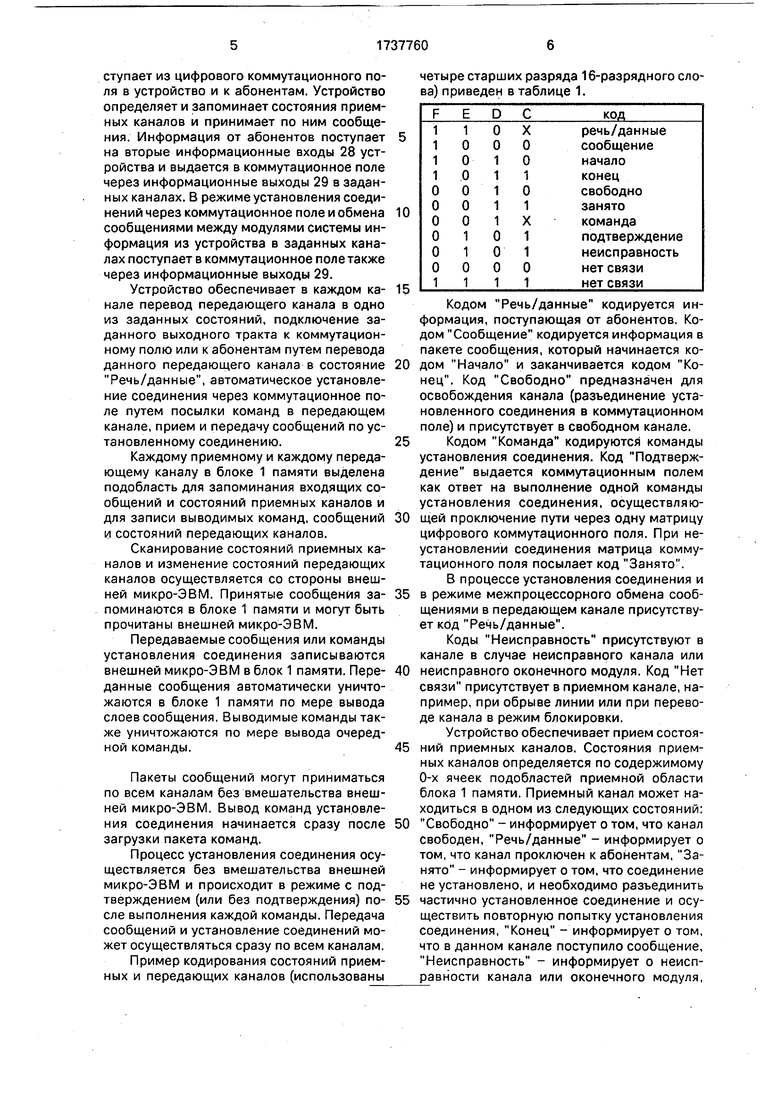

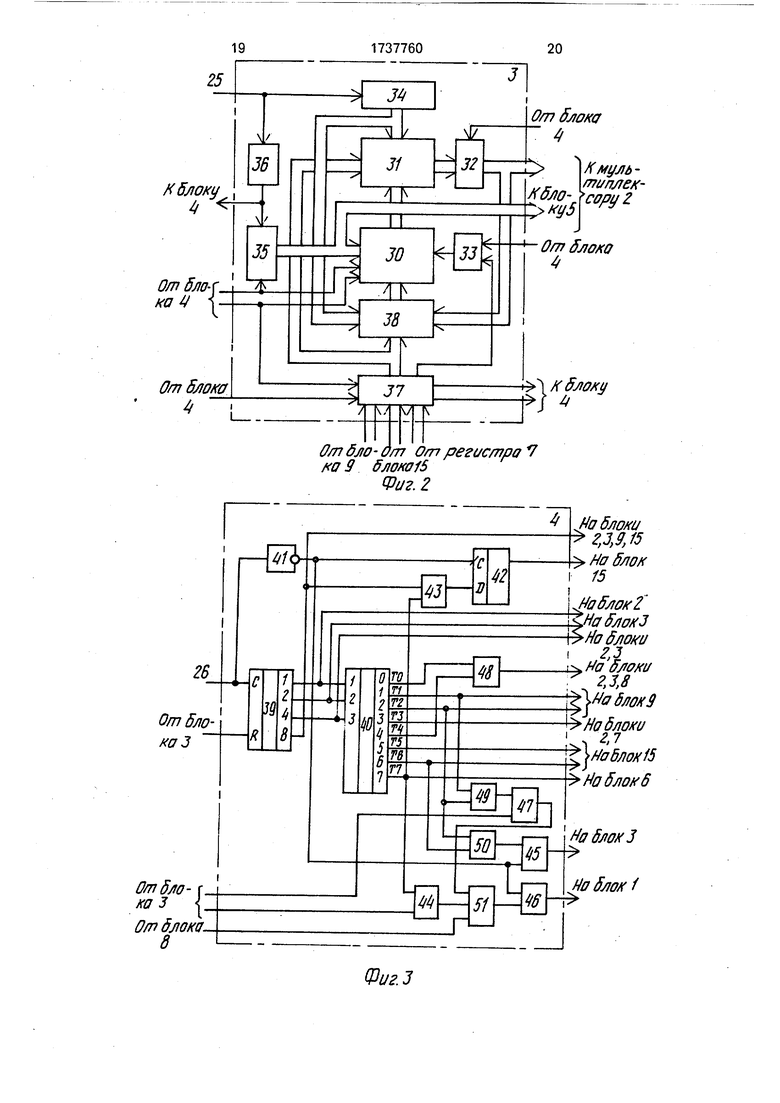

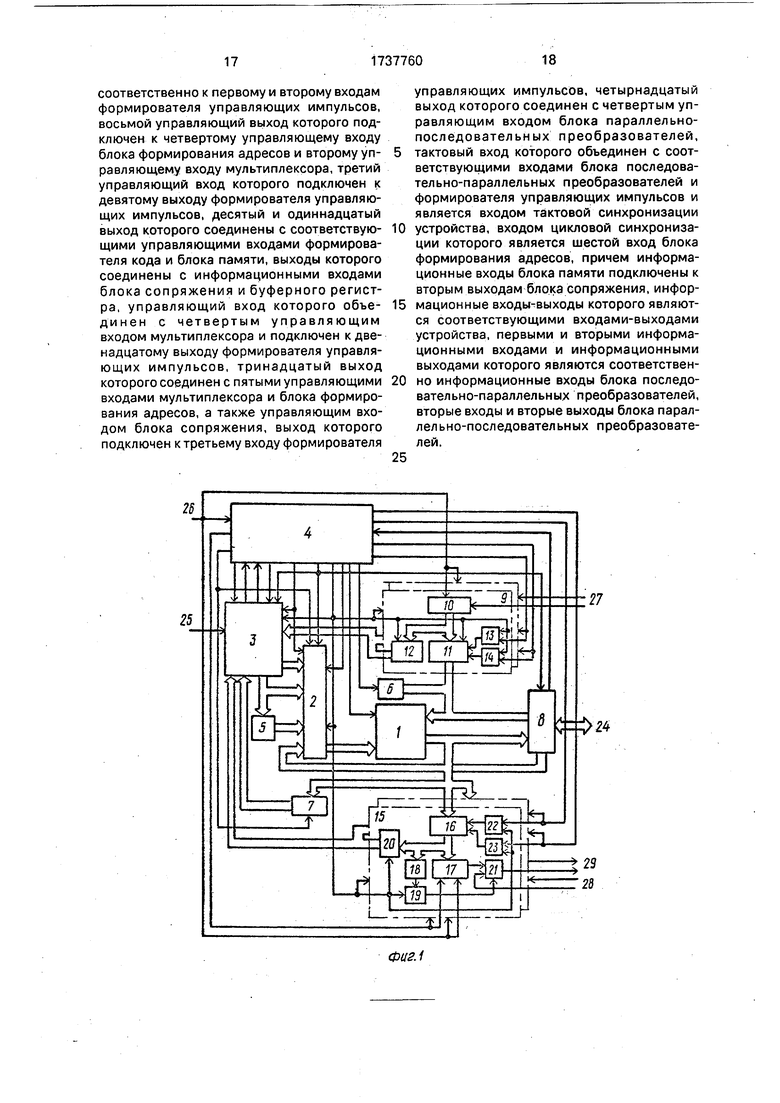

Блок 8 сопряжения (фиг. 4) содержит четвертый регистр 52, буфер 53 данных, первый 54 и второй 55 l-К-триггеры, второй 56, третий 57, четвертый 58 инверторы, десятый элемент И 59, пятый элемент ИЛИ 60.

Работа устройства осуществляется следующим образом.

Первые 27 и вторые 28 информационные входы и информационные выходы 29 устройства представляют собой тракты с временным уплотнением каналов и подключаются к цифровому коммутационному по- лю. Входы 27 и 28 подключаются через коммутатор к абонентам. Входы 25 и 26 подключаются к генератору тактовых сигналов.

Тракт с временным уплотнением представляет собой две линии: линию передава- емых и линию принимаемых данных, по которым соответственно передается и принимается информация по нескольким (например, по 32) каналам с временным уплотнением. В каждом канальном интерва- ле передается по передающему тракту и принимается по приемному тракту одно слово данных. Разрядность слова данных - 16. Старшие разряды данных определяют код передаваемой и принимаемой инфор- мации.

В каждом канале может приниматься (по приемному тракту) и передаваться (по передающему тракту) сообщение. В каждом канале может передаваться последователь- ность команд установления соединения. В каждом канале может приниматься подтверждение выполнения переданной команды установления соединения.

Каждому передающему (прямому) кана- лу поставлен в соответствие приемный (обратный) канал, по которому принимается ответная информация.

Прием и передача информации может осуществляться одновременно по всем каналам. Передаваемая информация записывается в область передаваемых данных блока 1 памяти. Принимаемая информация записывается в область принимаемых данных блока 1 памяти. Для каждого канала в блоке памяти выделяется область определенной емкости. Емкость этих областей определяется длиной сообщения.

Устройство предназначено также для автоматического выполнения функций установления соединения в цифровом коммутационном поле. Процесс установления соединения может происходить одновременно по всем каналам.

Для ЭАТС с распределенным управлением установление соединения - это процесс, состоящий из последовательной посылки команд установления соединений и их выполнения коммутационным полем, причем число команд зависит от числа ступеней коммутационного поля и может достигать 7. Поэтому здесь правомерно говорить об одновременности процессов установления соединений по различным каналам. Здесь речь идет о самом процессе установления соединения, который в принципе мог бы осуществляться последовательно, то есть процесс установления соединения, например, по 2-му каналу мог бы начинаться после его завершения по первому каналу. В предлагаемом устройстве это ограничение не накладывается, Теоретически и практически процессы установления соединений данное устройство может осуществлять одновременно по всем каналам, поскольку внешняя микро-ЭВМ не вмешивается в этот процесс и не накладывает ограничение на быстродействие устройства.

Для возможности запоминания в блоке 1 памяти всей информации (в частности, сообщений), принимаемой по всем каналам, и передачи из блока памяти информации (в частности, команд и сообщений) во все каналы необходимо хранить и выдавать текущие адреса буферной памяти для каждого канала, как передающего, так и приемного. При этом при приеме или передаче слов сообщений необходимо обеспечить по соответствующим каналам последовательное увеличение текущего адреса на единицу в каждом цикле. При передаче команд необходимо обеспечить вывод следующей команды лишь при поступлении подтверждения по обратному каналу.

Функции хранения и вычисления текущих адресов для каждой области блока 1 памяти выполняет блок 3 формирования адресов.

Информация, поступающая по первому информационному входу 27 устройства, поступает из цифрового коммутационного поля в устройство и к абонентам. Устройство определяет и запоминает состояния приемных каналов и принимает по ним сообщения. Информация от абонентов поступает на вторые информационные входы 28 устройства и выдается в коммутационное поле через информационные выходы 29 в заданных каналах. В режиме установления соединений через коммутационное поле и обмена сообщениями между модулями системы информация из устройства в заданных каналах поступает в коммутационное поле также через информационные выходы 29.

Устройство обеспечивает в каждом ка- нале перевод передающего канала в одно из заданных состояний, подключение заданного выходного тракта к коммутационному полю или к абонентам путем перевода данного передающего канала в состояние Речь/данные, автоматическое установление соединения через коммутационное поле путем посылки команд в передающем канале, прием и передачу сообщений по установленному соединению.

Каждому приемному и каждому передающему каналу в блоке 1 памяти выделена подобласть для запоминания входящих сообщений и состояний приемных каналов и для записи выводимых команд, сообщений и состояний передающих каналов.

Сканирование состояний приемных каналов и изменение состояний передающих каналов осуществляется со стороны внешней микро-ЭВМ. Принятые сообщения за- поминаются в блоке 1 памяти и могут быть прочитаны внешней микро-ЭВМ.

Передаваемые сообщения или команды установления соединения записываются внешней микро-ЭВМ в блок 1 памяти. Пере- данные сообщения автоматически уничтожаются в блоке 1 памяти по мере вывода слоев сообщения. Выводимые команды также уничтожаются по мере вывода очередной команды.

Пакеты сообщений могут приниматься по всем каналам без вмешательства внешней микро-ЭВМ. Вывод команд установления соединения начинается сразу после загрузки пакета команд.

Процесс установления соединения осуществляется без вмешательства внешней микро-ЭВМ и происходит в режиме с подтверждением (или без подтверждения) по- еле выполнения каждой команды. Передача сообщений и установление соединений может осуществляться сразу по всем каналам.

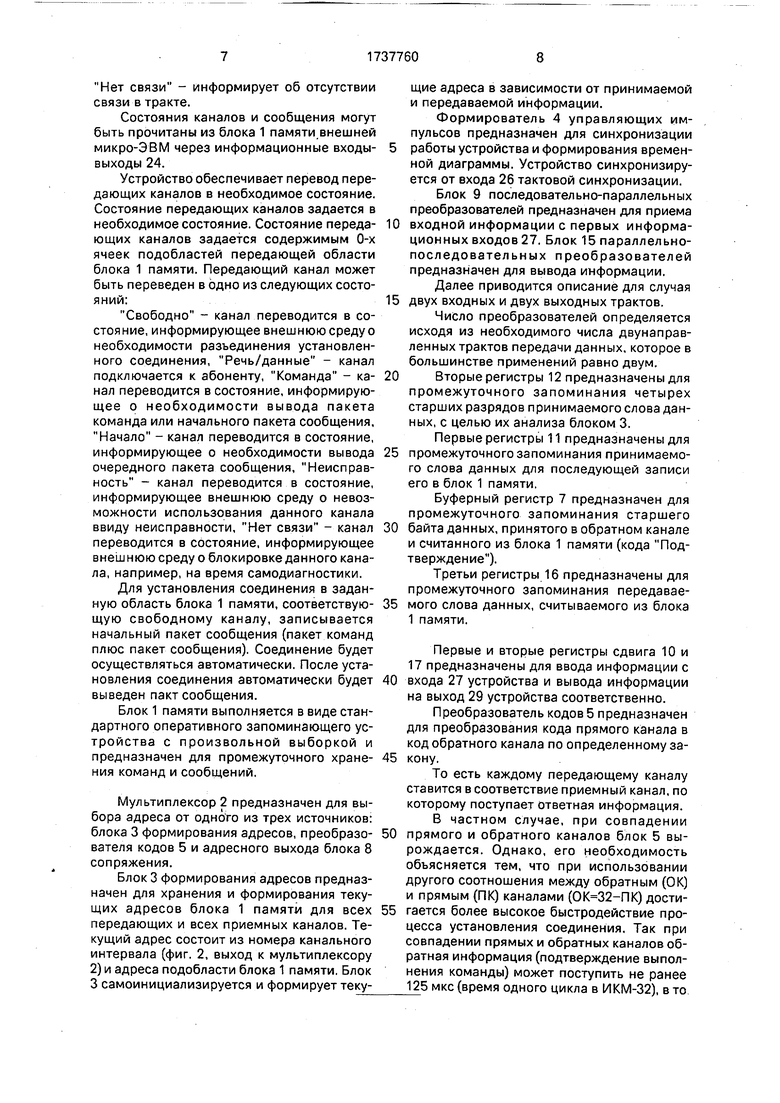

Пример кодирования состояний приемных и передающих каналов (использованы

четыре старших разряда 16-разрядного слова) приведен в таблице 1.

Кодом Речь/даиные кодируется информация, поступающая от абонентов. Кодом Сообщение кодируется информация в пакете сообщения, который начинается кодом Начало и заканчивается кодом Конец. Код Свободно предназначен для освобождения канала (разъединение установленного соединения в коммутационном поле) и присутствует в свободном канале.

Кодом Команда кодируются команды установления соединения. Код Подтверждение выдается коммутационным полем как ответ на выполнение одной команды установления соединения, осуществляющей проключение пути через одну матрицу цифрового коммутационного поля. При неустановлении соединения матрица коммутационного поля посылает код Занято.

В процессе установления соединения и в режиме межпроцессорного обмена сообщениями в передающем канале присутствует код Речь/данные.

Коды Неисправность присутствуют в канале в случае неисправного канала или неисправного оконечного модуля. Код Нет связи присутствует в приемном канале, например, при обрыве линии или при переводе канала в режим блокировки.

Устройство обеспечивает прием состояний приемных каналов. Состояния приемных каналов определяется по содержимому 0-х ячеек подобластей приемной области блока 1 памяти. Приемный канал может находиться в одном из следующих состояний: Свободно - информирует о том, что канал свободен, Речь/данные - информирует о том, что канал проключен к абонентам, Занято - информирует о том, что соединение не установлено, и необходимо разъединить частично установленное соединение и осуществить повторную попытку установления соединения, Конец - информирует о том, что в данном канале поступило сообщение, Неисправность - информирует о неисправности канала или оконечного модуля,

Нет связи - информирует об отсутствии связи в тракте.

Состояния каналов и сообщения могут быть прочитаны из блока 1 памяти внешней микро-ЭВМ через информационные входы- выходы 24.

Устройство обеспечивает перевод передающих каналов в необходимое состояние. Состояние передающих каналов задается в необходимое состояние. Состояние передающих каналов задается содержимым 0-х ячеек подобластей передающей области блока 1 памяти. Передающий канал может быть переведен в одно из следующих состояний:

Свободно - канал переводится в состояние, информирующее внешнюю среду о необходимости разъединения установленного соединения, Речь/данные - канал подключается к абоненту, Команда - канал переводится в состояние, информирующее о необходимости вывода пакета команда или начального пакета сообщения, Начало - канал переводится в состояние, информирующее о необходимости вывода очередного пакета сообщения, Неисправность - канал переводится в состояние, информирующее внешнюю среду о невозможности использования данного канала ввиду неисправности, Нет связи - канал переводится в состояние, информирующее внешнюю среду о блокировке данного канала, например, на время самодиагностики.

Для установления соединения в заданную область блока 1 памяти, соответствующую свободному каналу, записывается начальный пакет сообщения (пакет команд плюс пакет сообщения). Соединение будет осуществляться автоматически. После установления соединения автоматически будет выведен пакт сообщения.

Блок 1 памяти выполняется в виде стандартного оперативного запоминающего устройства с произвольной выборкой и предназначен для промежуточного хранения команд и сообщений.

Мультиплексор 2 предназначен для выбора адреса от одного из трех источников: блока 3 формирования адресов, преобразователя кодов 5 и адресного выхода блока 8 сопряжения.

Блок 3 формирования адресов предназначен для хранения и формирования текущих адресов блока 1 памяти для всех передающих и всех приемных каналов. Текущий адрес состоит из номера канального интервала (фиг. 2, выход к мультиплексору 2) и адреса подобласти блока 1 памяти. Блок 3 самоинициализируется и формирует текущие адреса в зависимости от принимаемой и передаваемой информации.

Формирователь 4 управляющих импульсов предназначен для синхронизации

работы устройства и формирования временной диаграммы. Устройство синхронизируется от входа 26 тактовой синхронизации.

Блок 9 последовательно-параллельных преобразователей предназначен для приема

входной информации с первых информационных входов 27. Блок 15 параллельно- последовательных преобразователей предназначен для вывода информации. Далее приводится описание для случая

двух входных и двух выходных трактов.

Число преобразователей определяется исходя из необходимого числа двунаправленных трактов передачи данных, которое в большинстве применений равно двум.

Вторые регистры 12 предназначены для промежуточного запоминания четырех старших разрядов принимаемого слова данных, с целью их анализа блоком 3.

Первые регистры 11 предназначены для

промежуточного запоминания принимаемого слова данных для последующей записи его в блок 1 памяти.

Буферный регистр 7 предназначен для промежуточного запоминания старшего

байта данных, принятого в обратном канале и считанного из блока 1 памяти (кода Подтверждение).

Третьи регистры 16 предназначены для промежуточного запоминания передаваемого слова данных, считываемого из блока 1 памяти.

Первые и вторые регистры сдвига 10 и 17 предназначены для ввода информации с

входа 27 устройства и вывода информации на выход 29 устройства соответственно.

Преобразователь кодов 5 предназначен для преобразования кода прямого канала в код обратного канала по определенному закону.

То есть каждому передающему каналу ставится в соответствие приемный канал, по которому поступает ответная информация. В частном случае, при совпадении

прямого и обратного каналов блок 5 вырождается. Однако, его необходимость объясняется тем, что при использовании другого соотношения между обратным (ОК) и прямым (ПК) каналами (ОК 32-ПК) достигается более высокое быстродействие процесса установления соединения. Так при совпадении прямых и обратных каналов обратная информация (подтверждение выполнения команды) может поступить не ранее 125 мкс (время одного цикла в ИКМ-32), в то

время как в других случаях это время сокращается.

Код прямого канала (выход блока 3) и код обратного канала (выход блока 5) поступают на мультиплексор 2 и через него на часть адресных входов блока 1 памяти. На адресные входы блока 1 памяти в цикле ТЗ (выход блока 4) поступает код обратного канала, в циклах ТО и Т4 - адрес с блока 9, и код прямого канала - в остальных циклах.

Преобразователь кодов 5 реализуется на ПЗУ.

Формирователь кодов 6 предназначен для формирования определенного кода (Речь-данные) для записи в блок 1 памяти на место переданных кодов Команда, Начало, Подтверждение.

Блок 8 сопряжения предназначен для сопряжения с внешней микро-ЭВМ через шину, представляющую собой общую магистраль (общую шину), и обеспечивает доступ внешней микро-ЭВМ к блоку 1 памяти как по записи, так и по чтению. Сопряжение через общую шину осуществляется стандартным образом.

Коммутаторы 21 предназначены для коммутации информации на информационные выходы 29 либо с вторых информационных входов 28, либо с вторых регистров сдвига 17 для возможности вывода служебной информации, поступающей из блока 1 памяти. Из памяти на информационные выходы 29 выводится только служебная информация.

Устройство работает полностью синхронно. Синхронизация поступления служебной информации достигается тем, что прежде чем осуществить коммутацию, слово из блока 1 считывается в регистр и дешифрируются его старшие биты. Это происходит в канальном интервале, предшествующем тому, в котором это слово должно быть выведено. Таким образом, информация о том, что будет выводиться служебное слово, известна заранее и не представляет труда вовремя (при переходе из данного к следующему канальному интервалу) переключить соответствующий коммутатор 21 сигналом с первого триггера 19. Триггер 19 включается при обнаружении первым дешифратором 18 кода Речь/данные.

Вход 25 является входом цикловой синхронизации (частотой 8 кГц) и предназначен для синхронизации 0-го канального интервала. По перепаду 0-1 сигнала цикловой синхронизации блок 3 формирует сигнал сброса, поступающий на вход блока 4.

Вход 26 является входом тактовой синхронизации битов данных трактов с временным уплотнением каналов.

Область адресации блока 1 памяти разделена на области передаваемых и принимаемых данных. Как приемная, так и передающая области разбиты на 64 подобласти. Каждой подобласти поставлен в соответствие один из 64-х каналов (два тракта). В каждом канальном интервале осуществляется чтение передаваемых и запись принимаемых данных соответствующего

0 канала.

Формирователь 4 управляющих импульсов в каждом канальном интервале формирует 8 циклов (ТО, Т1, ... Т7) обращения к блоку 1 памяти. Временная диаграмма

5 формируется на базе третьего счетчика 39 и второго дешифратора 40. Инициализация третьего счетчика 39 осуществляется сигналом, формируемым формирователем 36 блока 3 по перепаду 0-1 сигнала 25 цикловой

0 синхронизации. Третий счетчик 39 изменяет свое состояние по перепаду 0-1 сигнала 26 тактовой синхронизации. Элементы 41-51 формируют управляющие сигналы. С выхода последнего разряда третьего счетчика 39

5 блока 4 снимается сигнал канальной синхронизации, поступающий на счетный вход второго счетчика 35 блока 3, формирующего номера канальных интервалов.

Поскольку блоки 6, 8 и первые регистры

0 11 включены встречно друг другу на шину данных блока 1 памяти, необходимы раздельные сигналы управления, переводящие эти блоки в режим подключения (отключения) своих выходов. Поэтому формирова5 тель 4 вырабатывает эти сигналы в соответствующие интервалы времени.

Работу устройства достаточно рассмотреть для одного канального интервала, поскольку в остальных канальных интервалах

0 устройство работает аналогично.

Работа устройства сведена к периодическому выполнению восьми циклов и зависит лишь от информации, принимаемой и передаваемой в данном канальном интер5 вале.

В циклах ТО и Т4 разрешен доступ к блоку 1 памяти от внешней микро-ЭВМ через информационные входы-выходы 24. Доступ осуществляется через блок 8 сопря0 жения. Управляющий сигнал с блока 4 разрешает передачу через мультиплексор 2 адреса через блок 8.

Наличие сигнала записи или чтения от микро-ЭВМ (1 на входе 1-К-триггера 54,

5 фиг. 4) вызывает включение данного триггера 54 в начале цикла ТО или Т4. В цикле записи при этом на соответствующем выходе блока 8 появляется сигнал записи, который через блок 4 поступает на вход записи блока 1. Этот же сигнал вызывает подключение выходов блока 8 (буфера 53) на шину данных. В цикле чтения по окончании циклов ТО или Т4 данные с выходов блока 1 загружаются в четвертый регистр 52 и поступают на информационные входы-выходы 24. В обоих случаях по окончании операции формируется сигнал подтверждения.

Взаимодействие устройства с внешней микро-ЭВМ осуществляется асинхронно. При этом микро-ЭВМ никак не вмешивается в работу устройства, а имеет лишь пассивный доступ к блоку 1 памяти как к обычной памяти с произвольным доступом.

В циклах Т1 иТ2 осуществляется запись в блок 1 памяти соответственно старшего и младшего байтов принимаемых данных, загружаемых в первый регистр 11.

Старшие разряды принимаемых данных загружаются также во второй регистр 12 с целью анализа блоком 3 кода принимаемых данных.

В циклах Т5 и Т6 осуществляется чтение из блока 1 памяти соответственно старшего и младшего байтов передаваемых данных и загрузка их в третий регистр 16с целью их последующего вывода через второй регистр сдвига 17 на выход 29 устройства. Старшие разряды данных, загружаемых в третий регистр 16, через буфер 20 поступают на вход блока 3 с целью анализа кода передаваемых данных.

В цикле ТЗ осуществляется чтение данных, принятых в обратном канале, и запоминание четырех старших разрядов в буферном регистре 7. Информация считывается из 0-х ячеек приемных подобластей блока 1 памяти. Состояние регистра 7 поступает на вход блока 3 с целью анализа кода данных, принятых в обратном канале.

В цикле ТЗ обеспечивается передача адреса на блок 1 памяти через мультиплексор 2 с преобразователя кодов 5, который преобразует код прямого канала в код обратного канала.

В цикле Т7 осуществляется запись в блок 1 памяти на место считанного в цикле Т5 байта-кода Речь/даные с целью автоматической инициализации памяти после вывода команд и сообщений. При этом в данном цикле открываются выходы формирователя кода 6, формирующего на своих выходах код Речь/данные.

В циклах Т1, Т2, Т5, Т6, Т7 мультиплексор 2 передает на адресный вход блока 1 памяти адрес, формируемый блоком 3 на своих выходах.

Для возможности параллельного приема сообщений по каждому каналу, передачи сообщений или команд установления соединений из блока 1 памяти необходимо

хранить и выдавать текущие адреса подобластей блока 1 памяти. Эту функцию выполняет блок 3 формирования адресов.

Поскольку информация принимается и

5 передается не одновременно, текущие адреса для каждой подобласти блока 1 памяти, соответствующие разным канальным интервалам, будут различными и зависеть от вида передаваемой или принимаемой информа0 ции. Так при приеме или передаче сообщения текущий адрес каждый раз должен увеличивать на единицу. При передаче команд текущий адрес увеличивается на 1 лишь при обнаружении подтверждения в

5 обратном канале. При передаче или приеме кодов Свободно, Занято, Нет связи, Неисправность текущий адрес инициализируется. Блок 3 является одним из основных в предлагаемом устройстве. Он

0 выполняет функцию формирования адресов для блока 1 памяти в режиме разделения времени (как и все устройство) для каждого канала.

В блоке 3 формирования адресов име5 ется первый счетчик 34, формирующий текущие отсчеты. Канальные отсчеты для каждого канального интервала записываются и хранятся в узле запоминания 30, представляющем собой оперативное запо0 минающее устройство с произвольной выборкой. Номер канального интервала (адрес подобласти блока 1) формируется вторым счетчиком 35.

Первый арифметико-логический узел 31

5 обеспечивает формирование текущего адреса путем некоторой операции над состоянием первого счетчика 34 (С) и содержимым узла 30(А). Второй АЛУ 38 обеспечивает формирование канальных отсчетов, запи0 сываемых в узел 30, путем операции над состоянием первого счетчика 34 (С) и содержимым четвертого регистра 32 (В), в который загружается текущий адрес.

Таким образом, блок 3 как бы выполняет

5 функцию 2К счетчиков, где К - число канальных интервалов, поскольку адреса формируются как для приема, так и для передачи. При этом благодаря использованию относительных отсчетов обеспечивается периоди0 ческая самоинициализация текущих адресов, что повышает надежность устройства.

Операции,выполняемые первым и вторым АЛУ 31 и 38, приведены ниже. Код опе5 рации формируется кодопреобразователем 37 и зависит от принятого кода (от блока 9) в цикле приема, переданного кода (блок 15) в циклах передачи, и кода, принятого в обратном канале, прочитанного в цикле ТЗ и

загруженного в буферный регистр 7. Первый АЛУ 31 вычисляет значение текущего адреса для блока 1. Второй АЛУ 38 вычисляет код, записываемый в узел 30.

В цикле ТО организованы цикл чтения узла 30 запоминания и загрузка в четвертый регистр 32 результата операции первого АЛУ 31: С-А - если принят код Сообщение (вывод адреса, увеличенного на единицу), С-А-1 - если принят код Речь/данные (вывод текущего адреса), О-в остальных случаях (установка 0-го адреса).

В цикле Т2 организован цикл записи в узел 30 результата операции второго АЛУ 38: С-В - если принят код Речь/данные или Сообщение (сохранение текущего адреса), С - в остальных случаях (инициализация текущего адреса).

В цикле Т4 организованы цикл чтения узла 30 и загрузка в четвертый регистр 32 результата операции первого АЛУ 31: С-В - если в обратном канале принят код Подтверждение (вывод адреса, увеличенного на единицу), С-А-1 - в остальных случаях (вывод текущего адреса).

В цикле Тб организован цикл записи в узел 30 результате операции второго АЛУ 38: С-В - если передается код Команда, Начало или код Речь/данные без подтверждения в обратном канале (сохранение текущего адреса), С - в остальных случаях (инициализация текущего адреса).

Запись в узел 30 запрещена, если принимается код Конец или Команда, либо передается код Сообщение или код Начало без подтверждения в обратном канале (увеличение текущего адреса на единицу).

Запись в блок 1 памяти в цикле Т7 разрешена, если передается код Подтверждение, Команда или Начало.

Запись в блок 1 памяти в циклах Т1, Т2 запрещена, если принимается код Речь/данные.

Второй счетчик 35 инициализируется сигналом 25 цикловой синхронизации. По перепаду 0-1 сигнала цикловой синхронизации формирователь 36 формирует сигнал сброса, который также инициализирует блок 4.

В исходном состоянии после инициализации блока 1 памяти кодом Свободно во все ячейки узла 30 постоянно записывается состояние первого счетчика 34. Первое АЛУ 31 выполняет операцию С-А-1, благодаря чему на адресном выходе блока 3 формируется код О для всех каналов. Коды Неисправность, Нетсвязи, Занято вызывают то же действие, что и код Свободно.

При приеме сообщения по одному из каналов каждый код Сообщение по этому

каналу вызывает запись в узел 30 результата операции второго АЛУ 38 С-В. Первое АЛУ 31 выполняет операцию С-А, обеспечивая постепенное увеличение текущего адреса на единицу. Код Начало, следующий в начале пакета сообщения, инициализирует адрес данной приемной подобласти блока 1 путем разрешения записи состояния первого счетчика 34 в узел 30 и этим обеспечивает

0 запись поступающего сообщения в начале данной подобласти.

Поступление кода Конец вызывает установку на выходе первого АЛУ 31 кода О, вызывая запись Конец в 0-ю ячейку

5 данной подобласти. При передаче пакета сообщения коды Начало и Сообщение вызывают запрет записи в узел 30, благодаря чему обеспечивается постепенное увеличение текущего адреса на единицу. Вывод

0 кода Конец вызывает инициализацию текущего адреса в узле 30 для данного канала. В циклах приема вся принимаемая информация записывается в соответствующие подобласти области принимаемых данных

5 блока 1 памяти. При Этом коды Конец, Подтверждение, Свободно, Неисправность, Нет связи, Занято всегда записываются в 0-е ячейки подобластей блока 1. В циклах передачи вся передаваемая

0 информация, кроме кодов Речь/данные, выводится в выходной тракт через коммутатор 21. При обнаружении кода Речь/данные коммутатор 21 переводится на передачу информации с второго инфор5 мационного входа 28.

С целью самоинициализации передающей области блока 1 памяти на место переданных кодов Начало, Команда, Подтверждение в блок 1 памяти записыва0 ется код Речь/данные.

Для установления соединения через коммутационное поле в свободный канал необходимо послать пакет сообщения, включающий команды установления соеди5 нения. Для этого в свободную подобласть передающей области блока 1 памяти со стороны внешней микро-ЭВМ необходимо записать требуемую последовательность команд и пакет сообщения.

0 Рассмотрим для примера один передающий канал. В исходном состоянии блок 1 инициализирован кодом Свободно. Блок 3 в этом случае формирует на своем выходе код О для каждого канала. Код Свободно

5 выводится в каждом канальном интервале. Блок 3 анализирует старшие биты и, в зависимости от кода, выполняет соответствующую операцию и формирует код О. То есть из блока 1 выводится код свободно из 0-й ячейки соответствующей области.

После того, как из внешней микро-ЭВМ в данную область блока 1 будет записан пакет команд установления соединения, на выход в данный канал выводится первая команда. Код Команда поступает на блок 3, который продолжает формировать код О в данном канале с целью возможности получения подтверждения о выполнении 1-й команды. Чтобы из блока 1 повторно не выводилась 1-я команда, после ее вывода она стирается в цикле Т7 кодом Речь/данные и из блока 1 на вывод выводятся эти коды, пока в обратном канале не поступит код Подтверждение. При поступлении кода подтверждения (считывается из блока 1 в буферный регистр 70 блок 3 должен обеспечить увеличение адреса на единицу с целью возможности вывода следующей команды. Далее процесс аналогично повторяется для всех команд пакета.

При передаче пакета сообщения все происходит аналогично, за исключением того, что адрес увеличивается на 1 без ожидания подтверждения в обратном канале.

Вызываемый модуль обнаруживает вызов со стороны вызывающего модуля определением перехода приемного канала из строя Свободно в состояние Конец.

Прием сообщения начинается с появления кода Начало. Код Начало инициализирует адрес подобласти приемной области болка 1 памяти. Коды пакета сообщения записываются в данную подобласть начиная с первой ячейки. Код Конец записывается в данную подобласть в 0-ю ячейку для возможности определения поступления всего сообщения путем сканирования со стороны внешней микро-ЭВМ только 0-х ячеек приемных подобластей блока 1 памяти.

Технико-экономические преимущества предлагаемого устройства по сравнению с прототипом следующие.

Обеспечивается управление установлением соединения одновременно по всем каналам за счёт введения блоков 3, 5, 6, 7, сокращение аппаратурных затрат за счет объединения функции запоминания информации в одном блоке 1 памяти и использования одних и тех же схем адресации, входных и выходных регистров для записи и считывания на всех канальных интервалах последовательно, использование для передачи сообщений, установления соединений, подтверждения установления соединения и для обмена речевой информацией одних и тех же дуплексных трактов с временным уплотнением каналов за счет возможности кодирования информации в старших разрядах, что исключает необходимость дополнительных линий связи, повышение

быстродействия и надежности системы коммутации, благодаря возможности задания состояний передающих каналов и запоминания состояний приемных каналов в определенных ячейках блока 1 памяти, что обеспечивает более быстрое и надежное взаимодействие с внешней средой, возможность использования для диагностики трактов с временным уплотнением каналов.

Формула изобретения

Устройство для автоматического установления соединений и обмена сообщениями, содержащее формирователь управляющих импульсов, блок памяти, входы которого подключены к выходам блока последовательно-параллельных преобразователей, первые входы блока параллельнопоследовательных преобразователей подключены к выходам блока памяти, о т- личающееся тем, что, с целью повышения скорости установления соединения, в него введены последовательно соединенные блок формирования адресов, преобразователь кодов и мультиплексор, выход которого подключен к адресным входам блока памяти, буферный регистр, выходы которого подключены к первым входам блока формирования адресов, формирователь кода, выходы которого соединены с входами блока памяти и блок сопряжения, первые выходы которого подключены к вторым входам мультиплексора, третьи и четвертые

входы которого подключены соответственно к первым и вторым выходам блока формирования адресов, вторые и третьи входы которого подключены соответственно к первым выходам блока параллельно-последовательных и блока последовательно- параллельных преобразователей, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходом формирователя управляющих импульсов, третий и четвертый выходы которого подключены соответственно к первому и второму управляющему входу блока параллельно-последовательных преобразователей, третий управляющий вход которого

объединен с третьим управляющим входом блока последовательно-параллельных преобразователей, первыми управляющими входами мультиплексора, блока формирования адресов и подключен к пятому

выходу формирователя управляющих импульсов, шестой и седьмой выходы которого подключены соответственно к второму и третьему управляющим входам блока формирования адресов, первый и второй управ- ляющие выходы которого подключены

соответственно к первому и второму входам формирователя управляющих импульсов, восьмой управляющий выход которого подключен к четвертому управляющему входу блока формирования адресов и второму управляющему входу мультиплексора, третий управляющий вход которого подключен к девятому выходу формирователя управляющих импульсов, десятый и одиннадцатый выход которого соединены с соответствующими управляющими входами формирователя кода и блока памяти, выходы которого соединены с информационными входами блока сопряжения и буферного регистра, управляющий вход которого объединен с четвертым управляющим входом мультиплексора и подключен к двенадцатому выходу формирователя управляющих импульсов, тринадцатый выход которого соединен с пятыми управляющими входами мультиплексора и блока формирования адресов, а также управляющим входом блока сопряжения, выход которого подключен к третьему входу формирователя

управляющих импульсов, четырнадцатый выход которого соединен с четвертым управляющим входом блока параллельно- последовательных преобразователей,

тактовый вход которого объединен с соответствующими входами блока последовательно-параллельных преобразователей и формирователя управляющих импульсов и является входом тактовой синхронизации

устройства, входом цикловой синхронизации которого является шестой вход блока формирования адресов, причем информационные входы блока памяти подключены к вторым выходам блока сопряжения, информационные входы-выходы которого являются соответствующими входами-выходами устройства, первыми и вторыми информационными входами и информационными выходами которого являются соответственно информационные входы блока последовательно-параллельных преобразователей, вторые входы и вторые выходы блока параллельно-последовательных преобразователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1510009A1 |

| Устройство для формирования адресов буферной памяти | 1987 |

|

SU1587581A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Диспетчер памяти ЭВМ | 1986 |

|

SU1363223A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Диспетчер памяти ЭВМ | 1990 |

|

SU1718225A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для формирования прерывания при отладке программ | 1985 |

|

SU1305680A1 |

25

t29 28

Фиг.З

от б/юка4

Фиг А

Авторы

Даты

1992-05-30—Публикация

1989-11-20—Подача