Изобретение относится к технике связи. Известно устройство временной коммутации асинхронных импульсных каналов, содержащее последовательно соединенные распределитель .временных каналов и блок памяти, первый выход которого через первый дешифратор подключен ко входам входных канальных комплектов, .первый и второй выходы которых подключены соответственно к первой информационной шине и шине передачи фазы, соединенной с входом анализатора фазы, первый выход которого подключен к первому входу переключающего блока, первый и второй выходы которого соединены соответственно с вторым н третьим входами блока памяти, первый выход которого соединен с вторым входом переключающего блока, а выходы второго дешифратора подключены к первым входам выходных канальных комплектов, вторые входы которых соединены с второй информацион|1ой. шиной {1J. Однако известное устройство не облад-ает достаточной пропускной способностью. Цель изобретения - увеличение пропускной способности. .Для этого в устройство временной коммутации асинхронных импульсных каналов, содержаще последовательно соединенные распределитель временных каналов и блок памяти, первый выход которого через первый дешифратор подключен ко входам входными канальных комплектов, первый и второй выходы которых подключены соответственно к первой информационной шине и щине передачи фазы, соединенной со входом анализатора фазы, первый вь1ход которого подключен к первому входу переключающего блока, первый и второй выходы которого соединены соответственно со вторым и третьим входами-блока памяти, первый выход которого соединен со вторым входом переключающего блока, а выходы второго дешифратора подключены к первым входам выходных канальных комплектов, вторые входы которых соединены со второй информационной шиной, введены п последовательно соединенных элементов задержки и п+1 регистров, первые выходы которых соединены со второй информационной шиной, а вторые выходы регистров подключены ко входам второго дешифратора, при этом входы первого регистра соединены со входами первого элемента задержки, первый, второй и третий входы которого соединены соответственно со вторым выходом анализатора фазы, первой информационной щиной и вторым выхбдом блока памяти, причем выходы элементов задержки подключены к входам соответствующих регистров, а третий вход перек.пючаю цего блока соединен с вторым выходом блока памяти.

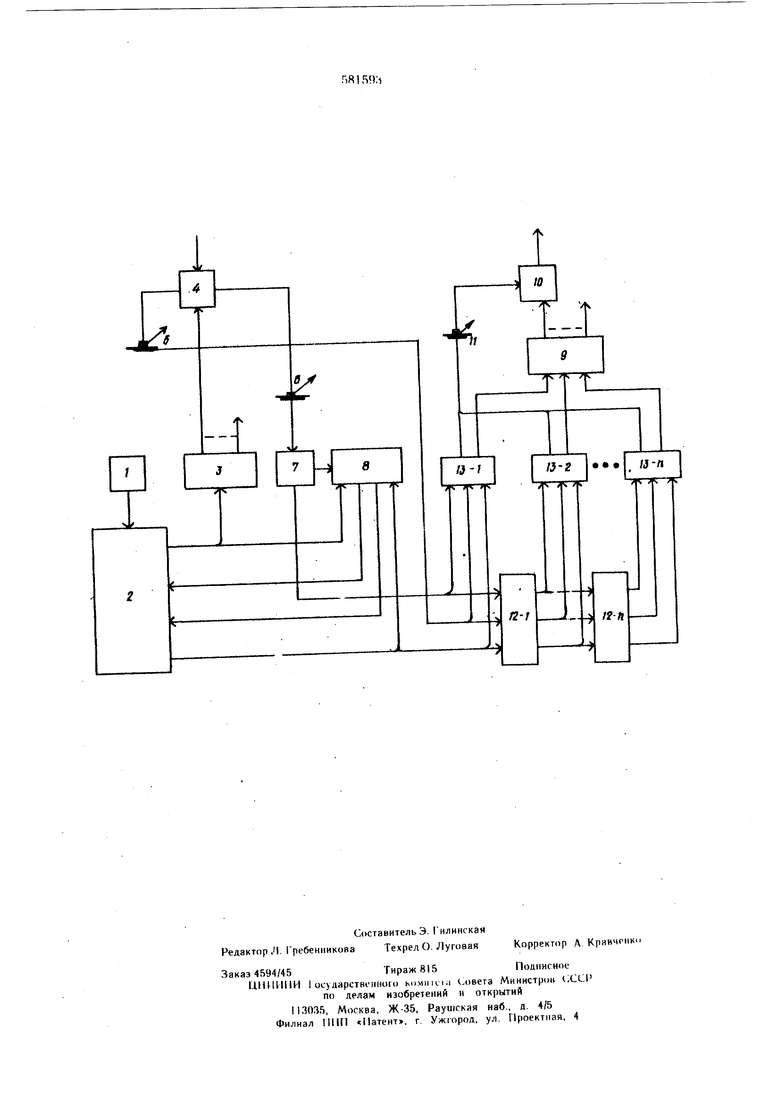

На чертеже дана структурная электрическая схема устройства временной коммутации асинхронных импульсных каналов.

Предлагаемое устройство содержит последовательно соединенные распределитель I временных каналов и блок 2 памяти, первчй выход которого через первый дешифратор 3 подключен к входам входных канальных комплектов 4, первый и второй выходы которых подключены соответственно к первой информационной шине 5 и шине 6 передачи фазы, соединенной с входом анализатора 7 фазы. Первый выход анализатора 7 фазы подключен к первому входу переключающего блока 8, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока 2 памяти, первый выход которого соединен с вторым входом переключающего блока 8. Выходы второго дешифратог)а 9 подключены к первым входам выходных канальных комплектов 10, вторые входы которых соединены с второй информационной шиной П. В устройство введены п последовательно соединенных элементов задержки 12-1 -12-п и п+1 регистров 13-1 -13-(п+I), первые выходы которых соединены с второй информационной шиной 11. Вторые выходы регистпов подключены к входам второго дешифpjTopa 9, при этом входы первого регистра 13-1 соединены с входами первого элемента задержки 12-1, первый, второй, третий входы которого соединены соответственно с в то рым выходом анализатора 7 фазы, первой информационной шиной 5 и вторым выходом 2 памяти. Выходы элементов задержки ivoa«лючены к входам со )тветствуюших регистров. Третий вход переключающего блока 8 соединен f вторым выходом блока 2 памяти

Летроиство временной коммутации асищронных импульсных канало работает следую1ДИМ образом.

Регистр 13-1-13-(пЧ-1) выдают информационный импульс на вход второго дешифратора 9 и вторую информационную шину 1. На втором выходе анализатора 7 фазы при обработке очередного управляющего сигнала появляется кодовая комбинация К, соответствующая отклонению импульса проключения от середины информа 1ионного импульса.

Кодовая комбинация с второго выхода анализатора фазы поступает на первый вход элемента задержки 12-1. на его йторой вход поступает сигнал с первой информационной шины 5, а на третий вход -- с второго выхода 2 памяти.

В большинстве случаев величина К/ 2-5 тактов. Количество элементов задержки должно быть равно 2К. В этом случае первый регистр 13-1 обеспечивает передачу информации на вход второго дешифратора У и вторую информационную шину II гфи появлении на

тине G передачи кодовой комбинации К, второй регистр-- К-1 и т.д. Каждое управляющее слово последовательно проходит по элементам задержки до тех пор. пока оно не будет считано одним из регистров. При этом задержки или опережения импульсов проключения относительно характеристического момента восстановления, возникц ие на предыдущих ступенях коммутации, будут скор,;ектироваиы.

Предлагаемое устройство может использоваться также при кодово-адресной коммутации. В этом случае информацию о фазе получать из канального комплекта или из промежуточных ступеней коммутации.

Технико-экономический эффект предлагаемого устройства заключается в уменьшении краевых искажений коммутируемых сигналов (увеличении пропускной способности группового тракта) и упрощении коммутации.

Формула изобретения

Устройство временной коммутации асинхронных импульсных каналов, содержащее последовательно соединенные распределитель временных каналов и блок памяти, первый выход которого через первый дешифратор подключен ко входам входных канальных комплектов, первь|й и второй выходы которых подключены соответственно к первой информационной шине и шине передачи фазы, соединенной с входом анализатора фазы, первый выход которого подключен к первому входу переключающего блока, первый и второй выходы которого соединены соответственно со вторым и третьим входами блока памяти, первый выход которого соединен со вторым входом переключающего блока, а выходы второго дешифратора подключены к первым входам выходных канальных комплектов, вторые входы которых соединены со второй информационной шиной, отличающееся тем, что, с целью увеличения пропускной способности, введены п последовательно соединенных элементов задержки и n-f.l регистров, первые выходы которых соединены со второй информационной шиной, а вторые выходы регистров подключены ко входам второго дешифратора, при этом входы первого регистра соединены со входами первого элемента задержки, первый, второй и третий входы которого соединены соответственно со вторым выходом анализатора фазы, первой информационной шиной и вторым выходом блока памяти, причем выходы элементов задержки подключены ко входам соответствующих регистров, а третий вход переключающего блока соединен с вторым выходом блока памяти.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР К 434610 кл. Н 04 L 11/20, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Канальное устройство объединенного коммутатора каналов и сообщений | 1975 |

|

SU531295A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Адаптивный статистический анализатор | 1980 |

|

SU955090A1 |

| СПОСОБ МНОГОКАНАЛЬНОЙ ПЕРЕДАЧИ ПАКЕТОВ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043658C1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Временной коммутатор асинхронныхиМпульСНыХ СигНАлОВ | 1979 |

|

SU809629A1 |

| Коммутатор изохронных каналов | 1978 |

|

SU725259A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство временной асинхронной коммутации импульсных сигналов | 1975 |

|

SU581592A2 |

Авторы

Даты

1977-11-25—Публикация

1975-12-24—Подача