1

Изобретение относится к телевизион-. ной тезшийе и предназначено для исподь зования в телевизионных устройствах cHHxpoHHaaiiHH, в частности в телевизион ных приемниках и синхрогёнераторах.

Известно устройство для строчной синхронизации, содержащее задающий генератор, выход которого подключен к входу блока вычитания, счетчик, первый выход которого Подключен к первому вхо ду фазового детектора 1J . В этом устройстве необходимо обеспечить высокую частоту переключения счетчика, примерно равную 12О МГц. Такую скорость переключения трудно обеспечить без применения свррхбы стродействующих интегральных схем, что является сувцесТ. венным недостатком. Кроме того, это устройство не защищено от импульсных помех, вызванных наличием врезок в кадровых синхроимпульсах и выбросов в телевизионном сигнале.

Целью, изобретения является упрощение устройства за счет исключен 1я сверхбыстродействующих логических элементов путем четырехкратного уменьшения частоты переключения счетчика при одновременном сохранении свойства фиксации номинальной строчной частоты выходных импульсов во время пропадания входного сигнала и повышение помехозащищенности от воздействия импульсных помех.

Для этого в устройство для строчной синз ронизашга, содержащее задающий генератор, выход которого подключен к входу блока вычитания, счетчик, первый выход которого подключен к первому входу фазового детектора, введены Т-триггер и последовательно соединенные формирователь импульса, ин- вертор, RS -триггер и логический элемент 2И-2ИЛИ-НЁ. Причем к второму входу последнего подключен выход формирователя импульса, к третьему входу - выход Т-триггера, установочный вход которого соединен с вторым выхоцом триггера, а четвертый вход логическопэ

элемента 2И-2ИЛИ-НЕ подключен н счетному входу Т триггера и к второму выходу счетчика, третий выход которого соединен с вторым входом RS -триггера, выход логического элемента 2И 2ИЛИ-НЕ подключен к второму входу фазового детектора, второй вход блока вычитания подключен к выходу фазового детектора, а выход блока вычитания К входу счетчика.

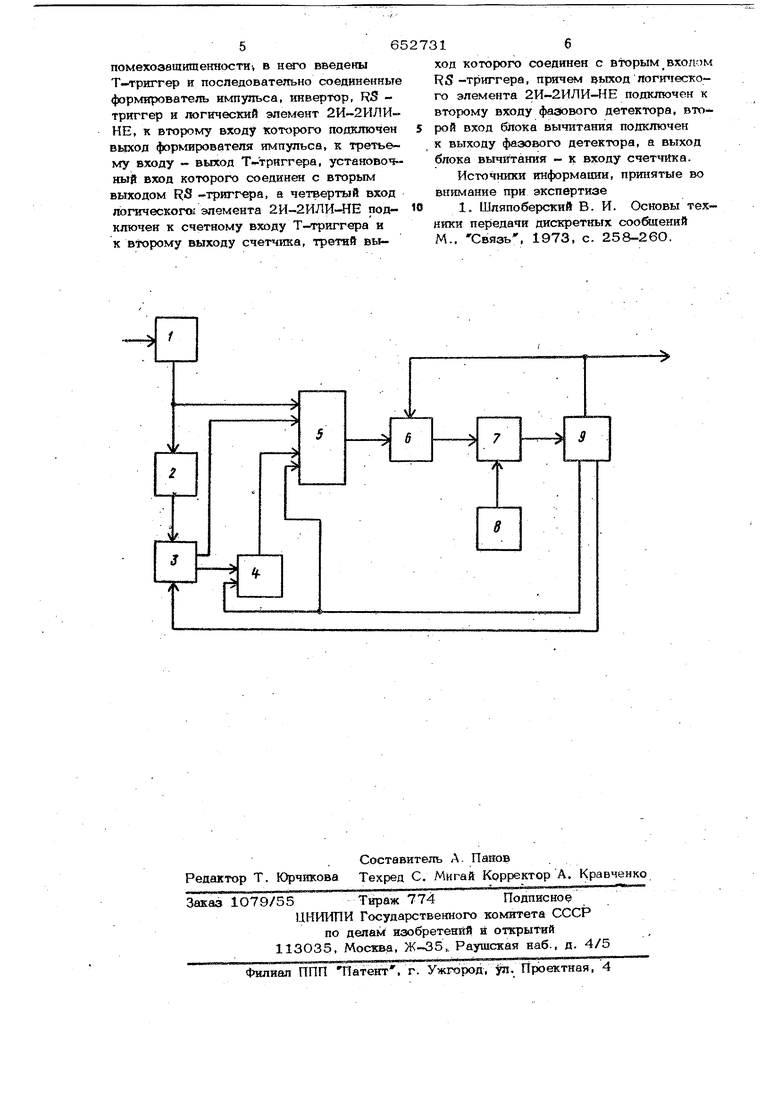

На чертеже изображена структурная влектрическая схема устройства для стро ной синхронизации, которое содержит -формирователь импульса 1,инвертор 2, R5 «триггер 3, Т-триггер 4, логический элемент 2И-2И71И-НЁ 5, фазовый детектор 6, блок вычитания 7, задающий генератор 8, счетчик 9.

Счетчик 9, фазовый детектор 6, задающий генератор 8 и блок вычитания 7 образуют двухпозиаионную релейную .цифровую систему синхронизации. Минимальное время между моментами появле кия импульсов нд входе счетчика в этой системе определяется соотношением

At S Tp,jn . При заданном размахе колебаний временного положения импульсов на выходе устройства строчной синхронизации А& 3 30 НС, при этом макст«1альная частота переключения счеч чика составляет приблизительно ЗОМГп, т, е. в четыре раза меньше, чем в известном уст йстве синхронизации.

Для сохранения свойства фиксации номинальной частоты выходных импульсов во время пропадания входного сигнала, утрачиваемого при переходе к двухпозишюнной цифровой системе синхронизации, и обеспечения защиты от импульсных помех на вход логического элемента 2И-2ИЛИ-НЕ 5 и на вход инвертора 2 поступают укороченные импульсы, представляющие собой отметки временного положения передних фронтов импульсов положительной телевизионной синхросмеси. При этом наряду с истинными отметками временного положения строчных С1шхроимпупьсов возможно появление ложных отметок, вызваннь1х воздействием импульсных помех и кадровых врезок.

Уменьшение воздействия импульсных помехдостигается тем, что логический элемент 2И-2ИЛИ-НЕ открыт для прохождения временных отметок входных импульсов только на коротком интервале времени, соответствующем наличию еданичного уровня в стробирующем сигнале

который вырабатывается F 5-триггером 3, В такое единичное состояние -триггер переводится импульсом с , опережающего выхода счетчика 9, а затем сбрасывается в нулевое состояние первым прищедшим на вход укороченным строчным синхроимпульсом. Благодаря существующей задержке интегральных схем этот укороченный синхроимпульс

успевает пройти на выход логического элемента 2И-2ИЛИ-НЕ, в то как на следующем за ним интервале времени, вплоть до прихода нового импульса с опережающего выхода счетчика, логиЧеский элемент 2 И-2ИЛИ-1Ш закрыт для прохождения любых импульсов.

В случае пропадания входных синхроимпульсов на инверсном выходе f(S -триггера 3 появляется нулевой сигнал достаточной длительности и Т-триггер 4 начинает вырабатывать сигнал полустроч- кой частоты. Благодаря этому на выходе логического элемента 2И-2ИЛИ-НЕ5 .появляются инвертированные импульсы с запаздьгеающего выхода счетчика, действующие с полустрочной частотой, которые поступают на вход фазового детек.тора 6. Так как при пояшлении на входе фазового детектора импульса с запаздывающего выхода счетчика 9 цифровая двухпозиционная система синхронизации вьфабатывает выходные импульсы с максимальным периодом, а при отсутствии импульсов на входе фазового детектора 6 она вырабатьтает импульсы с мини- мальным периодом, то появление импульсов полустрочной частоты с запаздывающего выхода счетчика приводит к коммутации периода импульсов от строки к стрвке на выходе устройства. При этом средний период выходного сигнала со счетчика 9 остается равен номинальному, f. е. сохраняется свойство ф пссацнн номинальной частоты при-пропадаюта входКОГО сигнала.

Формула изобретения

Устройство для строчной синхронизации, содержащее задающий генератор, выход которого подключен к входу блока вычитания, счетчик, первый выход которого подключен к первому входу фазового детектора, отличающееся тем что, с целью упрощения устройства за счет исключения сверхбыстродейсг ук щих логических элементов и повышения 56 помехозащищенности , в нетю ввепены Т-триггер и последовательно соединенные формирователь импульса, инвертор, RS триггер и логический элемент 2И 2ИЛИНЕ, к второму входу которого подключен вьрсол форкгарователя импульса, к третьему входу - выход Т-трйггера, установочный вход которого соединен с вторым выходом RS -триггера, а четвертый вход логического; элемента 2И-2ИЛИ-НЕ подключен к счетному входу Т-триггера и к второму выходу счетчика, третий вы1ход которого соединен с вторым входом RS-триггера, причем выход логи 1еского элемента 2И-2ИЛИ-НЕ подключен к второму входу фазового детектора, второй вход блока вычитания подключен к выходу фазового детектора, а выход блока вычитания - к входу счетчика. Источники информашга, принятые во внимание при экспертизе 1. Шляпоберский В. И. Основы техники передачи дискретных сообщений М-. Связь, 1973, с. 258-260.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ведомый телевизионный синхрогенератор | 1987 |

|

SU1598208A1 |

| Телевизионное устройство для измерения координат пятна | 1987 |

|

SU1450136A1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Устройство цветовой синхронизации декодера СЕКАМ | 1990 |

|

SU1753622A1 |

| Устройство для синхронизации преобразователей,включаемых параллельно на общую нагрузку | 1985 |

|

SU1319182A1 |

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Устройство дистанционной синхронизации телевизионной камеры | 1987 |

|

SU1525942A1 |

| Компенсатор низкочастотных искажений телевизионного сигнала | 1984 |

|

SU1185651A1 |

| Устройство цветовой синхронизации | 1985 |

|

SU1317691A1 |

| Устройство обнаружения цветоразностных сигналов | 1982 |

|

SU1085017A1 |

Авторы

Даты

1979-03-15—Публикация

1976-11-29—Подача