ны управляющий JK -Tj lfrrep, КУ триггеры, логический элемент 2-2И2ИЛИ, логические элементы И-НЕ, причем логический элемент 2-2И2ИЛИ включен между фазовым детектором и делителем частоты с переменным коэффициентом деления, а первый R9 - триггер - между блоком для вделения разностной частоты и реверсивным счетчиком, тактовый вход которого соединен с третьим выходом делителя частоты с фиксированным коэффициентом деления через первый логический элемент И-НЕ, соединенный с прямым выходом управляющего 3is -триггера, инверсный выход которого подключен к J - и К - входам и к четвертому входу логического элемента 2-И-2ИЛИ , третий вход которого соединен с выходом делителя частоты с перменным коэффициентом деления,при этом первый вход логического элемента 2-2И-2ИЛИ подключен ко второму входу делителя частоты с фиксированным коэффициентом деления, а второй - к прямому выходу управляющего ЭК -триггера, тактовый вход которого через второй и третий логический элементы И-НЕ подключен к выходам блока для выделения разностной частоты, к которым одновременно подключены S -входы втрого и третьего RS -триггеров, а их прямые выходы через четвертый логический элемент И-НЕ подключены к S -входу четвертого RS -триггера, R -вход которого соединен с выходом третьего логического элемента И-НЕ, а инверсный выход - с вторым входом второго логического элемента И-НЕ и одновременно с R -входом управляющего 31. -триггера прямой выход которого подключен к R -входам второго и третьего триггеров.

При таком выполнении синтезатора частот первый же импульс с одного из выходов блока для выделения разностной частоты заставит сработать управляющий ЗК -триггер, который включит устройство для автопоиска и разомкнет кольцо ФАПЧ, но так, что на ФД вместо импульсов с ДПКД начнут поступать вспомогательные импулсы со второго выхода ДФКД, сдвинуты относительно основных на 180°. Это приведет к тому, что ФД выдаст на вход ГУН такое управляющее напряжение, которое в режиме синхронизации соответствовало бы захвату ФАПЧ ровно в середине характеристики ФД, т.е. произойдет имитация работы кольца ФАПЧ в режиме синхронизации. Кроме того, на тактовый вход реверсивного счетчика теперь поступает уже не монотонно убывающая по частоте последовательность импульсов, а последовательность импульсов с некоторого третьего выхода ДФКД. такой

постоянной частоты, которая обеспечила бы максимально возможную для данной системы ФАПЧ скорость вхождения в режим синхронизации. Поскольку при этом устройство для автопоиска подает на второй вход ГУН управляющее напряжения, изменяющееся не плавно, а ступенчато, то наступит такой момент, когда соотношение между частотами импульсов на выходах ДПКД и ДФК изменится на противоположное. При этом первый же импульс со второго выхода блока для выделения разностной частоты (импульс реверса) заставит сработать управляющий Л1. -триггер, который включит ФАПЧ и отключит автопоиск, т. е. произойдет захвати причем, в середине характеристики ФД.

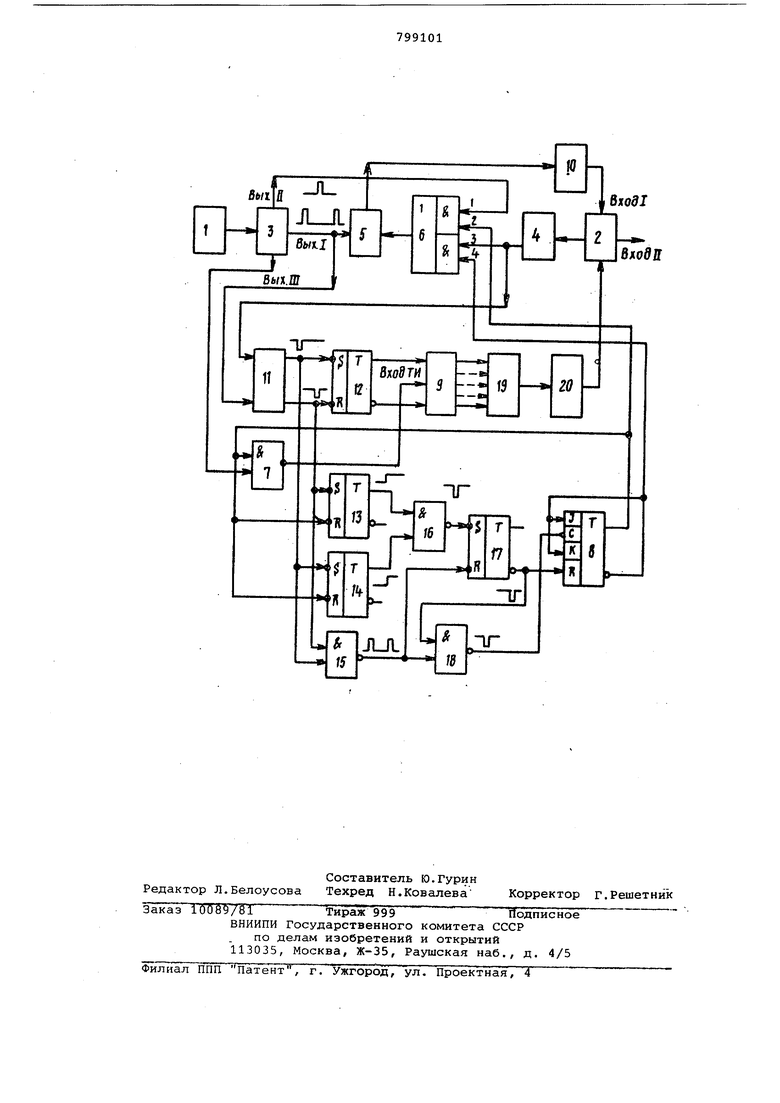

На чертеже представлена функциональная схема синтезатора частот.

Синтезатор частот содержит ОГ 1 и ГУН 2, выходы которых соединены соответственно со входами ДФКД 3 и ДПКД 4. ДФКД 3 имеет три выхода. Первый подключен к одному входу ФД 5, второй - через логический элемент б ко второму входу ФД 5, а третий выход через логический элемент 7, коммутируемый сигналом с прямого выхода управляющего Jk, -триггера 8, соединен с тактовым входом реверсивного счетчика 9. Выход ФД 5 через первый ФНЧ 10 подключен к первому вхо-ду ГУН 2. Ко второму входу ФД 5 через логический элемент б подключен также и выход ДПКД 4. Коммутация сигналов с выхода ДПКД 4 или со второго выхода ДФКД 3 на второй вход ФД 5 через логический элемент б осуществляется с соответствующих выходов управляющего JK- -триггера 8. Выход ДПКД 4 и первый выход ДФКД 3, кроме того, подключены ко входам блока 11 для выделения разностной частоты. Выходы блока 11, для выделения разностной частоты, подключены к R - и S - входам первого R.3 -триггера 12. к S -входагл второго и третьего RS триггеров 13 и 14 и ко входам логического элемента 15. Выходы первого US-триггера 12 соединены со входами суммирования и вычитания реверсивного счетчика 9. Прямые выходы второго и третьего RS -триггеров 13 и 14 подключены ко входам логического элемента 16, выход которого соединен с S -входом четвертого -триггера 17. Второй и третий RS -триггеры 13 и 14, логический элемент 16 и четвертый триггер 17 образуют блок для выделения импульса реверса, который с инверсного выхода четвертого RSтриггера 17 поступает на R -вход управляющего 3k -триггера 3 и на вход логического элемента 18. Выход логического элемента 15 соединен с R входом четвертого RS -триггера 17 и со вторым входом логического эле мента 18, выход которого подключен к тактовому входу управляющего ЗКтриггера 8. R -входы второго и тре. тьего Л5 -триггеров 13 и 14 соединены с прямым выходом управляющего ЗК-триггера 8. Выход каждого разряд реверсивного счетчика 9 соединен с соответствующими входами ЦАП 19, ко торый вырабатывает управляющее напря жение и через второй ФНЧ 20 подает его на второй вход ГУН 2. Синтезатор частот работает следу ющим образом. Предположим, что в начальный момент частота ГУН 2, поделенная ДПКД 4,отличается от частоты ОГ 1, поделенной ДФКД 3. В этом случае на одномиз выходов блока 11 для выделения разностной частоты появится о рицательный импульс, который через логические элементы 15 и 18 поступит на тактовый вход управляющего ЗК-триггера 8 и опрокинет его в положение О на инверсном выходе. Этот О, поступая на 3 - и - вхо ды управляющего ЗК -триггера 8, запрещает его срабатывание от последующих импульсов разностной частоты на тактовом входе т. е. осуществляет его самоблокировку. Одновременно О с инверсного выхода 31 -триггер 8 запрещает прохождение импульсов с ДПКД 4 через логический элемент 6 на второй вход ФД 5, а 1 с прямого выхода tJ К. -триггера 8 разрешает прохождение через логический эле мент 6 на второй вход ФД 5 импульсо со второго выхода ДФКД 3. Частоты следования импульсов с первого и вт рого выходов ДФКД 3 равны, по фазе эти импульсы сдвинуты на 180°. Импульсы с первого выхода ДФКД 3 формируют пилообразное напряжение ФД 5,а импульсы со второго выхода, поступая на второй вход ФД 5 вместо импульсов с ДПКД 4, образуют точно Б середине фазовой характеристики в оборки напряжения, которые запоминаются схемой памяти в ФД 5 и через ФНЧ 10 поступают на первый вход ГУН 2. Таким образом, хотя кольцо ФАПЧ и разомкнуто (между выходом ДПКД 4 и вторым входом ФД 5) , на первый вх ГУН 2 с выхода ФД 5 через ФНЧ 10 по ступает управляющее напряжение, как бы соответствующее захвату ФАПЧ ровно в середине фазовой характерис тики. Одновременно с этим 1 с пря мого выхода ЗК -триггера 8 разрешае прохождение импульсов с третьего выхода ДФКД 3 через логический элемент 7 на тактовый вход реверсивного счетчика 9, т. е. включается устройство для автопаиска. Работа реверсивного счетчика на сложение или на вычитание определяется потенциалами с выхода RS -триггера 12, который устанавливается в определенно положение импульсами с выходов бЛока 11 для выделения разностной частоты. Реверсивный счетчик 9 управляет ЦАП 19, вырабатывающим з зависимости от количества импульсов, поступивших на тактовый вход, ту или иную градацию (ступеньку) постоянного напряжения, которое поступает на второй вход ГУН 2. Под действием этого ступенчатого управляющего напряжения частота на выходе ГУН 2 также дискретно изменяется в сторону уменьения частотной разницы на выходах ДФКД 3 и ДПКД 4. Так как изменение частоты происходит дискретно, наступает такой момент, когда скачком бует пройдена точка равенства частот и на реверсивный счетчик 9 поступает команда обратного-счета. Это значит, что Й. -триггер 12 под действием первого отрицательного импульса ре-т верса с другого выхода блока 11 для выделения разностной частоты опрокинется в противоположюое состояние. В самый начальный момент под действием первого отрицательного импульса с одного из выходов блока 11 для выделения разностной частоты сработал один из RS -триггеров 13 или 14. С приходом отрицательного импульса (.импульса реверса) с другого выхода блока 11 для выделения разностной частоты сработает второй R6 -триггер 14или 13. В результате на оба входа логического элемента 16 поступят по 1 и.логический элемент 16 вьщаст О на S -вход Т13 -триггера 17. Одновременно на -вход us -триггера 17 с выхода логического элемента 15поступит положительный импульс. Поэтому на инверсном выходе RS-триггера 17 появится О, который запретит прохождение импульса с выхода элемента 15 через элемент 18 на так-, товый вход 3k. -триггера 8 и одновременно, этот О, поступая на R -вход ЗК -триггера 8, опрокинет ei-o в состояние О на прямом выходе. Логический О с прямого выхода ЗК. -триггера 8 запретит прохождение тактовых импу1.ьсов с третьего выхода ДФКД 3 через логический элемент 7 на такто.вый вход реверсивного счетчика 9 (т. е. отключится автопоиск), устанЪвит RS -триггеры 13 и 14 в исходное состояние (т. е. состояние О на прямых выходах) и запретит прохождение импульсов со второго выхода ДФКД 3 через логический элемент 6 -на второй вход ФД 5. Одновременно 1 с инверсного выхода ЗК. -триггера 8 разрешит прохождение импульсов с выхода ДПКД 4 через логический элемент б на второй вход ФД 5, т. е. замкнется кольцо ФАПЧ и осуществится закват в середине характеристики фазового детектора, так как теперь фазовый сдвиг между импульсами с выхода ДПКД 4 и со второго выхода ДФКД 3 очень мал и не превышает одной

ступеньки по управляющему напряженжо

на ГУН 2.

Использование данного синтезатора частот позволяет получить максималь ное быстродействие, т. е. минимальное время перехода с одной частоты на другую. Это один из параметров всех синтезаторов частот и особенно тех, который используются в устройствах, где для улучшения помехозащищенности несущая частота все время меняется по какому-либо закону, например в устройствах, где используется способ адаптации по частоте Кроме того, захват в середине характеристики ФД дает возможность наиболее эффективно использовать полосу захвата и удержания системы ФАПЧ, обеспечивая тем самым высокие технологические и. эксплуатационные показатели качества изделий, в которых применяется данный синтезатор. Захват в середине характеристики ФД устраняет возможность срыва синхронизации при помехах.

Формула изобретения

Синтезатор частот, содержащий опорный генератор, делитель частоты с фиксированным коэффициентом деления, фазовый детектор, первый фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, включенные в кольцо фазовой автоподстройки частоты, а также устройство для автопоиска, включенное параллельно фазовому детектору и состоящее из последовательно соединенных блока для выделения разностной частоты, реверсивного счетчика, цифроаналогового преобра-зователя и второго фильтра нижних частот, отличающийся тем что, с целью повышения быстродействия надежного вхождения в режим синхронизации , в него введены управляющий ЛК -триггер, RS -триггеры, логический элемент 2-2И-2ИЛИ, логи;;-:;, элементы И-НЕ, причем логи, :Л.;( элемент 2-2И-2ИЛИ включен .:,«(/ фазовым детектором и делителем ,-:::тоты с перменным коэффициентом де,..:.йия, а первый S-триггер -- 1у.ежду блоком для выделения разностной частоты и реверсивным счетчиком,, тактовый вход которого соединен с третьим выходом делителя частоты с фиксированным коэффициентом деления через первый логический элемент И-НЕ,

O соединенный с прямым выходом управляющего 5К -триггера, инверсный выход которого подключен к 3 - и К-входам и к четвертому входу логического элемен1-а 2-2,4-2ИЛИ . третий вход

5 которого соединен с выходом делителя частоты с переменным коэффициентом деления, при этом первый вход логического элемента 2-2И-2ИЛИ подключен ко второму входу делителя часто0 с фиксированным коэффициентом деления , а второй к прямому выхо,ду управляющего JK -триггера, тактовый вход которого через вторрй и тре,тий логический элементы И-НЬ подJ ключен к выходам блока для выделения разностной частоты, к которым одновременно подключены S -входы второго и третьего RS -триггеров, а их прямые выходы через четвертый логический элемент И-НЕ подключены к

О S -входу четвертого RS -триггера, R -вход которого соединен с выходом третьего логического элемента И-НЕ а инверсный выход - со вторым входом второго логического элемента И-НЕ

5 и одновременно с И -входом управляющего -триггера, прямой выход которого подключен к R -входам второго и третьего RS-триггеров.

Источники информации, 0 принятые во внимание при экспертизе

1.Галин А.С. Диапазонно-кварцевая стабилизация СВЧ. М., Связь, 1976, с. 33.

2.Рыжков А.В. Комбинированная система ФАПЧ с реверсивным поиском. - Электросвязь, 1975, № 10, с. 6870 (прототип).

BxodI

ВюдП

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU886254A2 |

| Цифровой синтезатор частот | 1987 |

|

SU1469554A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Синтезатор частот | 1977 |

|

SU758528A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частот | 1979 |

|

SU879733A2 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2000 |

|

RU2191468C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

Авторы

Даты

1981-01-23—Публикация

1976-11-26—Подача