1

Изобретение относится к области |вычислительной техники и может быть использовано в процессорах для спектрально-корреляционного анализа сигналов.

Известно устройство для быстрого преобразования Фурье, содержащее регистры реальной и мнимой части комплексного весового коэффициента, регистры вещественной и мнимой части первого числа, четыре множительных блока, шесть одноразрядных комбинационных сумматоров и регистры реальной и мнимой части второго числа ij

Однако, это устройство требует большого количества оборудования.

Наиболее близким техническим решением к данному изобретению является устройство, которое, как и данное устройство, содержит множительные блоки, первые входы первых двух из которых подключены к соответствующим входам задания постоянных коэффициентов устройства, а вторые входы этих блоков подключены соответственно ко входг1М вещественной и мнимой части первого комплексного числа устройства, сумматоры и регистры J2J.

Однако, это устройство является сложным.

2

Цель изобретения - упрощение устройства.

Указа:нная цель достигается тем, что устройство содержит два суМматора-вычитателя, первые входы которых подключены соответственно ко входам вещественной и мнимой части второго комплексного числа устройства, а выходы этих блоков соединены со входами соответствующих регистров выходы которых являются выходами устройства, входы вещественной и мнимой части первого комплексного числа устройства и входы задания

S постоянных коэффициентов устройства соединены соответственно со входами первого и второго сумматоров/ выходы которых соединены со входами третьего множительного блока, выход

0 которого соединен с первыми входами третьего и четвертого сумматоров, вторые входы которых подключены соответственно к выходам первого и второго множительного блока, а выходы третьего и четвертого сумматоров соединены со входами соответствующих сумматоров-вычитателей.

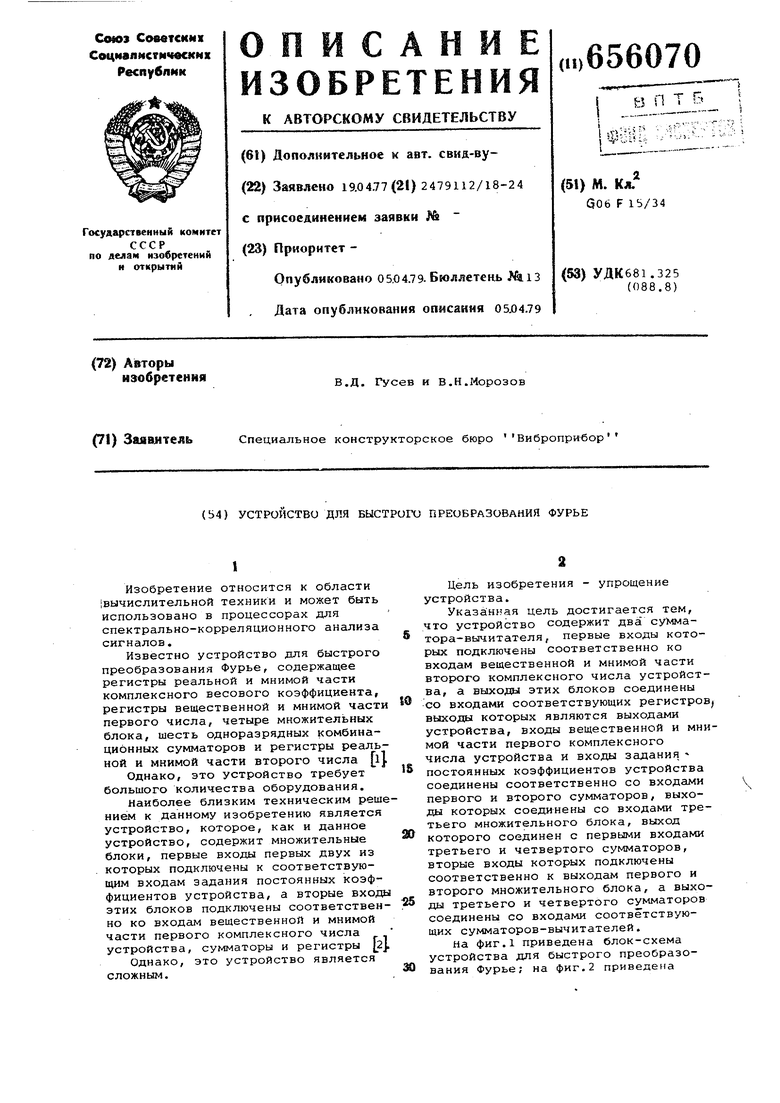

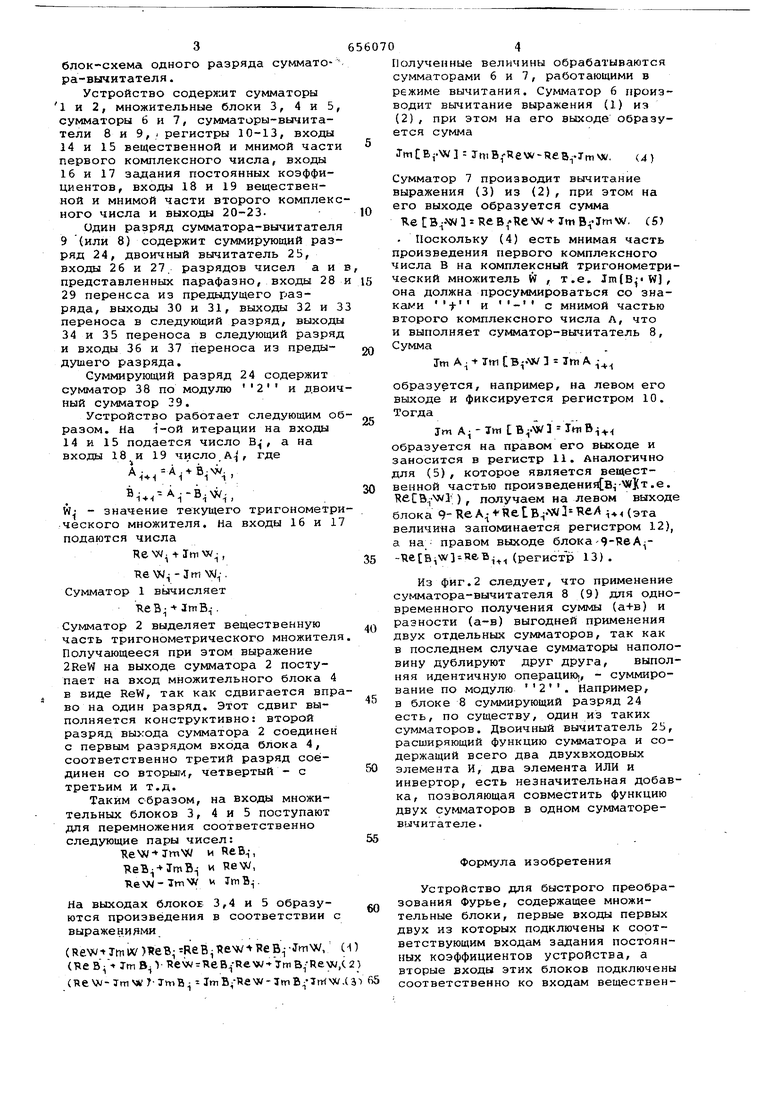

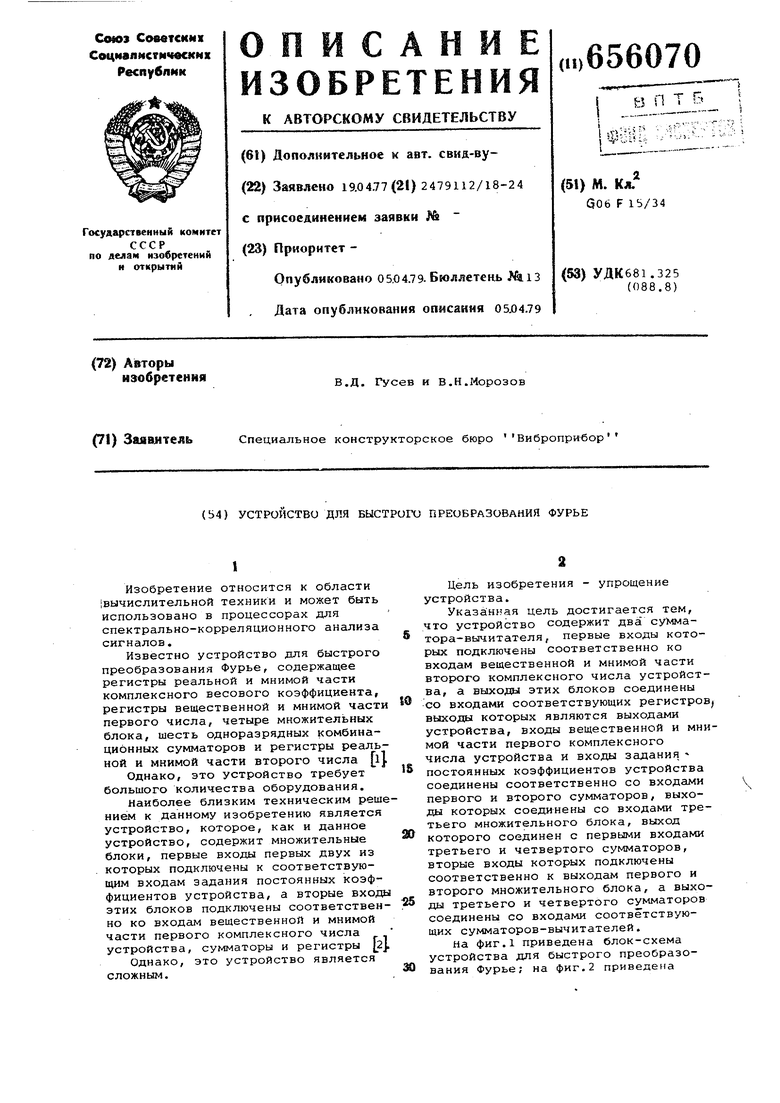

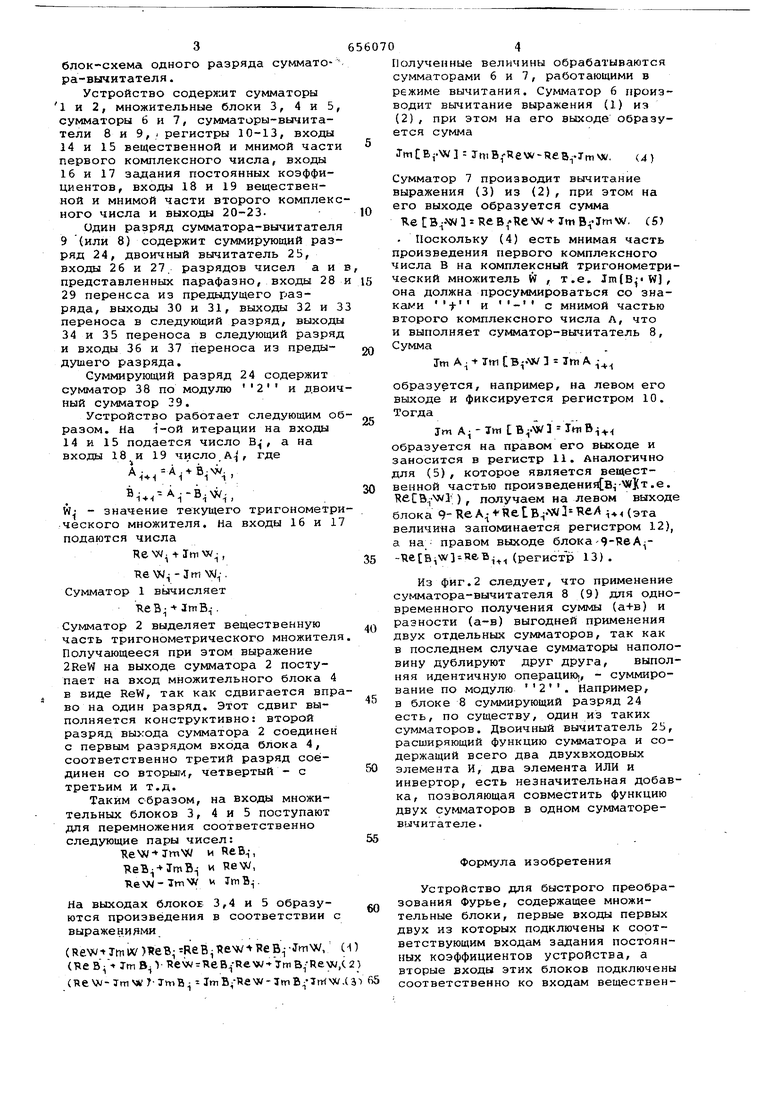

на фиг.1 приведена блок-схема устройства для быстрого преобразо0вания Фурье; на фиг.2 приведена блок-схема одного разряда сумматора-вычитателя. Устройство содерхонт сумматоры 1 и 2, множительные блоки 3, 4 и 5 сумматоры б и 7, сумматоры-вычитатели 8 и 9,1 регистры 10-13, входы 14 и 15 вещественной и мнимой част первого комплексного числа, входы 16 и 17 задания постоянных коэффициентов, входы 18 и 19 вещественной и мнимой части второго комплек ного числа и выходы 20-23Один разряд сумматора-вычитател 9 (или 8) содержит суммирующий раз ряд 24, двоичный вычитатель 25, входы 26 и 27. разрядов чисел ай представленных парафазно, входы 28 29 переноса из предьадущего разряда, выходы 30 и 31, выходы 32 и переноса в следующий разряд, выход 34 и 35 переноса в следующий разря и входы 36 и 37 переноса из предыдущего разряда. Суммирующий разряд 24 содержит сумматор 38 по модулю 2 и двои ный сумматор 39. Устройство работает следующим о разом. На 1-ой итерации на входы 14 и 15 подается число , а на входы 18 и 19 число A-J, где .., В,,.А.-В., - значение текущего тригонометр ческого множителя. На входы 16 и 1 подаются числа Re W.J-v Ini w, VJ,-. Сумматор 1 вычисляет ReB- JmB,-. Сумматор 2 выделяет вещественную часть тригонометрического множител Получающееся при этом выражение 2ReW на выходе сумматора 2 поступает на вход множительного блока 4 в виде ReW, так как сдвигается впр во на один разряд. Этот сдвиг выполняется конструктивно; второй разряд выхода сумматора 2 соединен с nepBfciM разрядом входа блока 4, соответственно третий разряд соединен со вторыг, четвертый - с третьим и т.д. Таким образом, на входы множительных блоков 3, 4 и 5 поступают для перемножения соответственно следующие пары чисел: и , и nevv, ReNJW-ImV/ u JmB. Ha выходах блоков 3,4 и 5 образуются произведения в соответствии с выражениями (ReWfTmw)l eB--ReB T eNk/-vTieBT-irmNX/, (TteBY-t TtnB VRew ReBYRew-fTmB/Rexw (Re Vy-Jm ТТшВ ImB Rew-j(TiB lrri / 04 Полученные величины обрабатываются суммсхторами 6 и 7, работающими в режиме вычитания. Сумматор 6 производит вычитание выражения (1) из (2), при этом на его выходе образуется сумма JmCBi-Vi/3:3-r,,B,UeW-ReB -TmN, (4) Сумматор 7 производит вычитание выражения (3) из (2), при этом на его выходе образуется сумма Яе B -wisReB Reow- -JwB JtTtw, (S) Поскольку (4) есть мнимая часть произведения первого комплексного числа В на комплексный тригонометрический множитель W , т.е. ), она должна просуммироваться со знаками f и - с мнимой частью второго комплексного числа л, что и выполняет сумматор-вычитатель 8, Сумма Тт )tf ГпА. образуется, например, на левом его выходе и фиксируется регистром 10. Тогда Jm IniB образуется на правом его выходе и заносится в регистр 11. Аналогично для (5), которое является вещественной частью произведени5{В1-(т.е. KeCB, ) , получаем на левом выходе блока 9-КеА.4Не1в «3 Т1 Л(эта величина запоминается регистром 12), а на правом выходе блока9-ReA -Re BiW ReB- (регистр 13) . Из фиг.2 следует, что применение сумматора-вычитателя 8 (9) для одновременного получения суммы (а+в) и разности (а-в) выгодней применения двух отдельных сумматоров, так как в последнем случае сумматоры наполовину дублируют друг друга, выполняя идентичную операцию;, - суммирование по модулю 2. Например, в блоке 8 суммирующий разряд 24 есть, по существу, один из таких сумматоров. Двоичный вычитатель 25, расширяющий функцию сумматора и содержащий всего два двухвходовых элемента И, два элемента ИЛИ и инвертор, есть незначительная добавка, позволяющая совместить функцию двух сумматоров в одном сумматоревычитателеФормула изобретения Устройство для быстрого преобразования Фурье, содержащее множительные блоки, первые входы первых двух из которых подключены к соответствующим входам задания постоянных коэффициентов устройства, а вторые входы этих блоков подключены соответственно ко входам вещественной и мнимой части первого комплексного числа устройства, сумматоры и регистры, отличающееся тем, что, с целью упрощения устройства, оно содержит два сумматора-вычитателя, первые входы которых подключены соответственно ко входам вещественной и мнимой части второго комплексного числа устройства, а выходы этих блоков соединены со входами соответствуюищх регистров, выходы которых являются выходами устройства, входы вещественной и ,мнимой части первого комплексного 1исла устройства и входы задания постоянных коэффициентов устройства соединены соответственно со входами первого и второго сумматоров.

выходы которых соединены со входами третьего множительного блока, выход которого соединен с первыми входами третьего и четвертого сумматоров, вторые входы которых подключены соответственно к выходам первого и второго множительного блока, а выходы третьего и четвертого сумматоров соединены со входами соответствующих сумматоров-вычитателей.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 480079, кл. G06 F 15/34, 1973.

2.Авторское свидетельство СССР 421994, кл. G06 F 15/34, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

л и

/ и

t8

tL л:

/g 1 fj

L. U-j-J U... Ф 4f

20HIгггз

Фш 1

Авторы

Даты

1979-04-05—Публикация

1977-04-19—Подача