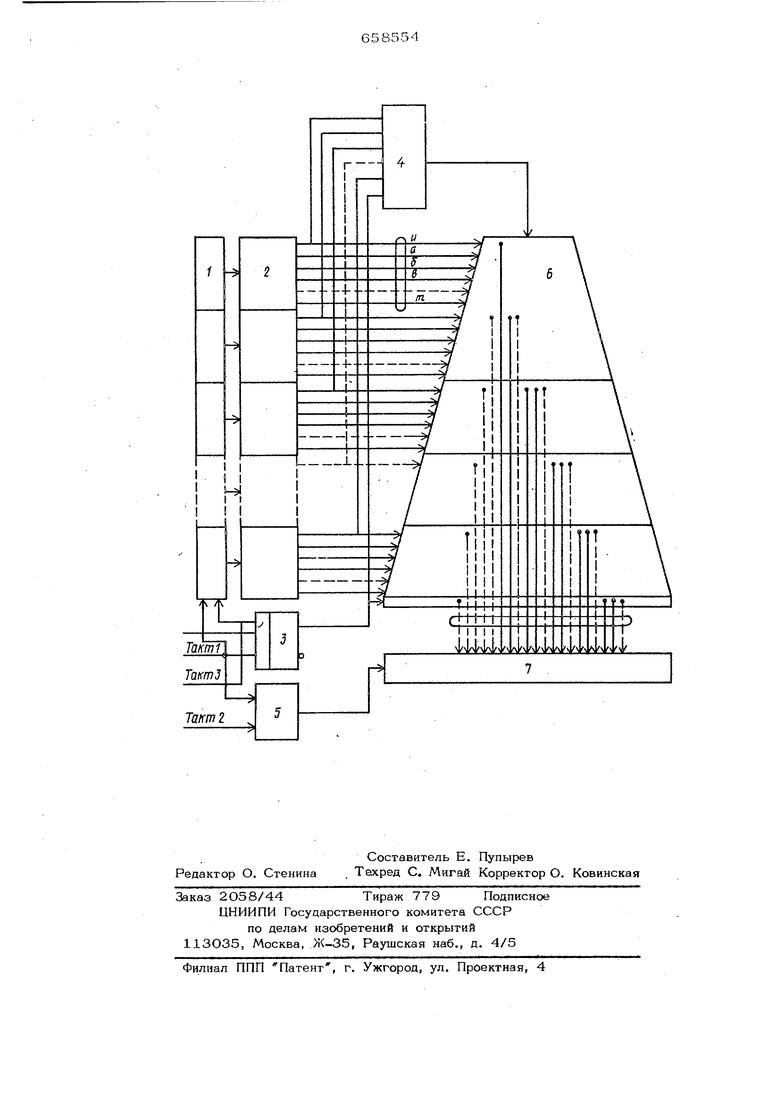

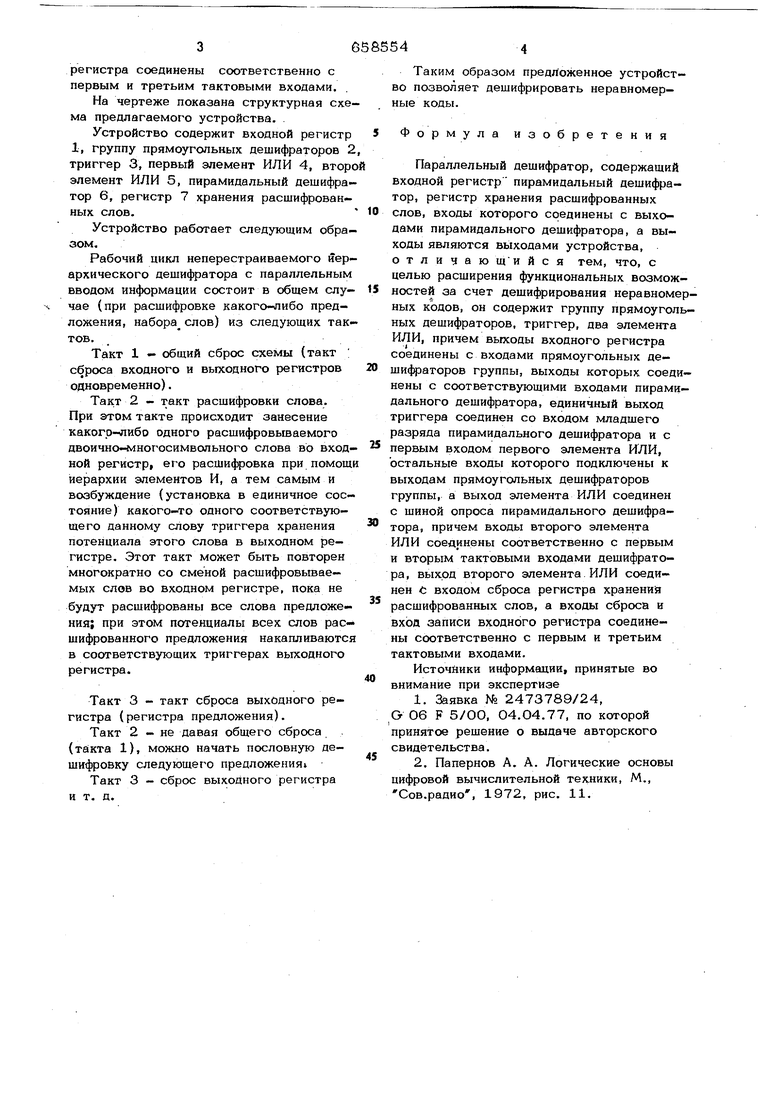

регистра соединены соответственно с первым и третьим тактовыми входами. На чертеже показана структурная схе ма предлагаемого устройства. . Устройство содержит входной регистр 1, группу прямоугольных дешифраторов 2 триггер 3, первый элемент ИЛИ 4, втор элемент ИЛИ 5, пирамидальный дешифратор 6, регистр 7 хранения расшифрованных слов. Устройство работает следующим образом. Рабочий цикл неперестраиваемого иерархического дешифратора с параллельным вводом информации состоит в общем случае (при расшифровке какого-либо предложения, набора слов) из следующих тактов. Такт 1 - общий сброс схемы (такт ; сброса входного и выходного регистров одновременно). Такт 2 - такт расшифровки слова. При этом такте происходит занесение какогр- ибо одного расщифровьшаемого двоично- 1ногосимвольного слова во входной регистр, его расши4чэовка при помощ иерархии элементов И, а тем самым и возбуждение (установка в единичное состояние) какого-то одного соответствующего данному слову триггера хранения потенциала этого слова в выходном регистре. Этот такт может быть повторен многократно со сменой расшифровываемых слов во входном регистре, пока не будут расшифрованы все слова предложения; при этом потенциалы всех слов расшифрованного предложения накапливаются в соответствующих триггерах выходного регистра. Такт 3 - такт сброса выходного регистра (регистра предложения). Такт 2 - не давая общего сброса (такта 1), можно начать пословную дешифровку следующего предложения1 Такт 3 - сброс выходного регистра и т. д. Таким образом предложенное устройство позволяет дешифрировать неравномерные коды. Формула изобретения Параллельный дешифратор, содержащий входной регистр пирамидальный дешифратор, регистр хранения расшифрованных слов, входы которого соединены с выходами пирамидального дешифратора, а выходы являются выходами устройства, отличаю щийся тем, что, с целью расширения функциональных возможностей за счет дешифрирования неравномерных кодов, он содержит группу прямоугольных дешифраторов, триггер, два элемента ИЛИ, причем выходы входного регистра соединены с входами прямоугольных дещи(|раторов группы, выходы которых соединены с соответствующими входами пирамидального дешифратора, единичный выход триггера соединен со входом младшего разряда пирамидального дещифратора и с первым входом первого элемента ИЛИ, остальные входы которого подключены к выходам прямоугольных дешифраторов группы, а выход элемента ИЛИ соединен с шиной опроса пирамидального дешифратора, причем входы второго элемента ИЛИ соединены соответственно с первым и вторым тактовыми входами дешифратора, выход второго элемента ИЛИ соединен t входом сброса регистра хранения расшифрованных слов, а входы сброса и вход записи входного регистра соединены соответственно с первым и третьим тактовыми входами. Источники информации, принятые во внимание при экспертизе 1.Заявка № 2473789/24, G 06 F 5/00, 04.04.77, по которой принятое решение о выдаче авторского свидетельства. 2.Папернов А. А. Логические основы цифровой вычислительной техники, М., Сов.радио , 1972, рис. 11.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный дешифратор | 1977 |

|

SU734665A1 |

| Последовательный дешифратор | 1977 |

|

SU705442A1 |

| Последовательный дешифратор слов | 1982 |

|

SU1043626A1 |

| Последовательный дешифратор слов | 1981 |

|

SU978138A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство распознавания многосимвольных слов | 1980 |

|

SU938279A1 |

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU855651A1 |

| Устройство для сопряжения абонентов с ЦВМ | 1990 |

|

SU1755289A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

Авторы

Даты

1979-04-25—Публикация

1977-04-04—Подача