(54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ

1

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в различного типа счетно-решающих устройствах, системах и приборах автоматического контроля и регулирования, а также в других, устройствах, осуществляющих преобразование дискретной информации.

Известен преобразователь параллельного кода в последовательный, содержащий регистр хранения информации, выполненный на триггерах, подключенных через двухвходовые первые и вторые элементы И к выходному триггеру, и распределитель импульсов, выходы которого соединены со вторыми первых и вторых элементов И, первые входы которых соединены с выходами триггеров регистра хранения, а выходы всех перклх и выходы всех вторых элементов И соответственно объединены в группы и подсоединены к единичному и нулевому входам выходного триггера, выход которого подсоединен к выходу преобразователя l.

Недостаток данного преобразователя состоит в невозможности его ис-.

пользования при большой частоте обмена информационными словгши.

Наиболее близким к предлагаемому является преобразователь параллельного кода в последовательный, содержащий сдви,говый регистр, группу элементов И и выходной элемент И 2.

Недостатком данного преобразователя является относительно низкое

10 быстродействие.

Цель изобретения - увеличение быстродействия преобразователя.

Поставленная цель достигается тем, что в преобразоват.ель параллельного кода в последовательный, со15держгшщй сдвиговый регистр, группу элементов И и выходной элемент И, введены дешифратор, регистр управления, входной счетчик, элемент И,

20 счетчик управления, ко1««утатор и группа сдвиговых регистров, причем выходы старших разрядов всех сдвиговых регистров соединены с информационными входами коммутатора, управля25ющие входы которого соединены с выходами счетчика управления, а выход коммутатора соединен с первым входом выходного элемента И, второй вход котсфого соединен с тактовым входом 30 преобразователя, с первыми входами

элементов И, с тактовым входом входного счетчика и с первым входом элемента И, остальные входы которого соединены с выходами входного счетчика, а выход элемента И соединен с управляющими входами счетчика управления и регистра управления, выходы которого соединены со вторыми входами элементов И группы, выходы которых соединены со входами сдвига соответствующих сдвиговых регистров, управляющие входы которых соединены с соответствующими выходами дешифратора, а информационные входы сдвиговых регистров являются информационными входами преобразователя, вход дешифратора является адресным входом преобразователя, вход сброса входного счетчика, счетчика управления и регистра управления является входом сброса преобразователя, а выход выходного элемента И является выходом преобразователя.

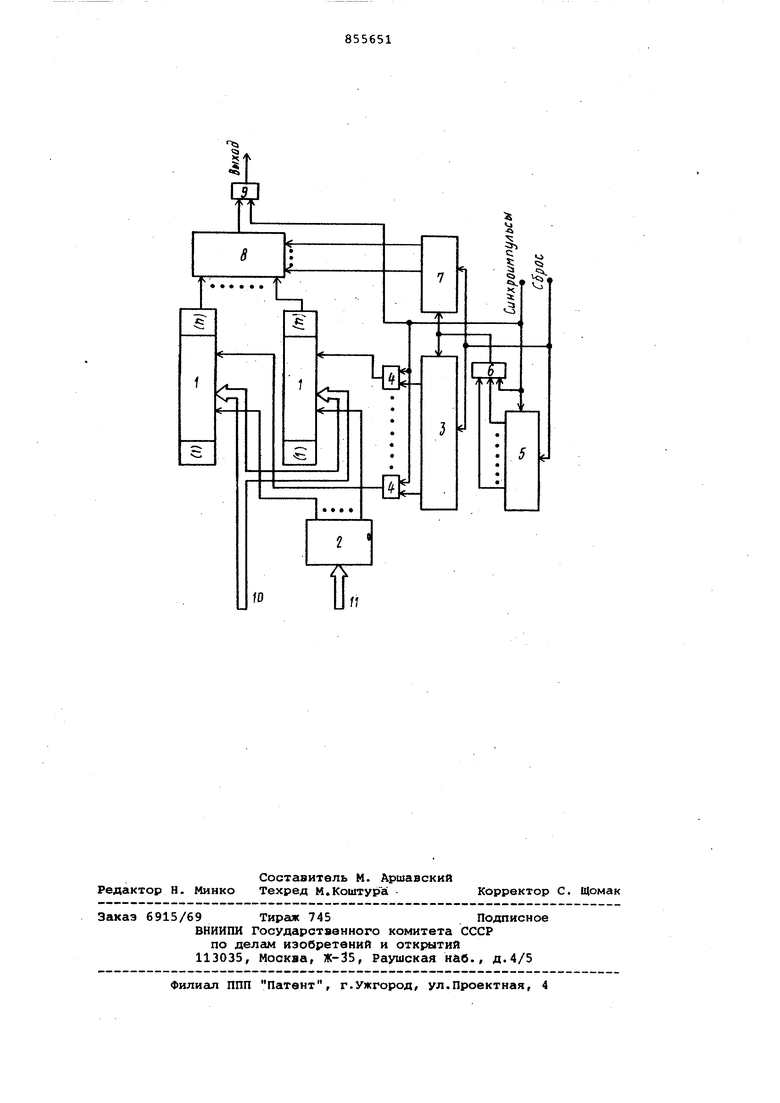

На чертеже представлена функциональная схема преобразователя параллельного кода в последовательный.

Преобразователь параллельного кода в последовательный содержит п сдвиговых регистров 1, дешифратор 2 регистр 3 управления, представляющий собой кольцевой сдвиганадий регистр, группу из п элементов И 4, входной счетчик 5, элемент И б, счетчик 7 управления, коммутатор 8, дыходной элемент И 9. Выходы дешифратора 2 соединены с стробирующими входами соответствующих сдвиговых регистров 1, выходы последних разрядов которых соединены с информационными входами коммутатора 8, управляющие входы которого соединены с выходами разрядов счетчика 7 управления, управляющий счетный вход которого объединен со входом регистра 3 управления и с выходом элемента И 6. Входы элемента И б соединены с выходами разрядов входного счётчика 5 и с тактовым входом преобразователя. Этот вход также соединен со вторым входом выходного элемента И 9 и элементов И 4, группы, первые входы которых соединены соответственно с выходом коммутатора 8 и с выходами соответствующих разрядов регистра 3 управления, а выходы элементов И 4 группы соединены с тактовыми входами соответствующих сдвиговых регистров 1. Вход сброса соединен с установочными входами регистра 3 управление, входного счетчика 5 и счетчика 7 управления. Вход 10 пода и параллельного кода в сдвиговый регистр 1 соединен с информационными входами сдвиговых регистров 1 хранении, адресный вход 11 со входами дешифратора 2.

Устройство для преобразования параллельного кода в последовательный работает следующим образом.

Через вход 10 в сдвиговые регистры 1 подается параллельный код, который необходимо перобразовать в последовательный, а через вход 11 одновременно с преобразуемым кодом в дешифратор 2 подается его адрес. Расшифрованный дешифратором 2 адрес производит запись информации в соответствующий сдвиговый регистр 1. Таким образом, массив информации, подлежащий преобразованию, записыва0 15 20 25 ется с большой частеотой в соответствующие регистры 1.Затем происходит процесс преобразования информации. По входу сброса поступает сиг- . нал, который обнуляет входной счетчик 5, счетчик 7 управления и все, кроме первого, разряды регистра 3 управления, а его первый разряд устанавливается в При этом в начальный момент времени регистр 3 управления открывает элемент И 4 группы, управляемый импульсами сдвига первого регистра 1, 5 счетчик 7 управления, выдавая сигналы на управляющие входы коммутатора 8, открывает вход для информации, поступающей с первого регистра 1. По тактовому входу поступает п пачек синхроимпульсов, по числу сдвиговых регистров 1 - по шестнадцать синхроимпульсов в каждой пачке. Синхроимпульсы поступают на вход входного счетчика 5, который работает по модулю 16 и на входы выходного элемента

5 И 9 и элементов И 4 группы. При этом каждый синхроимпульс стробирует информацию, поступающую с выхода коммутатора 8, на вход выходного элемента И 9 проходит через открытый элемент И 4 группы на вход соответствующего регистра 1, осуществляя по заднему фронту сдвиг информации в нем и увеличивая содержимое входного счетчика 5. Таким образом, синхроимпульсы пачки пройдут через открытый элемент И 4 группы на вход соответствующего регистра 1, осущест5 50 55 вив его полный сдвиг, с одновременным стробированием каждого бита информации на входе выходного элемента И 9 и выдачи его на выход преобразователя. Входной счетчик 5 по заднему фронту каждого пятнадцатого синхроимпульса каждой пачки открывает элемент И б и шестнадцатый синхроимпульс каждой пачки проходит на выход элемента И 6 и осуществляет сдвиг единицы в регистре 3 управления, произйодит переключение синхроимпульсов на сдвиг информации в следующем регистре 1 и изменение счетчика 7 управления на единицу, осуще0 65 ствляя переключение следующего входа коммутатора 8 на его выход. Получается, что каждая пачка синхроимпульсов производит сдвиг информации в соответствующем регистре 1 и осу-, ществляет его по заднему фронту

шестнадцатого синхроимпульса пачки переключение синхроимпульсов на вход следующего регистра 1, и соответственно подключение его выхода коммутатором 8 на вход выходного элемента И 9. По окончании преобразования всей информации устройство находится в исходном состоянии.

Данный преобразователь по сравнению с известным обеспечивает повышение быстродействия на величину, определяемую временем преобразования одного информационного слова. Это достигается тем, что в отличив от известного, который каждое принятре информационное слово сразу преобразовывает, предлагаемое устройство принимает весь массив входной информации, а затем его преобразовывает. Такое построение исключает возможность искажений последукхцей входной информации на момент преобразования предыдущей.

Формула изобретения

Преобразователь параллельного кода в последовательный, содержащий сдвиговый регистр, группу элементов И и выходной элемент И, отличающийся тем, что, с целью увеличения быстродействия, в него введены дешифратор, регистр управления, входной счетчик, элемент И, счетчик управления, коммутатор и группа сдвиговых регистров, причем выходы старших разрядов всех сдвиговых регистров соединены с информадионными входами коммутатора, упранлякщие входы которого соединены с выходами счётчика управления, а выход коммутатора соединен с первым входом выходного элемента И, второй вход которого соединен с тактовым входом преобразователя, с порвым 1 входами элементов И группы,с тактовым входом входного счетчика и с первым входом элемента И, остальные входы которого соединены с выходами

0 входного счетчика, а выход элемента И соединен с управляющими входами счетчика управления и регистра управления, выходы которого соединены со вторыми входами элементов И

5 группы, выходы которых соединены со входаили сдвига соответствующих сдвиговых регистров, управляющие входы которых соединены с соответствующими уходами дешифратора, а информаци0онные входы сдвиговых регистров являются информационными входами преобразователя, вход дешифратора является с1дресным входом преобразователя, вход сброса входного счетчика, счетчика управления и регистра

5 управления является входом сброса преобразователя, а выход выходного элемента И является выходом преобразователя .

Источники информации,

0 принятые во внимание при экспертизе

1.Иляпоберский В.И..Основы техники передачи дискретных сообщений. М., Связь, 1973, с. 141, рис.3,31.

2.Авторское свидетельство СССР

5 №. 217712, кл. G 06 F 5/04, 06.02.67 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1982 |

|

SU1075253A1 |

| Преобразователь параллельного кода в последовательный | 1989 |

|

SU1644390A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

Авторы

Даты

1981-08-15—Публикация

1979-11-11—Подача