Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля и диагностики цифровых блоков радиоэлектронной аппаратуры,

Целью изобретения является расширение функциональных возможностей устройства за счет формирования импульсных входных воздействий переменной длительности и независимого изменения задержки считывания по каждому каналу.

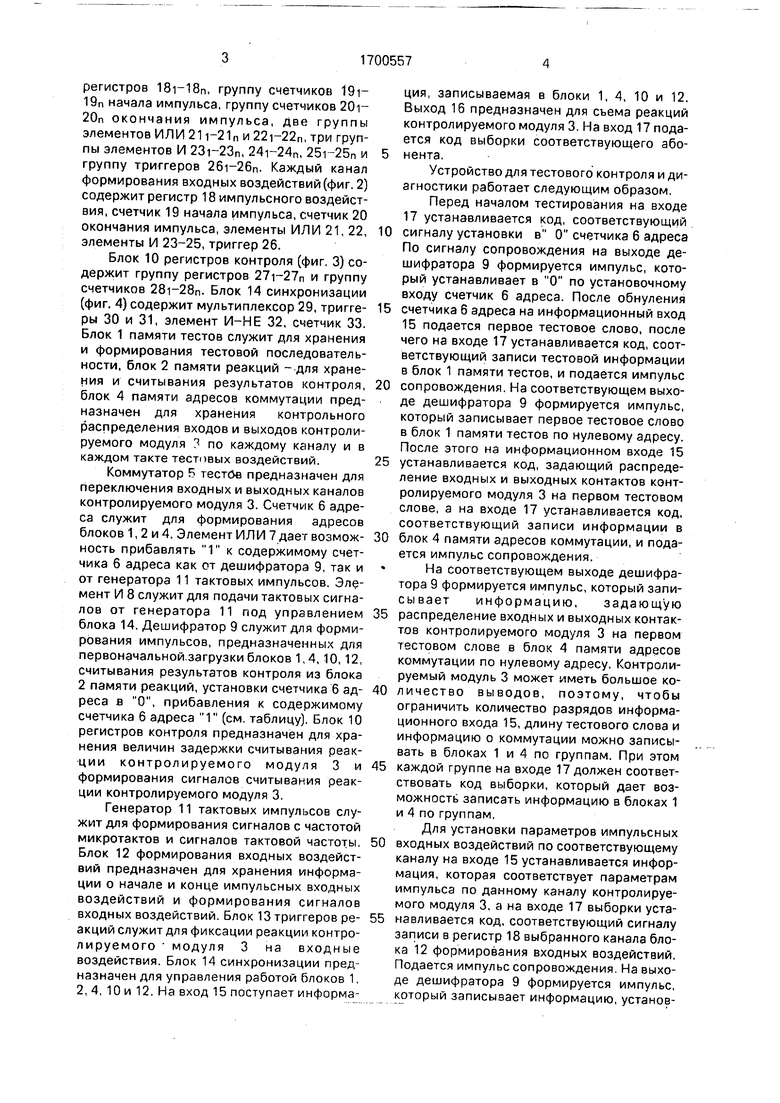

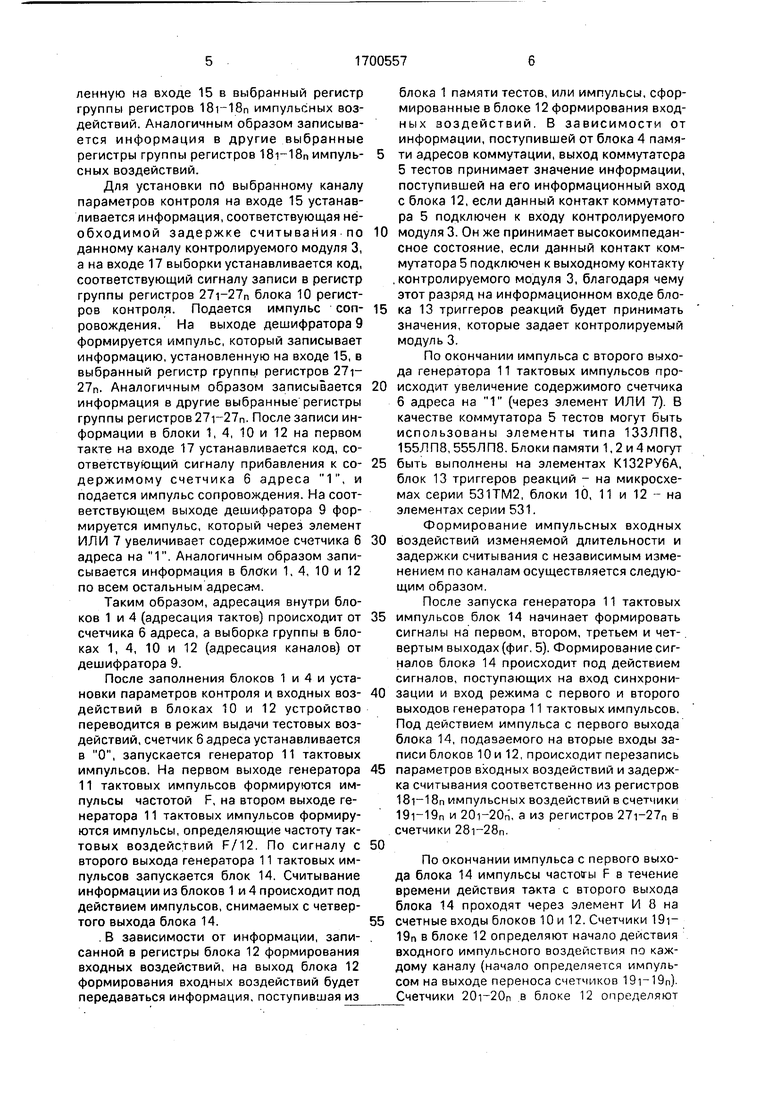

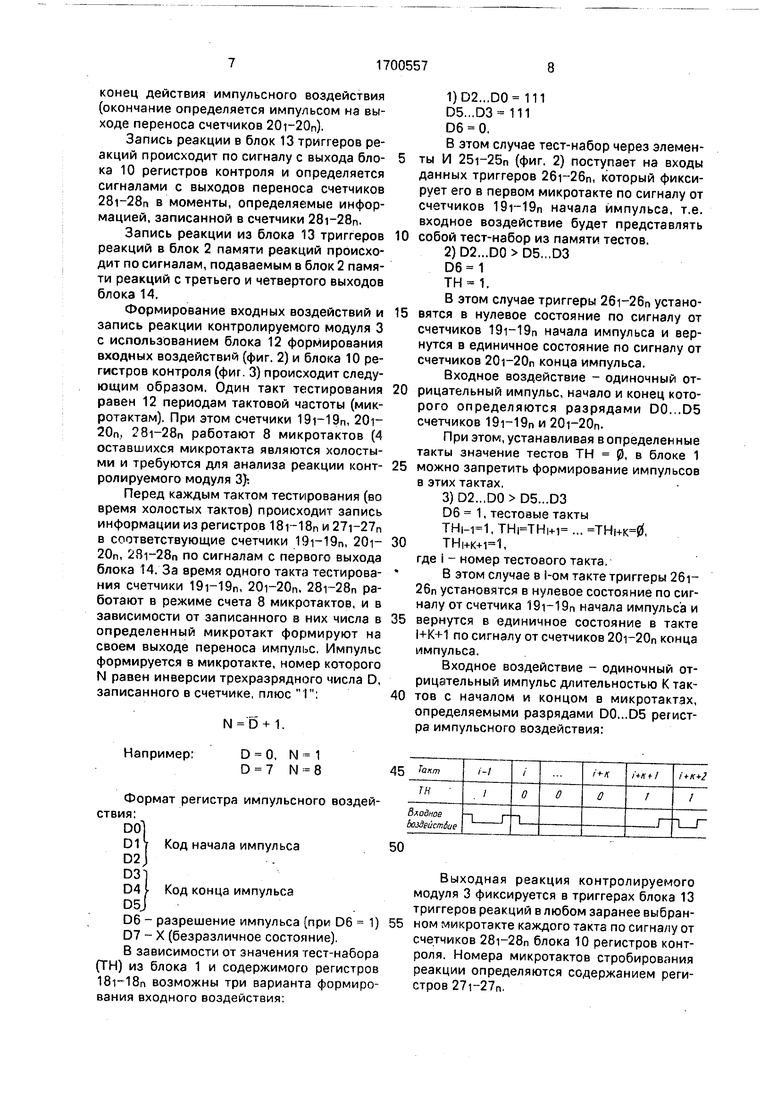

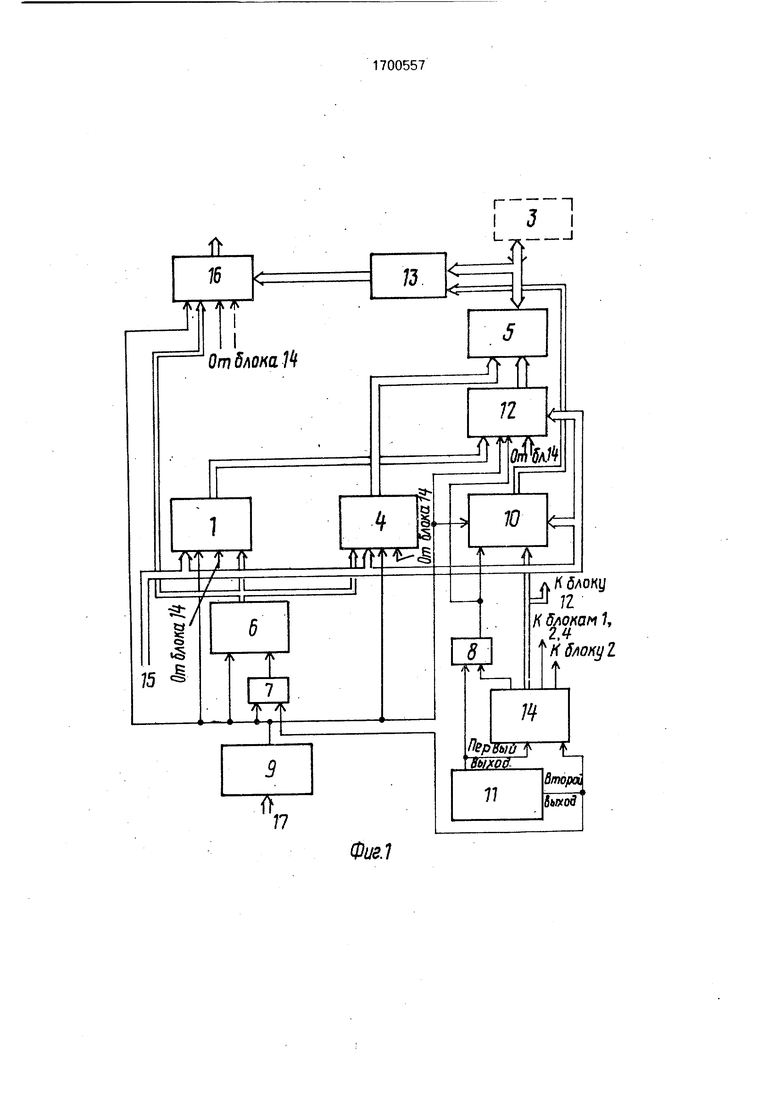

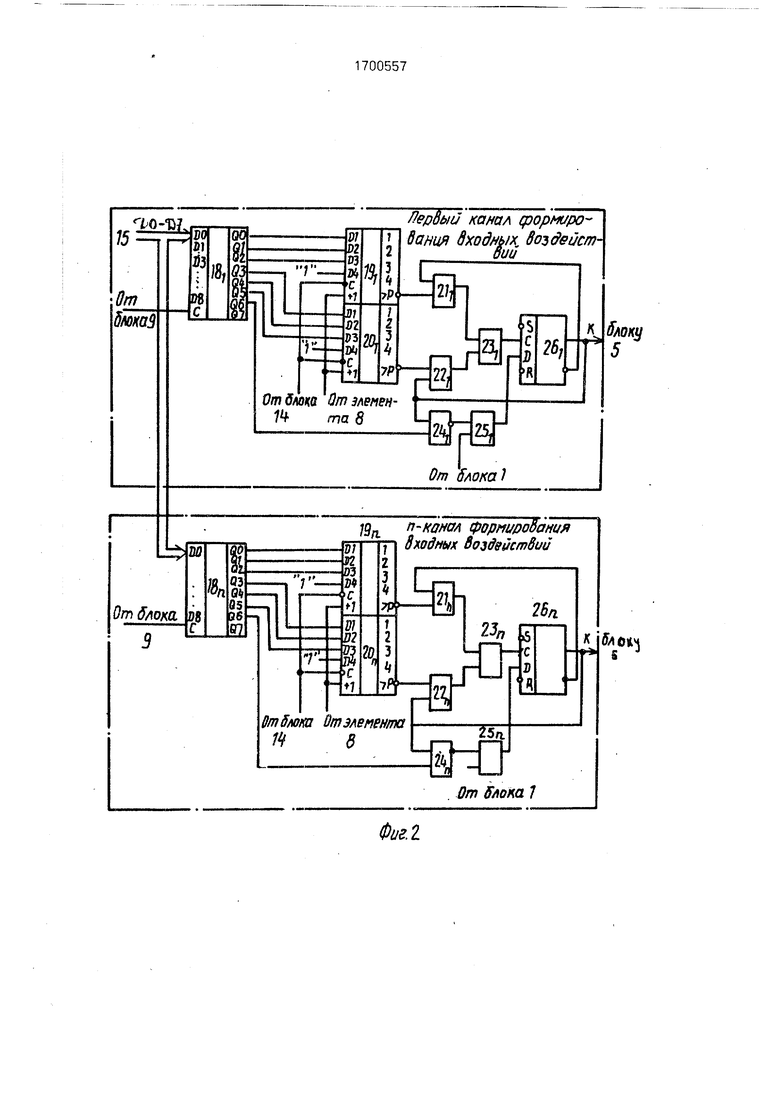

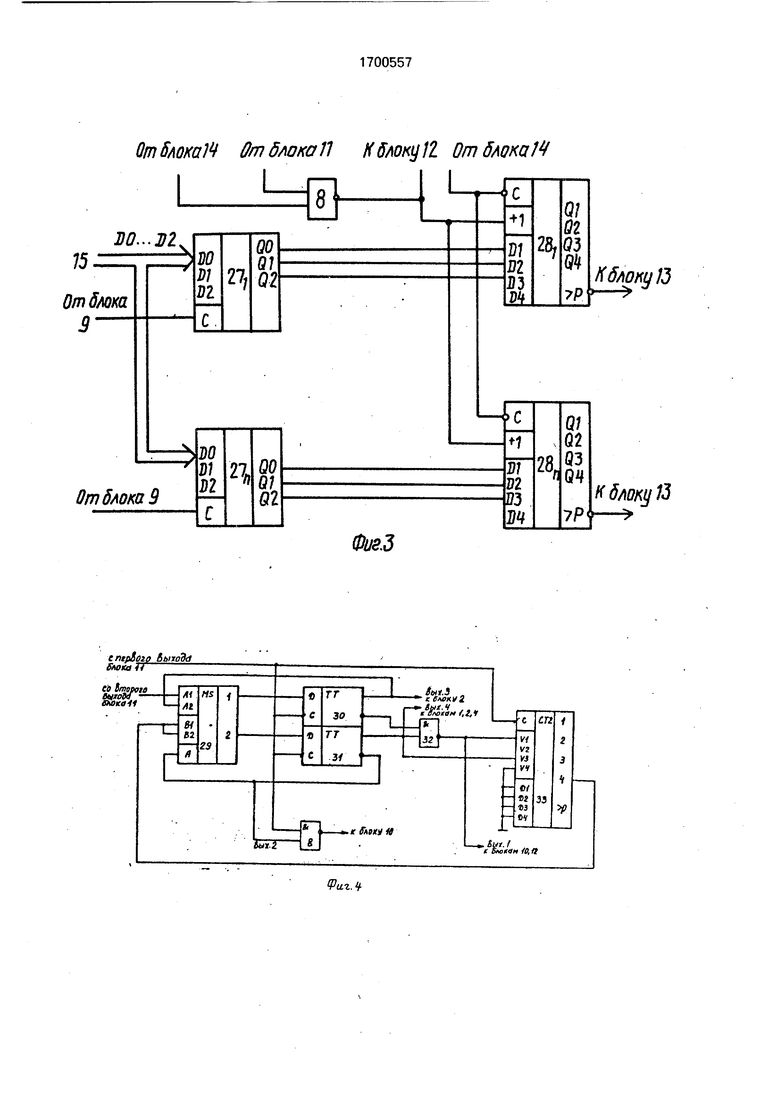

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема блока формирования входных воздействий; на фиг. 3 - функциональная схема блока регистров контроля; на фиг. 4 - функциональная схема блока синхронизации; на фиг. 5 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит блок 1 памяти тестов, блок 2 памяти реакций, контролируемый модуль 3, блок 4 памяти адресов коммутации, коммутатор 5 тестов, счетчик 6 адреса, элемент ИЛИ 7, элемент И 8, дешифратор 9, блок 10 регистров контооля, генератор 11 тактовых импульсов, блок 12 формирования входных воздействий, блок 13 триггеров реакций, блок 14 синхронизации. Устройство имеет информационный вход 15, информационный выход 16 и вход 17 выбора режима

Блок 12 формирования входных воздействий образован группой каналов входных воздействий. Блок 12 формирования входных воздействий (фиг 2) содержит группу

VI

О О СЛ

сл

VI

регистров 18i-18n, группу счетчиков 19i 19П начала импульса, группу счетчиков 20i- 20п окончания импульса, две группы элементов ИЛИ и , три группы элементов И 23i-23n, 24i-24n, 25i-25n и группу триггеров 26i-26n. Каждый канал формирования входных воздействий (фиг. 2) содержит регистр 18 импульсного воздействия, счетчик 19 начала импульса, счетчик 20 окончания импульса, элементы ИЛИ 21, 22, элементы И 23-25, триггер 26.

Блок 10 регистров контроля (фиг. 3) содержит группу регистров 27i-27n и группу счетчиков 28-|-28п. Блок 14 синхронизации (фиг. 4) содержит мультиплексор 29, триггеры 30 и 31, элемент И-НЕ 32, счетчик 33. Блок 1 памяти тестов служит для хранения и формирования тестовой последовательности, блок 2 памяти реакций - для хранения и считывания результатов контроля, блок 4 памяти адресов коммутации предназначен для хранения контрольного распределения входов и выходов контролируемого модуля 3 по каждому каналу и в каждом такте тестовых воздействий.

Коммутатор Б тестов предназначен для переключения входных и выходных каналов контролируемого модуля 3. Счетчик 6 адреса служит для формирования адресов блоков 1, 2 и 4. Элемент ИЛИ 7 дает возможность прибавлять 1 к содержимому счетчика б адреса как от дешифратора 9, так и от генератора 11 тактовых импульсов. Элемент И 8 служит для подачи тактовых сигналов от генератора 11 под управлением блока 14. Дешифратор 9 служит для формирования импульсов, предназначенных для первоначальной.загрузки блоков 1,4,10,12, считывания результатов контроля из блока 2 памяти реакций, установки счетчика 6 адреса в О, прибавления к содержимому счетчика 6 адреса 1 (см. таблицу). Блок 10 регистров контроля предназначен для хранения величин задержки считывания реакции контролируемого модуля 3 и формирования сигналов считывания реакции контролируемого модуля 3.

Генератор 11 тактовых импульсов служит для формирования сигналов с частотой микротактов и сигналов тактовой частоты. Блок 12 формирования входных воздействий предназначен для хранения информации о начале и конце импульсных входных воздействий и формирования сигналов входных воздействий. Блок 13 триггеров реакций служит для фиксации реакции контро- лируемого модуля 3 на входные воздействия. Блок 14 синхронизации предназначен для управления работой блоков 1, 2, 4, 10 и 12. На вход 15 поступает информация, записываемая в блоки 1,4, 10 и 12. Выход 16 предназначен для сьема реакций контролируемого модуля 3. На вход 17 подается код выборки соответствующего абонента.

Устройство для тестового контроля и диагностики работает следующим образом.

Перед началом тестирования на входе 17 устанавливается код, соответствующий

0 сигналу установки в 0 счетчика 6 адреса По сигналу сопровождения на выходе дешифратора 9 формируется импульс, который устанавливает в О по установочному входу счетчик 6 адреса. После обнуления

5 счетчика 6 адреса на информационный вход 15 подается первое тестовое слово, после чего на входе 17 устанавливается код, соответствующий записи тестовой информации в блок 1 памяти тестов, и подается импульс

0 сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который записывает первое тестовое слово в блок 1 памяти тестов по нулевому адресу. После этого на информационном входе 15

5 устанавливается код, задающий распределение входных и выходных контактов контролируемого модуля 3 на первом тестовом слове, а на входе 17 устанавливается код, соответствующий записи информации в

0 блок 4 памяти адресов коммутации, и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который запи- сывает информацию, задающую

5 распределение входных и выходных контактов контролируемого модуля 3 на первом тестовом слове в блок 4 памяти адресов коммутации по нулевому адресу. Контролируемый модуль 3 может иметь большое ко0 личество выводов, поэтому, чтобы ограничить количество разрядов информационного входа 15, длину тестового слова и информацию о коммутации можно записывать в блоках 1 и 4 по группам. При этом

5 каждой группе на входе 17 должен соответствовать код выборки, который дает возможность записать информацию в блоках 1 и 4 по группам.

Для установки параметров импульсных

0 входных воздействий по соответствующему каналу на входе 15 устанавливается информация, которая соответствует параметрам импульса по данному каналу контролируемого модуля 3, а на входе 17 выборки уста5 навливается код, соответствующий сигналу записи в регистр 18 выбранного канала блока 12 формирования входных воздействий. Подается импульс сопровождения. На выходе дешифратора 9 формируется импульс, который записывает информацию, установленную на входе 15 в выбранный регистр группы регистров импульсных воздействий. Аналогичным образом записывается информация в другие выбранные регистры группы регистров 181-18пимпуль- сных воздействий.

Для установки по выбранному каналу параметров контроля на входе 15 устанавливается информация, соответствующая необходимой задержке считывания по данному каналу контролируемого модуля 3, а на входе 17 выборки устанавливается код, соответствующий сигналу записи в регистр группы регистров 27i-27n блока 10 регистров контроля. Подается импульс con- ровождения. На выходе дешифратора 9 формируется импульс, который записывает информацию, установленную на входе 15, в выбранный регистр группы регистров 27т- 27П. Аналогичным образом записывается информация в другие выбранные регистры группы регистров 27i-27n. После записи информации в блоки 1, 4, 10 и 12 на первом такте на входе 17 устанавливается код, соответствующий сигналу прибавления к со- держимому счетчика 6 адреса 1, и подается импульс сопровождения. На соответствующем выходе дешифратора 9 формируется импульс, который через элемент ИЛИ 7 увеличивает содержимое счетчика 6 адреса на 1. Аналогичным образом записывается информация в блоки 1,4, 10 и 12 по всем остальным адресам.

Таким образом, адресация внутри блоков 1 и 4 (адресация тактов) происходит от счетчика 6 адреса, а выборка группы в блоках 1, 4, 10 и 12 (адресация каналов) от дешифратора 9.

После заполнения блоков 1 и 4 и установки параметров контроля и входных воз- действий в блоках 10 и 12 устройство переводится в режим выдачи тестовых воздействий, счетчик 6 адреса устанавливается в О, запускается генератор 11 тактовых импульсов. На первом выходе генератора 11 тактовых импульсов формируются импульсы частотой F, на втором выходе генератора 11 тактовых импульсов формируются импульсы, определяющие частоту тактовых воздействий F/12. По сигналу с второго выхода генератора 11 тактовых импульсов запускается блок 14. Считывание информации из блоков 1 и 4 происходит под действием импульсов, снимаемых с четвертого выхода блока 14.

. В зависимости от информации, запи- санной в регистры блока 12 формирования входных воздействий, на выход блока 12 формирования входных воздействий будет передаваться информация, поступившая из

блока 1 памяти тестов, или импульсы, сформированные в блоке 12 формирования входных зоздействий. В зависимости от информации, поступившей от блока 4 памяти адресов коммутации, выход коммутатора

5тестов принимает значение информации, поступившей на его информационный вход с блока 12, если данный контакт коммутатора 5 подключен к входу контролируемого модуля 3. Он же принимает высокоимпедан- сное состояние, если данный контакт коммутатора 5 подключен к выходному контакту

.контролируемого модуля 3, благодаря чему этот разряд на информационном входе блока 13 триггеров реакций будет принимать значения, которые задает контролируемый модуль 3.

По окончании импульса с второго выхода генератора 11 тактовых импульсов происходит увеличение содержимого счетчика

6адреса на 1 (через элемент ИЛИ 7). В качестве коммутатора 5 тестов могут быть использованы элементы типа 133ЛП8, 155ЛП8.555ЛП8. Блоки памяти 1,2 и 4 могут быть выполнены на элементах К132РУ6А, блок 13 триггеров реакций - на микросхемах серии 531ТМ2, блоки 10, 11 и 12 - на элементах серии 531.

Формирование импульсных входных воздействий изменяемой длительности и задержки считывания с независимым изменением по каналам осуществляется следующим образом.

После запуска генератора 11 тактовых импульсов блок 14 начинает формировать сигналы на первом, втором, третьем и чет-, вертым выходах (фиг, 5). Формирование сигналов блока 14 происходит под действием сигналов, поступающих на вход синхронизации и вход режима с первого и второго выходов генератора 11 тактовых импульсов. Под действием импульса с первого выхода блока 14, подаваемого на вторые входы записи блоков 10 и 12, происходит перезапись параметров входных воздействий и задержка считывания соответственно из регистров 18i-18n импульсных воздействий в счетчики 19i-19n и 20i-20n, а из регистров в счетчики 28i-28n.

По окончании импульса с первого выхода блока 14 импульсы частогы F в течение времени действия такта с второго выхода блока 14 проходят через элемент И 8 на счетные входы блоков 10 и 12. Счетчики 19i 19П в блоке 12 определяют начало действия входного импульсного воздействия по каждому каналу (начало определяется импульсом на выходе переноса счетчиков 19i-19n). Счетчики в блоке 12 определяют

конец действия импульсного воздействия (окончание определяется импульсом на выходе переноса счетчиков 20t-20n).

Запись реакции в блок 13 триггеров реакций происходит по сигналу с выхода блока 10 регистров контроля и определяется сигналами с выходов переноса счетчиков в моменты, определяемые информацией, записанной в счетчики 28i-28n.

Запись реакции из блока 13 триггеров реакций в блок 2 памяти реакций происходит по сигналам, подаваемым в блок 2 памяти реакций с третьего и четвертого выходов блока 14.

Формирование входных воздействий и запись реакции контролируемого модуля 3 с использованием блока 12 формирования входных воздействий (фиг. 2) и блока 10 регистров контроля (фиг. 3) происходит следующим образом. Один такт тестирования равен 12 периодам тактовой частоты (микротактам), При этом счетчики , 20i- 20n, 28i-28n работают 8 микротактов (4 оставшихся микротакта являются холостыми и требуются для анализа реакции контролируемого модуля 3):

Перед каждым тактом тестирования (во время холостых тактов) происходит запись информации из регистров и 27i-27n в соответствующие счетчики 19i-19n, 20i- 20n, 28i-28n no сигналам с первого выхода блока 14. За время одного такта тестирования счетчики 19i-19n, 20i-20n. 28r-28n работают в режиме счета 8 микротактов, и в зависимости от записанного в них числа в определенный микротакт формируют на своем выходе переноса импульс, Импульс формируется в микротакте, номер которого N равен инверсии трехразрядного числа D, записанного в счетчике, плюс

Например:

N D+ 1.

0 0, N 1

D 7 N 8

1)D2.,,DO 111 05...03 111 06 0,

В этом случае тест-набор через элемен- ты И 25i-25n (фиг. 2) поступает на входы данных триггеров , который фиксирует его в первом микротакте по сигналу от счетчиков 19i-19n начала импульса, т.е. входное воздействие будет представлять 0 собой тест-набор из памяти тестов. 2) 02...00 05.,.03 06 1 ТН-1.

В этом случае триггеры 26i-26n устано- 5 вятся в нулевое состояние по сигналу от счетчиков 19i-19n начала импульса и вернутся в единичное состояние по сигналу от счетчиков 20i-20n конца импульса.

Входное воздействие - одиночный от- 0 рицательный импульс, начало и конец которого определяются разрядами 00.,.05 счетчиков 19i-19n и .

При этом, устанавливая в определенные такты значение тестов ТН 0, в блоке 1 5 можно запретить формирование импульсов в этих тактах.

3)D2......D3 Об 1, тестовые такты THi-i 1, THi THi+i ... ТН1+к 0, 0 ТН|+к-м 1,

где i - номер тестового такта.

В этом случае в l-ом такте триггеры 26i- 26П установятся в нулевое состояние по сигналу от счетчика 19i-19n начала импульса и 5 вернутся в единичное состояние в такте I+K+1 по сигналу от счетчиков 20ч-20п конца импульса.

Входное воздействие - одиночный отрицательный импульс длительностью К так- 0 тов с началом и концом в микротактах, определяемыми разрядами 00...05 регистра импульсного воздействия:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| СИСТЕМА ФОРМИРОВАНИЯ КАДРОВОГО СОСТАВА ИННОВАЦИОННОГО ПРОЕКТА | 2015 |

|

RU2610012C1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1406640A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля и диагностики цифровых блоков радиоэлектронной аппаратуры. Целью изобретения является расширение функциональных возможностей устройства за счет формирования импульсных входных воздействий переменной длительности и независимого изменения задержки считывания по каждому каналу. С этой целью в устройство, содержащее блок памяти тестов, блок памяти реакций, блок памяти адресов коммутации, коммутатор тестов, счетчик адреса, генератор тактовых импульсов, дешифратор, элемент ИЛИ, элемент И и блок регистров контроля, введены блок формирования входных воздействий, блок синхронизации и блок триггеров реакций. 1 з.п.ф-лы, 5 ил., 1 табл. сл с

Формат регистра импульсного воздействия:DOl

01 02 03 D4 05

I

Код начала импульса

Код конца импульса

06- разрешение импульса {при Об 1)

07- X (безразличное состояние).

8зависимости от значения тест-набора (ТН) из блока 1 и содержимого регистров 18i-18n возможны три варианта формирования входного воздействия:

50

Выходная реакция контролируемого модуля 3 фиксируется в триггерах блока 13 триггеров реакций в любом заранее выбран- ном микротакте каждого такта по сигналу от счетчиков 28i-28n блока 10 регистров контроля. Номера микротактов стробирования реакции определяются содержанием регистров 27i-27n,

Информация из блока 13 триггеров реакций переписывается в блок 2 памяти реакций в начале следующего такта по сигналам с третьего и четвертого выходов блока 14.

Блок 14 синхронизации (фиг. 5) работает следующим образом. Перед приходом очередного сигнала /Пуск триггеры 30 и 31 находятся в единичном состоянии (/Т1 /Т2 1), старший выход счетчика 33 /Т3 1.

Синхросигнал /Пуск О через мультиплексор 29 поступает на информационный вход триггера 30, и по первому импульсу F (фиг. 5) триггер 30 устанавливается в нулевое состояние, формируя , который через мультиплексор 29 поступает на информационный вход триггера 31. Сигналы с инверсного выхода триггера 30 и с прямого выхода триггера 31, поступая на элемента И-НЕ 32, формируют сигнал , который поступает на вход разрешения записи счетчика 33, По второму импульсу F в счетчик 33 по всем разрядам записываются О, установленные на его информационных входах. По второму импульсу F также устанавливается в нулевое состояние триггер 31, формируя , в результате чего сигнал , сигнал /Т2 О, поступая на вход разрешения счетчика 33, переводит его в режим счета. Сигнал с инверсного выхода триггера 31 Т2 1, поступив на вход управления мультиплексора 29, переводит его в режим коммутации второй группы входов, Счетчик 33 отсчитывает 8 тактов частоты F, и по десятому импульсу F на его старшем выходе сигнал /ТЗ становится равным Т . Этот сигнал через мультиплексор 29 поступает на информационные входы триггеров 30 и 31. По одиннадцатому импульсу F триггеры 30 и 31 устанавливаются в единичное состояние. В результате схема установилась в исходное состояние и готова к следующему такту.

Формула изобретения

0 выход блока памяти адресов коммутации подключен к управляющему входу коммутатора тестов, выход которого является выходом устройства для подключения к входу контролируемого модуля, счетный вход бло5 ка регистров контроля соединен с выходом элемента И, а информационный выход блока памяти реакций является информационным выходом устройства, отличающее- с я тем, что, с целью расширения функцио0 нальных возможностей ус.ройства за счет формирования импульсных входных воздействий переменной длительности и независимого изменения задержки считывания по каждому каналу, оно содержит блок фор5 мирования входных воздействий, блок синхронизации и блок триггеров реакций, при этом первый и второй информационные входы, первый и второй входы записи, счетный вход и информационный выход блока фор0 мирования входных воздействий подключены соответственно к выходу блока памяти тестов, информационному входу устройства, седьмому выходу дешифратора, перпому выходу блока синхронизации, выходу эле5 мент И и информационному входу коммутатора тестов, первый и второй входы элемента И соединены соответственно с первым выходом генератора тактовых импульсов и вторым выходом блока синхрони0 зации, второй вход записи блока регистров контроля подключен к первому еыходу блока синхронизации, вход записи и выход блока триггеров реакций соединены соответственно с выходом блока регистров

5 контроля и информационны /, входом блока памяти реакций, информационный пход блока триггеров реакций являемся входом устройства для подключения ; выходу контролируемого модуля, вход записи блока пз0 мяти реакций соединен с третьим выходом блока синхронизации, четвертый РЫХОД которого подключен к входам разрешения обращения блока памятит ес ОБ, блока .ЗМРТИ реакций и блока памяти адресов коммута5 ции, синхровход блока синхронизации соединен с первым выходом генератора тактовых импульсов, второй выход которого подключен к входу запуска блокз синхронизации и второму входу элемента ИП / при этом блок формирования входных всздействий содержит группу регистров, две группы счетчиков, две группы элементов ИЛИ, три группы элементов И и группу триггеров, причем информационные входы и синхров- ходы регистров группы являются соответст- венно вторым информационным аходом и первым входом записи блока формирования входных воздействий, первая группа выходов регистров группы подключена к соответствующим информационным входам одноименных счетчиков первой группы, вторая группа выходов регистров группы подключена к соответствующим информационным входам одноименных счетчиков второй группы, третья группа выходов реги- стров группы соединена с первыми входами одноименных элементов И первой группы, вторые входы которых соединены с первыми входами одноименных элементов ИЛИ первой группы и подключены к соответству- ющим прямым выходам одноименных триггеров группы, инверсные выходы которых Соединены с первыми входами одноименных элементов ИЛИ второй группы, выходы переноса первой и второй групп подключе- ны к вторым входам элементов ИЛИ соответственно второй и первой групп, выходы которых соединены соответственно с первыми и вторыми входами одноименных элементов И второй группы, выходы которых подключены соответственно к синхровхо- дам одноименныхтриггеров группы, информационные входы которых соединены соответственно с выходами одноименных элементов И третьей группы, первые входы которых подключены к выходам одноименных элементов И первой группы, причем вторые входы элементов И третьей группы

таилицл лешифг

О

О

0000 0000

являются первым информационным входом блока, входы записи счетчиков первой и второй групп являются вторым входом записи блока, а счетные аходы счетчиков первой и второй групп являются счетным входом блока формирования входных воздействий, выходом блока формирования входных воздействий являются прямые выходы триггеров группы.

входных йодов 9

Аналогично } ( -7

ОУстановка счетчика 6

О Счет счетчика 6 через .элемент 7

Фиг. 1

g

C4l

rЮ LO

о

CD

r-

I,

ts

sgss lsggg y

I I I I I I I I I I I

ir§55ggggS

rf

g

I

i5

J

en

От блокам От блока 11 К блоку11 От блока М

е ntpSoiff kbitddd

еюим -

вйкан

К блоку 13

к блоку 13

ФигЗ

Фиг, 5

Времени

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-23—Публикация

1989-02-07—Подача