водами секционированной линии задержки, вход которой соединен с выходом трехвходового логического элемента Р1ЛИ, второй вход которого подключен к выходу логического элемента НЕ - И и иервому входу блока пересчета, второй вход которого соединен с выходом селектора, выход подключен ко второму входу логического элемента НЕ - И, а третий вход соединен с выходом многовходового логического элемента И, третий вход трехвходового логического элемента ИЛИ соединен с выходом элемента задержки и с первым входом второго логического элемента И, второй вход которого подключен к выходу секцнонировапной линии задержки, введены У 5-триггер, дополнительный элемент задержки, два дополнительных логических элемента И, двухвходовой и дополнительный трехвходовой логические элементы ИЛИ, выход последнего из которых соединен со входом элемента задержки, первый вход подключен к выходу первого логического элемента И и одному входу двухвходового элемента ИЛИ, второй вход которого соединен с выходом секционированной лннни задержки, а выход соединен с первым входом / 5-триггера, второй вход которого подключен к выходу дополнительного элемента задержки, вход которого подключен к выходу многовходового логического элемента И, причем выход RSтриггера соединен с первым входом первого дополнительного логического элемента И, второй вход которого соединен с выходом второго логического элемента И, а выход подключен ко второму входу дополнительного трехвходового логического элемента ИЛИ, третий вход которого соединен с выходом логического элемента НЕ - И, ири этом один вход второго дополнительного логического элемента И соединен со входной шиной, второй его вход подключен к выходу многоБходового логического элемента И, а выход дополнительного логического элемента И соединен с выходом селектора.

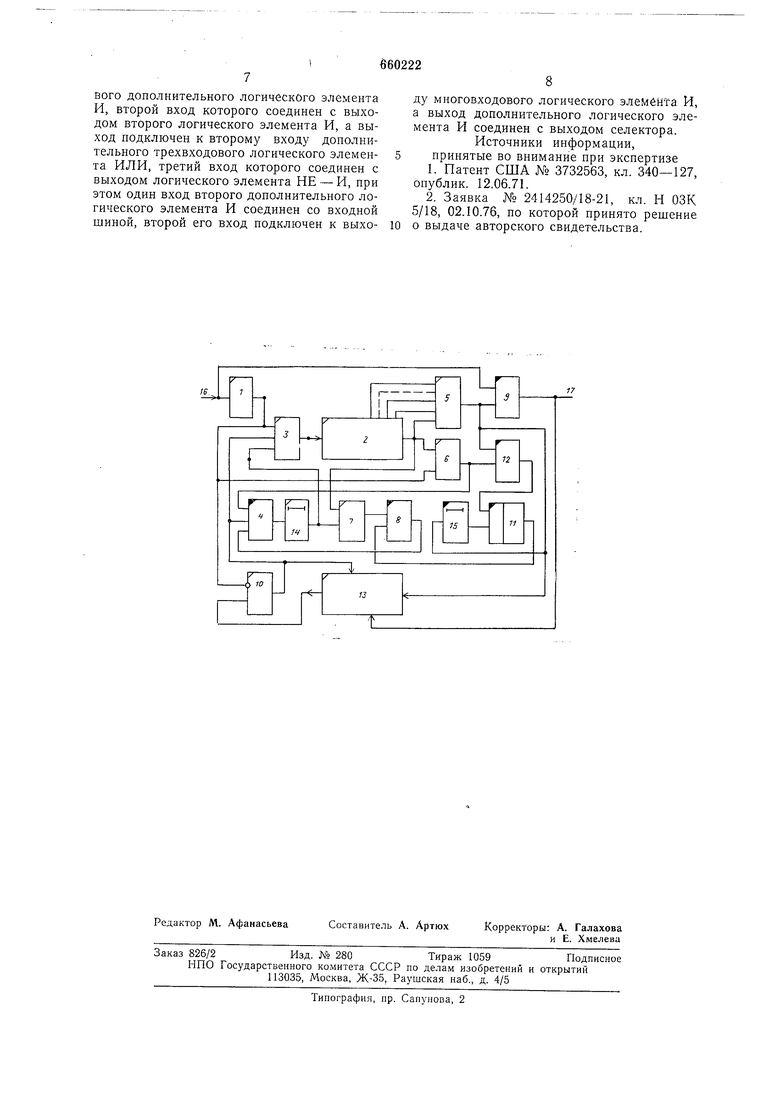

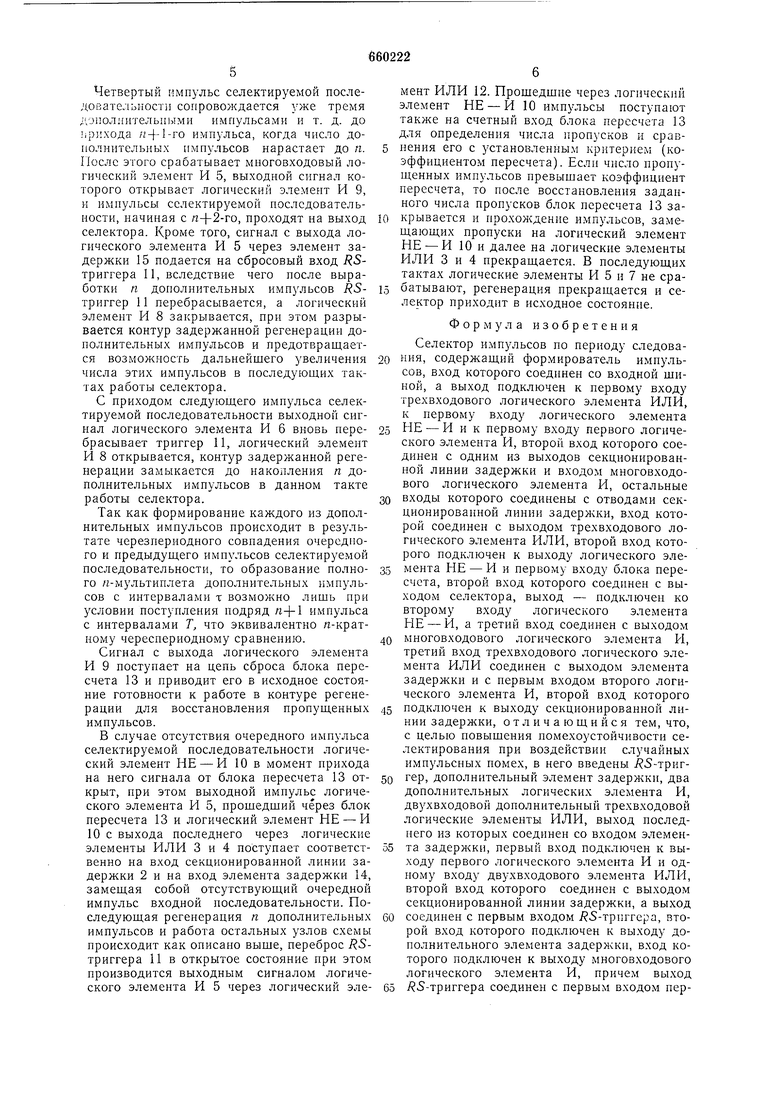

На чертеже дана структурная схема описываемого селектора.

Селектор содержит формирователь 1 импульсов, секционированную линию задержки 2, трехвходовые логические элементы ИЛИ 3, дополнительный трехвходовый логический элемент ИЛИ 4, многовходовый логический элемент И 5, двухвходовые логические элементы И 6 н 7, дополнительные двухвходовые логические элементы И 8 и 9, логический элемент НЕ - И 10, / 5-триггер

11,двухвходовый логический элемент ИЛИ

12,блок пересчета 13, элемент задержки 14 на т и дополнительный элемент задержки 15 на NT. Входной сигнал подан на входную шину 6, выходной сигнал снимается с выхода 17.

Принцип работы селектора заключается в следуюш,ем.

Ири поступлении сигналов на входную шину 16 селектора формирователь 1 вырабатывает нормализованные по длительности импульсы, которые через логический элемент ИЛИ 3 подаются на вход секционированной линии задержки 2, с ее выхода каждый импульс, задержанный на интервал Т, подается на вход логического элемента И 6. Если данный импульс принадлежит селектируемой последовательности, то в этот момент на другой вход логического элемента И 6 с выхода формирователя 1 поступает следуюший (второй) импульс последовательности и на выходе логического элемента И 6 появляется импульс совпадения, поступающий через логический элемент ИЛИ 12 на прямой вход / 5-триггера И и через логический элемент ИЛИ 4 - на элемент задержки 14. Выходной сигнал 5-триггера. И переводит логический элемент И 8 в открытое состояние. С выхода элемента задержки 14 импульс, задержанный относительно второго импульса последовательности на время т, через логический элемент ИЛИ 3 поступает на вход секционированной линии задержки 2 и проходит вслед за вторым импульсом селектируемой последовательности, образуя с ним дуплет с интервалом t. Импульс с выхода элемента задержки 14 поступает также на логический элемент И 7, но не проходит через него, так как на другой его вход сигнал в этот момент не поступает.

Третий импульс последовательности аналогичным образом проходит через логический элемент И 6, логический элемент ИЛИ 4 и элемент задержки 14 и поступает на вход секционированной линии задержки 2 через интервал т после импульса, поступившего на этот вход непосредственно с формирователя 1. С выхода элемента задержки 14 задержанный на время г третий импульс поступает на логический элемент И 7, на другой вход которого в этот момент с выхода секционированной линии задержки 2 приходит сформированный в предыдущем такте дополнительный импульс, отстающий от второго импульса последовательности на интервал т {второй имиульс дуплета). С выхода логического элемента И 7 имиульс совпадения проходит через открытый единичным выходом 5-триггера И логический элемент И 8 и через логический элемент ИЛИ 4 вновь поступает на элемент задерл :ки 14, с выхода которого задержанный еще на интервал т имиульс через логический элемент ИЛИ 3 проходит на вход секционированной линии задержки 2, в результате чего вслед за третьим импульсом последовательности распространяются уже два дополнительных импульса, образующие вместе с новым импульсом триплет с интервалами т. Второй раз нмпульс с выхода элемента задержки 14 через логический элемент И 7 не проходит.

Четвертый импульс селектируемой последовательности сопровождается уже тремя и,ополннтельиыми импульсами и т. д. до прихода /i-f-1-ro импульса, когда число дополнительных импульсов нарастает до п. После этого срабатывает многовходовый логический элемент И 5, выходной сигнал которого открывает логический элемент И 9, и импульсы селектируемой иоследовательности, начиная с л-f 2-го, проходят на выход селектора. Кроме того, сигнал с выхода логического элемента И 5 через элемент задержки 15 подается на сбросовый вход 5триггера 11, вследствие чего после выработки п дополнительных импульсов 5триггер 11 перебрасывается, а логический элемент И 8 закрывается, при этом разрывается контур задержанной регенерации дополнительных импульсов и предотвращается возможность дальнейшего увеличения числа этих импульсов в последующих тактах работы селектора.

С приходом следующего импульса селектируемой последовательности выходной сигнал логического элемента И 6 вновь перебрасывает триггер 11, логический элемент И 8 открывается, контур задержанной регенерации замыкается до накопления п дополнительных импульсов в данном такте работы селектора.

Так как формирование каждого из дополнительных импульсов происходит в результате черезпериодного совпадения очередного и предыдущего импульсов селектируемой последовательности, то образование полного «-мультиплета дополнительных импульсов с интервалами т возможно лишь при условии поступления подряд л+1 импульса с интервалами Т, что эквивалентно л-кратному череспериодному сравнению.

Сигнал с выхода логического элемента И 9 поступает на цепь сброса блока пересчета 13 и приводит его в исходное состояние готовности к работе в контуре регенерации для восстановления пропущенных импульсов.

В случае отсутствия очередного импульса селектируемой последовательности логический элемент НЕ - И 10 в момент нрихода на него сигнала от блока пересчета 13 открыт, при этом выходной импульс логического элемента И 5, прошедший через блок пересчета 13 и логический элемент НЕ - И 10 с выхода последнего через логические элементы ИЛИ 3 и 4 поступает соответственно на вход секционированной линии задержки 2 и на вход элемента задержки 14, замещая собой отсутствующий очередной импульс входной последовательности. Последующая регенерация п дополнительных импульсов и работа остальных узлов схемы происходит как описано выше, переброс RSтриггера 11 в открытое состояние при этом производится выходным сигналом логического элемента И 5 через логический элемент ИЛИ 12. Прошедшие через логический элемент НЕ - И 10 импульсы поступают также на счетный вход блока пересчета 13 ля определения числа пропусков и сравпения его с установленным критерием (коэффициентом пересчета). Если число пропущенных импульсов превышает коэффициент пересчета, то после восстановления заданного числа пропусков блок пересчета 13 закрывается и ирохождение и.мпульсов, замещающих пропуски на логический элемент НЕ - И 10 и далее на логические элементы ИЛИ 3 и 4 прекращается. В последующих тактах логические элементы И 5 и 7 не срабатывают, регенерация прекращается и селектор приходит в исходное состояние.

Формула изобретения

Селектор импульсов по периоду следования, содержащий формирователь импульсов, вход которого соединен со входной щиной, а выход подключен к первому входу трехвходового логического элемента ИЛИ, к первому входу логического элемента

НЕ - И и к первому входу первого логического элемента И, второй вход которого соединен с одним из выходов секционированной линии задержки и входом многовходового логического элемента И, остальные

входы которого соединены с отводами секционированной линии задержки, вход которой соединен с выходом трехвходового логического элемента ИЛИ, второй вход которого подключен к выходу логического элемента НЕ - И и первому входу блока пересчета, второй вход которого соединен с выходом селектора, выход - подключен ко второму входу логического элемента НЕ - И, а третий вход соединен с выходом

многовходового логического элемента И, третий в.ход трехвходового логического элемента ИЛИ соединен с выходом элемента задержки и с иервым входом второго логического элемента И, второй вход которого

подключен к выходу секционированной линии задержки, отличающийся тем, что, с целью повышения помехоустойчивости селектирования при воздействии случайных импульсных помех, в него введены .5-триггер, дополнительный элемент задержки, два дополнительных логических элемента И, двухвходовой дополнительный трехвходовой логические элементы ИЛИ, выход последнего из которых соединен со входом элемента задержки, первый вход подключен к выходу первого логического элемента И и одному входу двухвходового элемента ИЛИ, второй вход которого соединен с выходом секционированной линии задержки, а выход

соединен с первым входом У 5-трпггера, второй вход которого подключен к выходу дополнительного элемента задержки, вход которого подключен к выходу многовходового логического элемента И, причем выход 5-триггера соединен с первым входом пер7

вого дополнительного логического элемента И, второй вход которого соединен с выходом второго логического элемента И, а выход подключен к второму входу дополнительного трехвходового логического элемента ИЛИ, третий вход которого соединен с выходом логического элемента НЕ - И, при этом один вход второго дополнительного логического элемента И соединен со входной шиной, второй его вход подключен к выходу многовходового логического элемента И, а выход дополнительного логического элемента И соединен с выходом селектора.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3732563, кл. 340-127, опублик. 12.06.71.

2.Заявка № 2414250/18-21, кл. Н ОЗК 5/18, 02.10.76, по которой принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов | 1976 |

|

SU661757A1 |

| Селектор импульсов по периоду следования | 1976 |

|

SU660223A1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1977 |

|

SU696463A1 |

| Устройство для цифровой магнитной записи | 1977 |

|

SU699546A1 |

| Устройство для автоматического счета подвижных объектов | 1975 |

|

SU658023A1 |

| Цифровой измеритель длительности пачки импульсов | 1980 |

|

SU892412A1 |

| Рентгентелевизионный дефектоскоп | 1982 |

|

SU1081489A1 |

| Селектор импульсной последовательности | 1977 |

|

SU711673A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1977 |

|

SU684569A1 |

Авторы

Даты

1979-04-30—Публикация

1976-12-06—Подача