1

Изобретение относится к области информационно-измерительной техники и может быть использовано для преобразования аналоговых сигналов в цифровые коды.

Известен многоканальный интегрирующий аналого-цифровой преобразователь, содержащий ключи, преобразователь, блок управления и переключения каналов и счетчик.

Этот преобразователь имеет недостаточную точность преобразования 1.

Известен многоканальный интегрирующий аналого-цифровой преобразователь, содержащий 7 С-цепочки, подключенные к ключам, управляющие входы которых соединены с блоком адресного выбора каналов, блок управления, имеющий свой управляющий вход и соединенный со счетчиком, имеющим выходы для считывания результатов преобразования, и с блоком адресного выбора каналов, который имеет выход, номера канала ,2.

Известный преобразователь обладает низкой точностью, так как в нем применено только аналоговое интегрирование, которое не обеспечивает длительного хранения результатов преобразования, и имеет нелинейность из-за конечной постоянной времени интеграторов на С-ценочках.

Целью изобретения является новыщение

точности и быстродействия преобразования, а также уменьщение нелинейности за счет ее коррекции. Поставленная цель достигается тем, что

в многоканальный интегрирующий аналогоцифровой преобразователь, содерл ащий источник опорного напряжения, Т С-цепочки, подключенные к канальным ключам, управляющие входы которых соединены с

блоком адресного выбора каналов, подключенным к блоку управления, соединенному со счетчиком, введены элемент сравнения, дополнительный ключ, реверсивный счетчик импульсов и запоминающее устройство,

элемент сравнения и дополнительный ключ подключены к объединенным выходам канальных ключей, к другому входу элемента сравнения подключен иеточник опорного напряжения, а выход соединен с реверсивным счетчиком импульсов, блоком управления и первым управляющим входом дополнительного ключа, второй управляющий вход которого соединен с блоком управления, блок управления подключен к входам

приема и выходам выдачи кодов реверсивного счетчика импульсов, соединенного с входами приема и выходами выдачи кодов с запоминающего устройства, которое подключено к блоку адресного выбора каналов.

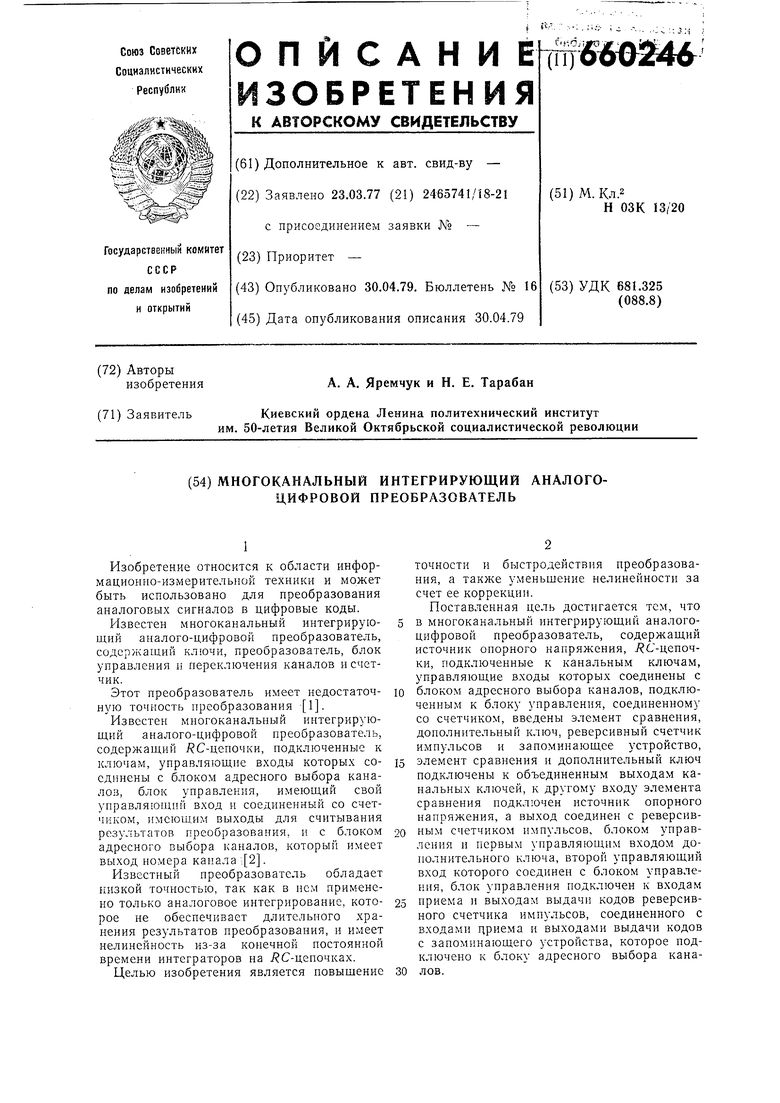

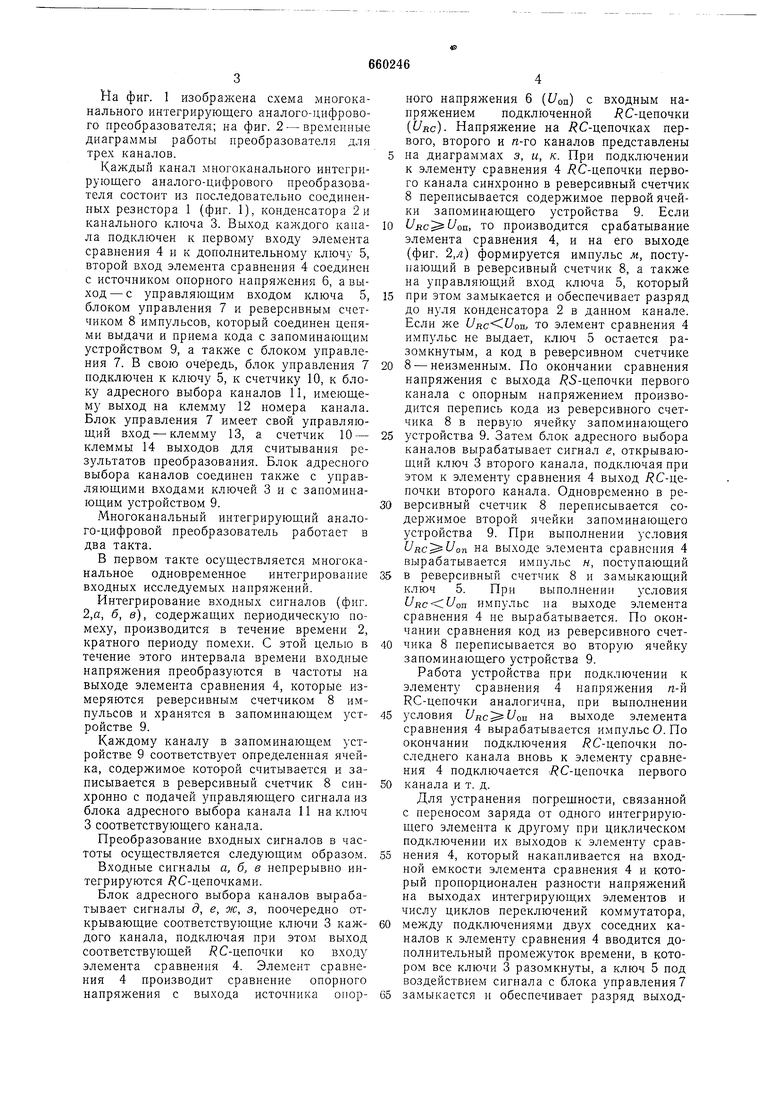

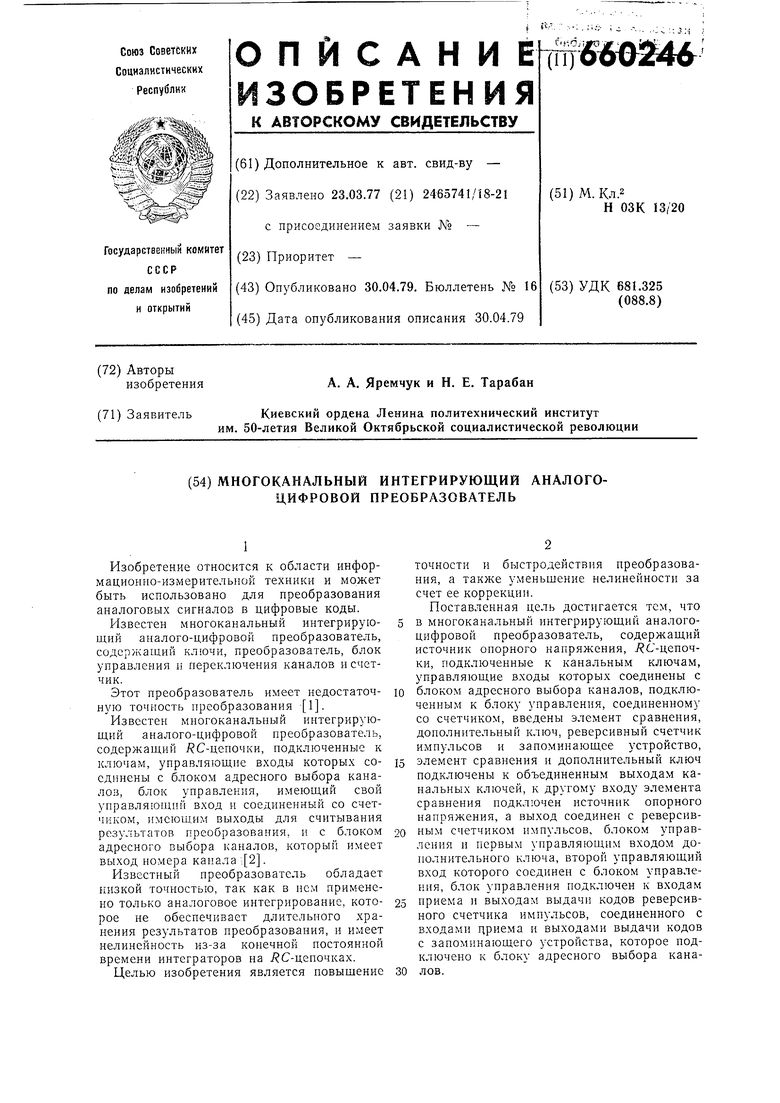

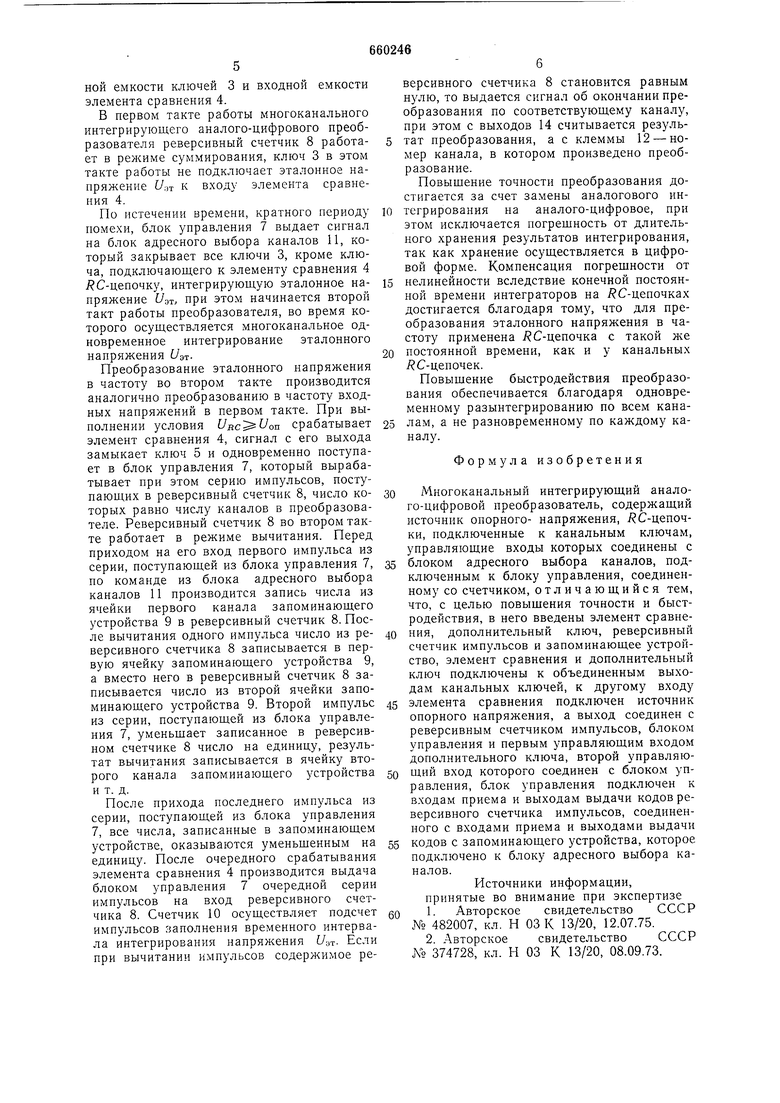

На фиг. 1 изображена схема многоканального интегрирующего аналого-цифрового иреобразователя; на фиг. 2 - временные диаграммы работы преобразователя для трех каналов.

Каждый канал многоканального интегрирующего аналого-цифрового преобразователя состоит из последовательно соединенных резистора 1 (фиг. 1), конденсатора 2 и канального ключа 3. Выход каждого канала нодключен к первому входу элемента сравнения 4 и к дополнительному ключу 5, второй вход элемента сравнения 4 соединен с источником опорного напряжения 6, а выход- с управляющим входом ключа 5, блоком управления 7 и реверсивным счетчиком 8 импульсов, который соединен цепями выдачи и ириема кода с запоминающим устройством 9, а также с блоком управления 7. В свою очередь, блок управления 7 подключен к ключу 5, к счетчику 10, к блоку адресного выбора каналов 11, имеющему выход на клемму 12 номера канала. Блок управления 7 имеет свой управляющий вход - клемму 13, а счетчик 10 - клеммы 14 выходов для считывания результатов иреобразования. Блок адресного выбора каналов соединен также с управляющими входами ключей 3 и с запоминающим устройством 9.

Многоканальный интегрирующий аналого-цифровой преобразователь работает в два такта.

В первом такте осуществляется многоканальное одновременное интегрирование входных исследуемых напряжений.

Интегрирование входных сигналов (фиг. 2,а, б, в), содержащих периодическую иомеху, производится в течение времени 2, кратного периоду помехи. С этой целью в течение этого интервала времени входные напряжения преобразуются в частоты на выходе элемента сравнения 4, которые измеряются реверсивным счетчиком 8 имиульсов и хранятся в запоминающем устройстве 9.

Каждому каналу в запоминающем устройстве 9 соответствует определенная ячейка, содержимое которой считывается и записывается в реверсивный счетчик 8 синхронно с подачей управляющего сигнала из блока адресного выбора канала 11 на ключ 3 соответствующего канала.

Преобразование входных сигналов в частоты осуществляется следующим образо.м.

Входные сигналы а, б, в непрерывно интегрируются / С-ценочками.

Блок адресного выбора каналов вырабатывает сигналы д, е, ж, з, поочередно открывающие соответствующие ключи 3 каждого канала, подключая при этом выход соответствующей С-цеиочки ко входу элемента сравнения 4. Элемент сравнения 4 производит сравнение опорного напряжения с выхода источника опорного напряжения 6 (i/on) с входным напряжением подключенной ./ С-цепочки (URC). Напряжение на .С-цепочках первого, второго и п-то каналов представлены на диаграммах з, и, к. При подключении к элементу сравнения 4 Т С-цепочки первого канала синхронно в реверсивный счетчик 8 переписывается содержимое первой ячейки запоминающего устройства 9. Если

, то производится срабатывание элемента сравнения 4, и на его выходе (фиг. 2,л) формируется имиульс м, поступающий в реверсивный счетчик 8, а также на управляющий вход ключа 5, который

при этом замыкается и обеспечивает разряд до нуля конденсатора 2 в данном канале. Если же , то элемент сравнения 4 импульс не выдает, ключ 5 остается разомкнутым, а код в реверсивном счетчике

8 - неизменным. По окончании сравнения напряжения с выхода 5-цепочки первого канала с опорным напряжением производится перепись кода из реверсивного счетчика 8 в первую ячейку запоминающего

устройства 9. Затем блок адресного выбора каналов вырабатывает сигнал е, открывающий ключ 3 второго канала, подключая при этом к элементу сравнения 4 выход У С-цепочки второго канала. Одновременно в реверсивный счетчик 8 переписывается содержимое второй ячейки запоминающего устройства 9. При выполнении условия на вы.ходе элемента сравнения 4 вырабатывается имиульс н, поступающий

в реверсивный счетчик 8 и замыкающий ключ 5. При выполнении условия импульс на выходе элемента сравнения 4 не вырабатывается. По окончании сравнения код из реверсивного счетчика 8 переписывается во вторую ячейку запоминающего устройства 9.

Работа устройства при подключении к элементу сравнения 4 напряжения л-й RC-цеиочки аналогична, ири выполнении

условия на выходе элемента сравнения 4 вырабатывается импульс О. По окончании иодключения С-цепочки последнего канала вновь к элементу сравнения 4 подключается :/ С-цепочка первого

канала и т. д.

Для устранения погрещности, связанной с переносом заряда от одного интегрирующего элемента к другому при циклическом подключении их выходов к элементу сравнения 4, который накапливается на входной емкости элемента сравнения 4 и который пропорционален разности напряжений на выходах интегрирующих элементов и числу циклов переключений коммутатора,

между подключениями двух соседних каналов к элементу сравнения 4 вводится дополнительный промежуток времени, в котором все ключи 3 разомкнуты, а ключ 5 под воздействием сигнала с блока управления 7

замыкается и обеспечивает разряд выходной емкости ключей 3 и входной емкости элемента сравнения 4.

В первом такте работы многоканального интегрирующего аналого-цифрового преобразователя реверсивный счетчик 8 работает в режиме суммирования, ключ 3 в этом такте работы не подключает эталонное напряжение f/oT к входу элемента сравнения 4.

По истечении времени, кратного периоду помехи, блок управления 7 выдает сигнал на блок адресного выбора каналов И, который закрывает все ключи 3, кроме ключа, подключающего к элементу сравнения 4 У С-цепочку, интегрирующую эталонное напряжение Usf, при этом начинается второй такт работы преобразователя, во время которого осуществляется многоканальное одновременное интегрирование эталонного напряжения UatПреобразование эталонного напряжения в частоту во втором такте производится аналогично преобразованию в частоту входных напряжений в первом такте. При выполнении условия срабатывает элемент сравнения 4, сигнал с его выхода замыкает ключ 5 и одновременно поступает в блок управления 7, который вырабатывает при этом серию импульсов, поступающих в реверсивный счетчик 8, число которых равно числу каналов в преобразователе. Реверсивный счетчик 8 во втором такте работает в режиме вычитания. Перед приходом на его вход первого импульса из серии, поступающей из блока управления 7, по команде из блока адресного выбора каналов 11 производится запись числа из ячейки первого канала запоминающего устройства 9 в реверсивный счетчик 8. После вычитания одного импульса число из реверсивного счетчика 8 записывается в первую ячейку запоминающего устройства 9, а вместо него в реверсивный счетчик 8 записывается число из второй ячейки запоминающего устройства 9. Второй импульс из серии, поступающей из блока управления 7, уменьшает записанное в реверсивном счетчике 8 число на единицу, результат вычитания записывается в ячейку второго канала запоминающего устройства и т. д.

После прихода последнего импульса из серии, поступающей из блока управления 7, все числа, записанные в запоминающем устройстве, оказываются уменьщенным на единицу. После очередного срабатывания элемента сравнения 4 производится выдача блоком управления 7 очередной серии импульсов на вход реверсивного счетчика 8. Счетчик 10 осуществляет подсчет импульсов заполнения временного интервала интегрирования напряжения t/зт. Если при вычитании импульсов содержимое реверсивного счетчика 8 становится равным нулю, то выдается сигнал об окончании преобразования по соответствующему каналу, при этом с выходов 14 считывается результат преобразования, а с клеммы 12 - номер канала, в котором произведено преобразование.

Повышение точности преобразования достигается за счет замены аналогового интегрирования на аналого-цифровое, при этом исключается ногрещность от длительного хранения результатов интегрирования, так как хранение осуществляется в цифровой форме. Компенсация погрещности от

нелинейности вследствие конечной постоянной времени интеграторов на / С-цепочках достигается благодаря тому, что для преобразования эталонного напряжения в частоту применена С-цепочка с такой же

постоянной времени, как и у канальных С-цепочек.

Повыщение быстродействия преобразования обеспечивается благодаря одновременному разынтегрированию по всем каналам, а не разновременному по каждому каналу.

Формула изобретения

Многоканальный интегрирующий аналого-цифровой преобразователь, содержащий источник опорного- напряжения, С-цепочки, подключенные к канальным ключам, управляющие входы которых соединены с

блоком адресного выбора каналов, подключенным к блоку управления, соединенному со счетчиком, отличающийся тем, что, с целью повышения точности и быстродействия, в него введены элемент сравнеНИН, дополнительный ключ, реверсивный счетчик импульсов и запоминающее устройство, элемент сравнения и дополнительный ключ подключены к объединенным выходам канальных ключей, к другому входу

элемента сравнения подключен источник опорного напряжения, а выход соединен с реверсивным счетчиком импульсов, блоком управления и первым управляющим входом дополнительного ключа, второй управляюЩий вход которого соединен с блоком управления, блок управления подключен к входам приема и выходам выдачи кодов реверсивного счетчика импульсов, соединенного с входами приема и выходами выдачи

кодов с запоминающего устройства, которое подключено к блоку адресного выбора каналов.

Источники информации, принятые во внимание при экспертизе

1- Авторское свидетельство СССР № 482007, кл. Н 03 К 13/20, 12.07.75.

2. Авторское свидетельство СССР № 374728, кл. Н 03 К 13/20, 08.09.73.

фиг.1

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный интегрирующий аналого- цифровой преобразователь | 1977 |

|

SU702515A1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2282937C1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1986 |

|

SU1320900A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU432512A1 |

| Многоканальное устройство для измерения температуры | 1989 |

|

SU1672239A1 |

| Многоканальный фазовый демодулятор | 1988 |

|

SU1555900A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ ПЕРЕМЕННОГО ТОКА В КОД | 2001 |

|

RU2195767C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1316089A1 |

П П П П П { П П П t

.JL.

LZlZlZt ZE3ZG3xn:/ т

м о к м я о м у- о м и я ff м

.i...l....nj JL ilJ10

Авторы

Даты

1979-04-30—Публикация

1977-03-23—Подача