11

Изобретение относится к автоматик и информационно-кзмерительной технике и может быть использовано в системах сбора аналоговой информации, предназначенных для автоматизации технологических процессов и научных исследований.

Цель изобретения - повышение точности преобразования и расширение области применения за счет возможности преобразования разнополярных быстро- изменяющихся сигналов.

На фиг.1 гтриведена функциональная схема аналого-цифрового преобразователя; на фиг.2 - функциональная схем блока формирования эталонного сигнала; на фиг.З - функциональная схем блока адресного выбора канала преобразования ; на фиг,4 - функциональная схема блока управления.

Аналого-цифровой преобразователь (фиг.1) содержит п блоков 1.1-l.n выборки хранения, п блоков 2.1-2.П формирования, эталонного сигнала, п ключей 3.1-З.п и дополнительных ключей 4.1-Д.п, интегратор 5, компаратор 6, источник 7 опорного напряжения, блок 8 адресного выбора канала преобразования, блок 9 управления

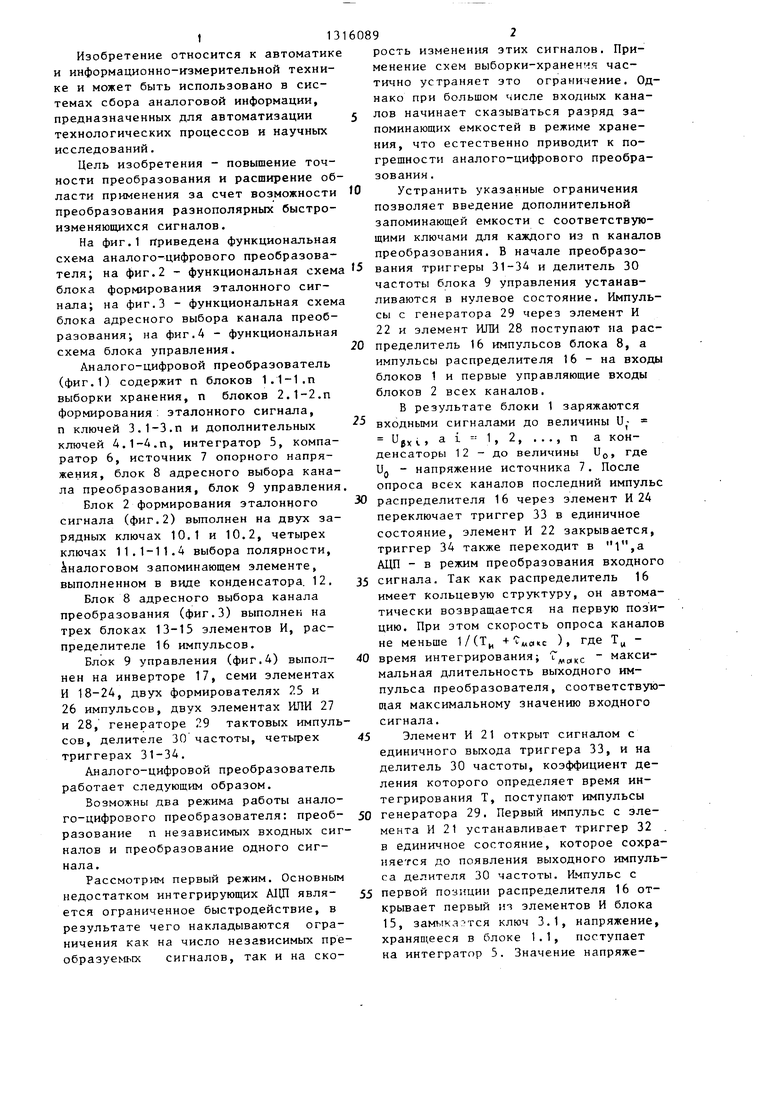

Блок 2 формирования эталонного сигнала (фиг.2) вьтолнен на двух зарядных ключах 10,1 и 10.2, четырех ключах 11.1-11.4 выбора полярности, Аналоговом запоминающем элементе, выполненном в виде конденсатора. 12,

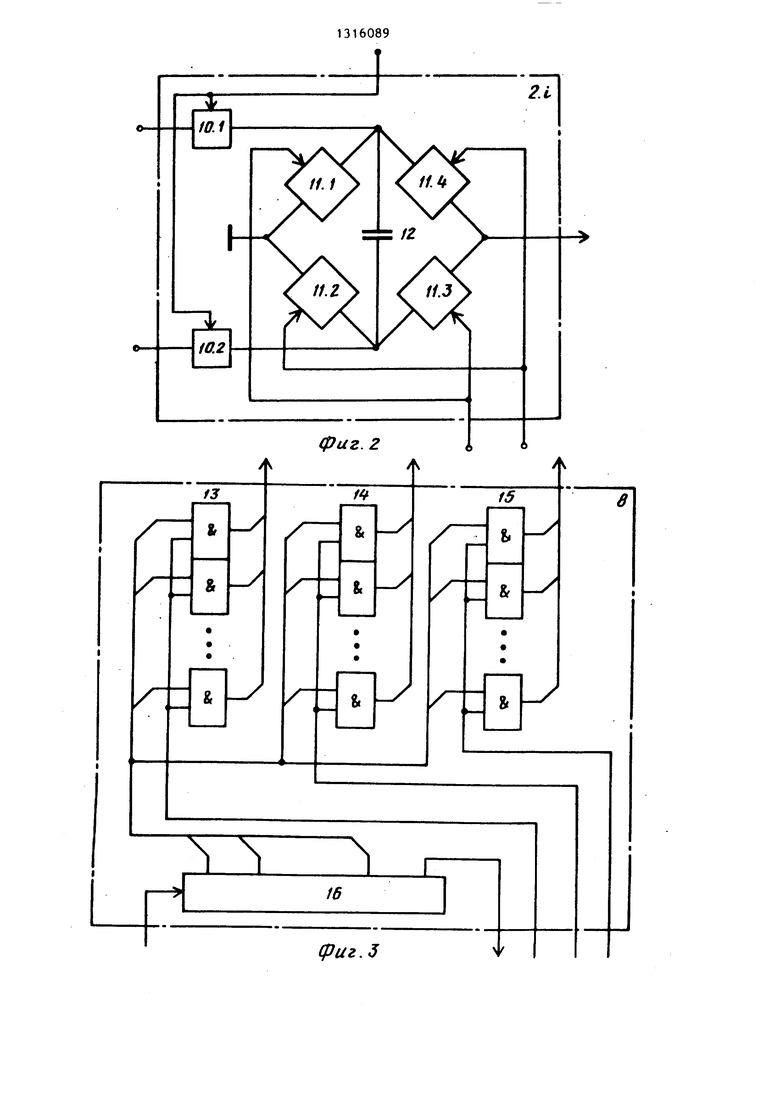

Блок 8 адресного выбора канала преобразования (фиг.З) выполнен на трех блоках 13-15 элементов И, распределителе 16 импульсов.

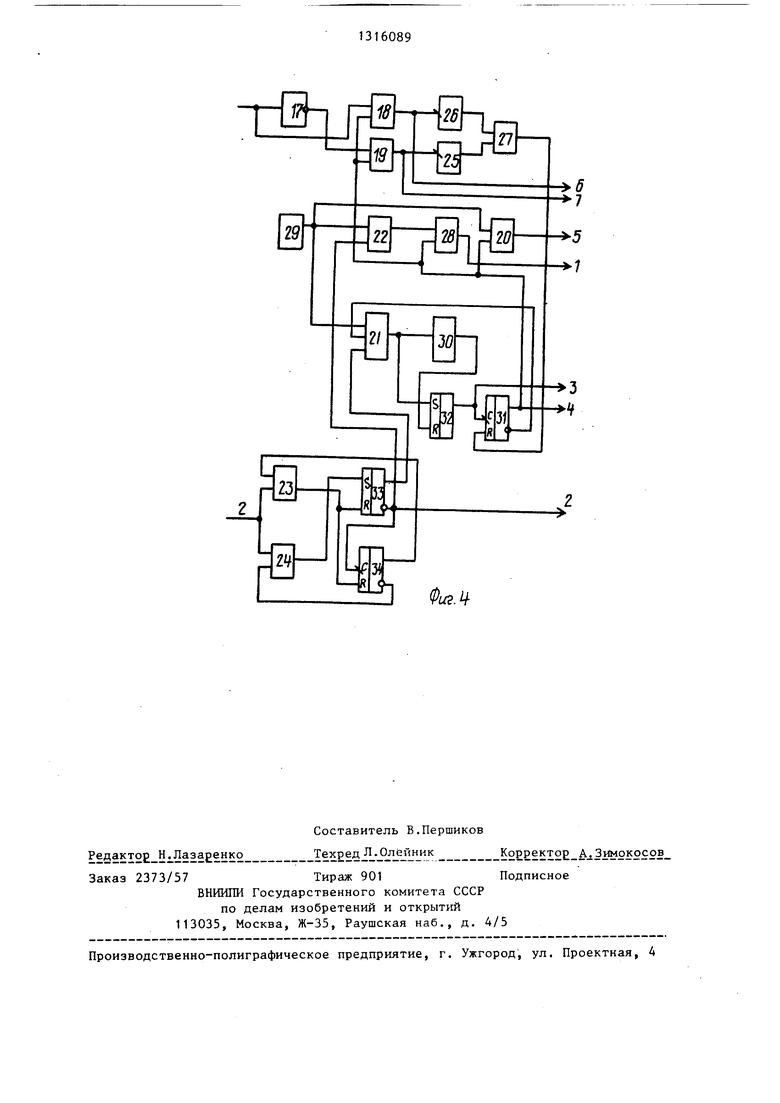

Блок 9 управления (фиг,4) выполнен на инверторе 17, семи элементах И 18-24, двух формирователях 25 и 26 импульсов, двух элементах ИЛИ 27 и 28, генераторе 29 тактовых импульсов, делителе 30 частоты, четьфех триггерах 31-34,

Аналого-цифровой преобразователь работает следующим образом.

Возможны два режима работы аналого-цифрового преобразователя: преобразование п независимых входных сигналов и преобразование одного сигнала.

Рассмотрим первый режим. Основным недостатком интегрирующих А1Щ является ограниченное быстродействие, в результате чего накладываются ограничения как на число независимьпс преобразуемых сигналов, так и на ско60892

рость изменения этих сигналов. Применение схем выборки-хранения частично устраняет это ограничение. Однако при большом числе входных кана5 лов начинает сказываться разряд запоминающих емкостей в режиме хранения, что естественно приводит к погрешности аналого-цифрового преобразования ,

o Устранить указанные ограничения позволяет введение дополнительной запоминающей емкости с соответствующими ключами для каждого из п каналов преобразования. В начале преобразо5 вания триггеры 31-34 и делитель 30 частоты блока 9 управления устанавливаются в нулевое состояние. Импульсы с генератора 29 через элемент И 22 и элемент ИЛИ 28 поступают на рас0 пределитель 16 импульсов блока 8, а импульсы распределителя 16 - на входы блоков 1 и первые управляющие входы блоков 2 всех каналов,

В результате блоки 1 заряжаются

5 входньп и сигналами до величины Ugy, ,2, ...,п а конденсаторы 12 - до величины U, где Ug - напряжение источника 7. После опроса всех каналов последний импульс

30 распределителя 16 через элемент И 24 переключает триггер 33 в единичное состояние, элемент И 22 закрывается, триггер 34 также переходит в 1,а АЦП - в режим преобразования входного

35 сигнала. Так как распределитель 16 имеет Кольцевую структуру, он автоматически возвращается на первую позицию. При этом скорость опроса каналов не меньше 1/(Т ), где T, 40 время интегрирования; ацс максимальная длительность выходного импульса преобразователя, соответствующая максимальному значению входного сигнала.

45 Элемент И 21 открыт сигналом с единичного выхода триггера 33, и на делитель 30 частоты, коэффициент деления которого определяет время интегрирования Т, поступают импульсы

0 генератора 29, Первый импульс с элемента И 21 устанавливает триггер 32 . в единичное состояние, которое сохраняется до появления выходного импульса делителя 30 частоты. Импульс с

55 первой позиции распределителя 16 открывает первый из элементов И блока 15, замыклг тся ключ 3.1, напряжение, храняп;ееся в блоке 1.1, поступает на интегратор 3. Значение напряжетом возможных утечек,равно

-t/Tp.

1 Уче

- где Т

и.,, е

flJ ч

,2,

п

. pi - постоянная разрядка емкост в блоке 1.1 1-го канала. При отрицательном выходном сигнале интегратора 5 напряжение на выходе компаратора 6 имеет уровень логической 1, при положительном - уровень логического О. В первом случае сигнал с выхода компаратора 6 подается непосредственно на первый вход элемента И 18, во втором - через инвертор 17 на первый вход элемента И 19. После окончания Т выходным сигналом делителя 30 частоты триггер 32 устанавливается в О, а триггер 31 - в 1 при этом соответствующий высокий потенциал подается на вторые входы элементов 18 и 19, а также на вход элемента И 20, одновременно с этим закрывается элемент И 21, один из входов которого соединен с нулевым вы- ходом триггера 31. В результате высокий потенциал появляется в зависимости от полярности входного сигнала на выходе либо элемента 18, либо элемента 19, при этом открываются соответ- ствующие пары ключей 11 выбора полярности напряжения с выхода соответствующего блока 1 .

Переключение триггера 31 в 1 открывает вентиль 20, через который проходят импульсы генервтора 29 тактовых импульсов, одновременно включается соответствующий вентиль из группы 14, который замыкает определенный ключ 4. В результате к входу интегратора 5 подключается конденсатор 12, и на входе интегратора 5 действует напряжение

и; Uoe

-t/T

Ро

1 1,2п.

Согласно известным соотношениям, описьшающим работу двухтактного интегрирующего времяимпульсного преобразователя, длительность выходного импульса определяется -ТИ/ТР,

К У

Ur

Т

и

-ГГ,+7)/Тро5

К const

условии,

oi ,

что

т,

р;

+ г «

Ди т. +Г ,

к Гт- - )

и,

(1)

ро

Uo

Т„ е

.

PCI

И

учитывая, что Т Т

poi

- К-Т

- и-и;

5 „

Таким образом, в идеальном .случае утечка конденсаторов в блоках 1 не сказывается на точности измерения. В реальных условиях Т р; Тр,- полной компенсации не достигается, однако ошибка из-за утечки конденсаторов в блоках 1 может быть уменьшена. Из соотношения (1) показатель экспоненты может быть представлен как

- Т т и р

,-)/т

(TI,T poi

р;

РО

так как t « Т

5 тогда (Т ро; - Тр,- )/Тр, Т

чину Тр;Тр,.

/(т

POi

poi ВелиPOi

- Т,

ЭКВ

0

5 „

5

0

5

0

5

можно рассматривать как эквивалентную постоянную времени конденсаторов в блоках. Нетрудно видеть, что .

Поскольку погрешность запоминания определяется постоянной разряда запоминающей емкости, увеличение этой постоянной снижает соответствующий уровень погрешности. Когда напряжение на выходе компаратора 6 становится равным нулю, закрывается один из элементов 18 или 19, происходит срабатывание по заднему фронту одного из формирователей 26 или 25. Выходной импульс формирователя 26 (25) через элемент ИЛИ 27 поступает на R-вход триггера 31, который переключается в состояние О, элемент И 20 закрывается. Число импульсов, прошедшее через этот вентиль, пропорционально измеряемому сигналу 1-го канала. Перепад напряжений, возникший при переключении триггера 31, через элемент ИЛИ 28 переключает распределитель 16 на одну позицию и начинается преобразование сигнала следующего канала. После опроса всех 12 каналов импульс с последней ячейки распределителя через элемент И 23 переключает триггеры 33 и 34 в нулевое состояние, одновременно закрывается элемент И 21. Таким образом, вся схема возвращается в исходное cocTOHHiie.

В режиме преобразования одного сигнала все ходы аналоговых сигналов объединяются и подключаются к источнику преобразуемого сигнала. Преобразователь работает аналогично предыдущему режиму.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий п ключей, где п число входных преобразуемых сигналов, выходы которых объединены, а управляющие входы подключены к соответствующим первым выходам блока адресного блока выбора канала преобразования, первый вход которого подключен к первому выходу блока управления, первый вход которого подключен к выходу компаратора, два дополнительных ключа, выходы которых объединены, а управляющие входы подключены к соответствующим вторым выходам блока адресного выбора канала преобразования, отличающийся тем, что, с целью повышения точности преобразования и расширения области применения за счет возможности преобразования разнополярных быстроизменяющихся сигналов, введены источник опорного напряжения, п 2 дополнительных ключей, интегратор, п блоков формирования эталонных сигналов, п блоков выборки- хранения, аналоговые входы которых являются входными щинами соответствующих каналов преобразования, выходы подключены к аналоговым входам соответствующих п ключей, управляющие входы объединены с первыми управляющими входами соответствующих п блоков формирования эталонных сигналов и подключены к соответствующим третьим выходам блока адресного выбора канала преобразования, соответствующие вторые выходы которого подключены к соответствующим управляющим входам п-2 дополнительных ключей, четвертый выход подключен к второму входу блока управления, выходы с второго по четвертый которого подключены соответственно к входам с второго по четвер тый блока адресного выбора канала преобразования, пятый выход является выходной шиной, а щестой и седьмой выходы подключены соответственно к вторым и третьим управляющим входам - п блоков формирования эталонных сигналов, первые аналоговые входы которых объединены н подключены к первому выходу источника опорного напряжения, вторые аналоговые входы объединены и подключены к второму выходу источника опорного напряжения, выходы подключены к аналоговым входам соответствующих п дополнительных ключей, выходы п-2 из которых объединены с выходом первого дополнительного ключа и подключены к первому входу интегратора, к второму входу которого подключен выход первого из

JO

п ключей, выход интегратора подключен к первому входу компаратора, второй вход которого подключен к шине нулевого потенциала.

2.Преобразователь по п.1, о т - личающийся тем, что блок формирования эталонного сигнала выполнен на первом и втором зарядных ключах, первом, втором, третьем и четвертом ключах выбора полярности, аналоговом запоминающем элементе, выполненном в виде конденсатора, первый вывод которого объединен с выходом первого и аналоговым входом четf5 вертого ключей выбора полярности и подключен к выходу первого зарядного ключа, второй вывод конденсатора объединен с выходом второго и аналоговым входом третьего ключей выбора поляр20 ности и подключен к выходу второго зарядного ключа, управляющий вход которого объединен с управляющим входом первого зарядного ключа и является первым управляющим входом блока

25 формирования эталонного сигнала, аналоговые входы первого и второго зарядных ключей являются соответственно первым и вторым аналоговыми входами блока формирования эталонного сигна30 ла, при этом аналоговые входы первого и второго ключей выбора полярности объединены и подключены к шине нулевого потенциала, выходы третьего и четвертого ключей выбора полярности объединены и являются выходом блока формирования эталонного сигнала, управляющие входы первого и третьего ключей выбора полярности объединены и являются вторым управляющим входом блока формирования эталонного сигнала, а управляющие входы второго и четвертого ключей выбора полярности объединены и являются третьим управляющим входом блока формирования эта45 лонного сигнала.

3.Преобразователь по п.1, о т - личающийся тем, что блок адресного выбора канала преобразования выполнен на первом, втором и тре5Q тьем блоках элементов И и распределителе импульсов, вход которого яв- - ляется первым входом блока адресного выбора канала преобразования, п выходов подключены к соответствующим

55 входам первых групп входов первого, второго и третьего блоков элементов И,выходы которых являются соответствующими первыми, вторыми и третьими выходами блока адресного выбора кана3540

JO

15

ла преобразования, входы вторых групп входов объединены соответственно в пе.рвом, втором и третьем блоках элементов И и являются соответственно вторым, четвертым и третьим входами блока адресного вьШора канала преобразования, при этом п+1 выход распределителя импульсов является четвертым выходом блока адресного выбора канала преобразования.

4. Преобразователь по п.1, отличающийся тем, что блок управления выполнен на генераторе тактовых импульсов, семи элементах И, двух формирователях импульсов, двух элементах ИЛИ, делителе частоты, четырех триггерах, инверторе, вход которого объединен с первым входом первого элемента И и йвляется первым входом блока управления, а выход под-20 ключей к первому входу второго элемента И, выход которого является седьмым выходом блока управления и подключен к входу первого формирователя импульсов, выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к входу установки в нулевое состояние первого триггера, второй вход подключен к выходу второго формирователя 30 импульсов, вход которого подключен к выходу первого элемента И и является шестым выходом блока управления, второй вход первого элемента И объединен

та И, первым входом второго элемента ИЛИ, первым входом третьего элемента И, подключен к прямому выходу первого триггера и является четвертым выходом блока управления, инверсный выход 40

25

первого триггера подключен к первому входу четвертого элемента И, тактовый вход является третьим выходом блока управления и подключен к прямому выходу второго триггера, вход установки в нулевое состояние которого подключен к выходу делителя частоты, а вход установки в единичное состояние объединен с входом делителя частоты и подключен к выходу четвертого элемента И, второй вход которого объединен с вторым входом третьего элемента И, выход которого является пятым выходом блока управления, с пер- тым входом пятого элемента И и подключен к выходу генератора тактовых импульсов, третий вход четвертого элемента И подключен к прямому выходу третьего триггера, вход установки в нулевое состояние которого объединен с входом установки в нулевое состояние четвертого триггера и подключен к выходу шестого элемента И, первый вход которого объединен с первым входом седьмого элемента И и является вторым входом блока управления, второй вход подключен к прямому выходу четвертого триггера, инверсный выход которого подключен к второму входу седьмого элемента И, выход которого подключен к входу установки в единичное состояние третьего триггера, инверсный выход которого является вторым выходом блока управления и под- с вторым входом второго элемен- 35 ключен к тактовому входу четвертого

триггера и второму входу пятого элемента И, выход которого подключен к второму входу второго элемента ИЛИ, выход которого является первым выходом блока управления.

5

0 0

5

первого триггера подключен к первому входу четвертого элемента И, тактовый вход является третьим выходом блока управления и подключен к прямому выходу второго триггера, вход установки в нулевое состояние которого подключен к выходу делителя частоты, а вход установки в единичное состояние объединен с входом делителя частоты и подключен к выходу четвертого элемента И, второй вход которого объединен с вторым входом третьего элемента И, выход которого является пятым выходом блока управления, с пер- тым входом пятого элемента И и подключен к выходу генератора тактовых импульсов, третий вход четвертого элемента И подключен к прямому выходу третьего триггера, вход установки в нулевое состояние которого объединен с входом установки в нулевое состояние четвертого триггера и подключен к выходу шестого элемента И, первый вход которого объединен с первым входом седьмого элемента И и является вторым входом блока управления, второй вход подключен к прямому выходу четвертого триггера, инверсный выход которого подключен к второму входу седьмого элемента И, выход которого подключен к входу установки в единичное состояние третьего триггера, инверсный выход которого является вто(риг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для контроля работы транспортных средств | 1986 |

|

SU1446638A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1800616A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

/j

&

&

W

(риг. 5

/«

fS

в

&

Ь

&

&

&

&

| Гальперин П.А | |||

| и др | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Многоканальный интегрирующий аналого- цифровой преобразователь | 1977 |

|

SU702515A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-07—Публикация

1985-05-05—Подача