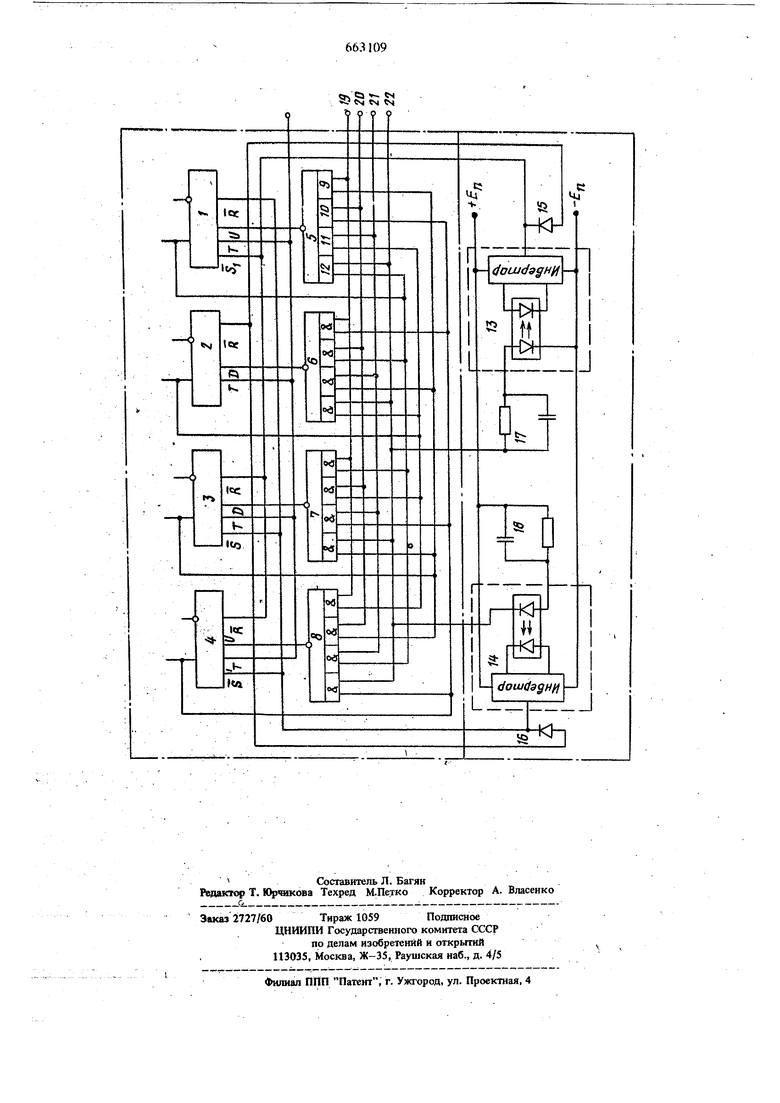

(54) РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ УРОВНЕЙ цепь - к управляющей шине числа смежных разрядов, а выход соединен с первой и через разде- . лйтельньш вход с второй выходными шинами бпо ка автоматической установки триггеров в определенное состояние, один вход второго onipoirtioro переключателя подключен к управляющей ишне числа смежных разрядов, другой вход чррез вторую ПС-цепь - к плю1совои шине источника питания, а. выход - к третьей и через второй разделительный диод к четвертой выходным шинам блока автоматической установки триггеров в определенное состояние. На чертеже представлена принципиальная электрическая схема предложенного распределителя уровней. Распределитель содержит четыре D-триггера 14, четыре логических элемента 2-2-2-2И-4ИЛИ-НЕ 5-8, в состав которых входят по четыре двухвходовых логических элемента И 9-12, и блок автоматической установки триггеров в определенное состояние, выполненный на двух оптронных переключателях 13, 14 с инверторами, разделительных диодах 15, 16 и двух дифференцирующих RC-цепях 17, 18. Выход каждого элемента 2-2-2-2И-4ИЛИ-НЕ подключен к информационному входу соответствующего триггера. Тактирующие сигналы подаются к тактирующим входам всех четырех триггеров Одноименные элементы И 9-12 всех разрядов по одному входу соединены соответственно между собой, образуя четыре управляюище шины 19-22. Единичный выход Tpitfгера каждого разряда подключен к вторым входам элемента И 12 данного разряда, элемента И 11 следующего разряда, элемента И Ю предьщущего разряда и элемента И 9 следующегб за ним разряда. ,, , Между управляющей шиной 22 и минусовой шиной источника питания через RC-цепь 17 в прямом направлении включена первичная цепь оптрон ного переключ:ат ля 13, выход инвертора которого непосредственно подключш к единичному уста новочному входу первого триггера и к нулевым установочным входам третьего и четвертого триггеров, а через разделительный даод 15 - к нулевому установочному входу второго триггера. Между управляющей шиной 22 и плюсовой ши ной источника гшта1шя распределителя через дифференщрующую НС-цепь 18 в прямом направлеНИИ включена п1грвнчная цепь оптронного переклю чателя 14. Выход его инвертора непосредственно подключен к нулевому установочному входу первого триггера и к единичным установочным входам третьего и четвертого трнгге{Х)в, а через разделительный диод 16 - к нулевому установочному входу второго триггера. Задание режимов коммутации фаз осуществля ется с помощью подачи определенных двоичных кодов уровней напряжения на управляющие шины 19-22. Уровень потенциала на управляющей шине 22 днозначно отображает число одаовременно возуждаемых фаз при данном режиме коммутации. ак Г-му уровню, приложенному к шине 22, сответствуют симметричные режимы прямого и обатного порядков переключечия фаз с п-1, а уровню - симметричные режимы с п- 2. При несимметричных режимах через такт меняется значения п с одного на два и наоборот. В связи с этим можно допустить, что в какой-то такт управления двум одаозаходным несимметричным режимам соответствует число одновременно возбуждаемых фаз п-2, а двум трехзаходным несимметричным режимам - п-1.. Непосредственное соответствие числа однов ременно возбуждаемых смежных фаз п управляющему потенциалу Ra шине 22 можно использовать для автоматического установления триггеров в : требуемые исходные состояния в каждом из всех возможных режимов коммутации фаз. Вьшолнение этой задачи осуществляется с помощью оптронных переключателей с инверторами и RCцепей. Перед началом создания каждого из возможных режимов коммутации фаз на управляющих цптаах 19-22 устанавливаются необходимые положения управляюпщх органов (например, переключателей) и тем самым прикладьшаются требуемые уровни управляющих потенциалов. При этом, если задается один из симметричнь1х или трехзаходных несимметричных режимов коммутации фаз с прямым или обратным порядком переключения и в соответствии с этим орган управления шиной 22 устанавливается на 1-е, состояние, то при включении источника питания распределителя под напряжением оказываются RC-цепь 17 и входная цепь оптронного переключателя 13. Через конденсатор и входную цепь оптрона в течение короткого промежз гка времени, определяемого постоянной времени дифференцирующей цепочки, протекает ток заряда конденсатора и вторичная цепь оптрона оказывается открытой. Этот Импульсный сигнал оптрона формируется в инверторе и приобретает стандартный прямоугольный вид. Если до поступления сигнала на вход инвертора на его выходе имеется Г-й потенциал, то на время действия сигнала возникает потенциал, что устанавливает в Г-е исходное состояние первый триггер и в исходные состояния второй, тре.тий и четвертый триггеры. По окончании полного заряда конденсатора импульс прекращается и на выходе шгоертора оптронного переключателя 13 восстанавливается Г-й уровень, который не препятствует дальнейшим потактным переключениям триггеров. Разряд конденсатора через резистор происходит в случае перехода на другой режим, при котором к шине 22 прикладывается потенциал. Таким образом, оптронный переключатель 13 с инвертором срабатывает каждый раз при появлении на шюсе 22 Г-го потенциала и устанавливает одан из триггеров в единичное исходное состояние, а три остальных триггера в нулевое состо яние-. Вторая цепочка установки в исходные состояния триггеров -,НС-цепь 18 и оптронный переключатель 14 с инвертором - функционирует ана логично первой цепочке, но в отличие от нее срабатывает только в моменты появления на,шине 22 уровня управляющего потенциала, т.е. только при симметричных режимах с п-2 и однозаходных несимметричных режимах, когда два из триггеров требуется установить в Г-е исходные состояния, а два - в состояния. Таким образом обеспечивается автоматическая установка триггеров в требуемые исходные состо яния в каждом из всех возможных режимов ком мутации фаз шагового двигателя. После установления соответствующих йсходнь1х состояний триггеров при каждом режиме коммутации фаз в процессах потактных переключений триггеров в каждом разряде участвзтот те из элементов И 9-12, на входы которых по шинам 1922 приложены Г-е уровни потенциалов. В зависимости от состояний триггеров в каждом такте на выходах логических элементов И-ИЛИ-НЕ до прихода очередного тактирующего сигнала устанавливаются соответствующие О или потенциалы. В соответствии с этими потенциалами по приходе каждого тактирующего сигнала триггеры устанавливаются в определенные О и Г-е состояния и тем самым создаю т синхронные переключения, требуемые для обеспечения заданных режимов коммуташш фаз. Таким образом, предпожешое устройство при относительной простоте конструкции обладает щирокшли функциональными возможностями. Формула изобретения 1. Реверсивный распределитель уровней, содержащий кольцевой реверсивный счетчик параллельного действия, выполненный на логических элементах и D-триггерах, каждый из которых содержит тактовый, информационный и два установочных входа, и шины тактирующих и управляющих импульсов, отличающийся тем, что, с .елью упрощейия распределителя и повышения его надежности, в него введен блок автоматической установки триггеров в определенное состояние, причем логические элементы выполнены в виде трехступенчатых логических элементов 2-2-2-2И-4ИЛИ-НЕ, каждый из которых выходом подключен к информационному входу D-триггера данного разряда, одними входами - к .шинам управляющих импульсов, другими - к единичным выходам 0триггеров, тактовые входы которых соединены с шиной тактирующих импульсов, а установочные входы подключены к выходнь1М шинам блока автоматической установки триггеров в определенное состояние. 2. Распределитель по п. 1, отличающийся тем, что кольцевой реверсивный счетчик параллельного действия выполнен четырехразрядным, а блок автомат стеской установки триггеров в определенное состояние вьшолнен на двух RC-цепях и двух оптронных переключателях с инверторами, при этом один вход первого оптронного переключателя подключен к минусовой шине источника питания, другой вход через первую ПС-цепь - к управляющей шине числа смежных разрядов, а вьгход соединен с первой и через разделительный ДИОД с второй выходными Шинами блока автоматической установки триггеров в определенное состояние, один вход второго оптронного переключателя подключен к управляющей шине числа смежных разрядов, другой вход через вторую ПС-цепь - к плюсовой, шине источника питания, а выход - к третьей и через второй разделительный диод к четвертой выходным шинам блока автоматической установки триггеров в определенное состояние. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 286020, л. НОЗК 17/16, 1969. 2. Авторское свидетельство СССР N 377950, л. Н ОЗК 17/16, 1970.

ч С) V- Сч

1 См tsi ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многорежимного управления трехфаным шаговым двигателем | 1976 |

|

SU574842A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1374179A1 |

| Трехканальный двухрежимный распределитель импульсов для управления шаговым двигателем | 1980 |

|

SU907753A1 |

| Двухрежимный распределитель импульсов для управления трехфазным шаговым двигателем | 1981 |

|

SU1019571A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1977 |

|

SU725184A1 |

| Многорежимный коммутатор для четырехфазного шагового двигателя | 1976 |

|

SU650195A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1981 |

|

SU1001423A1 |

| Устройство для управления шаговым двигателем | 1987 |

|

SU1481711A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU964951A1 |

| Устройство для управления @ -фазным шаговым электродвигателем | 1979 |

|

SU888323A1 |

Авторы

Даты

1979-05-15—Публикация

1976-03-30—Подача