(54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Устройство управления ключом напряжения | 1974 |

|

SU499659A1 |

| Стабилизированный источник питания | 1985 |

|

SU1265745A1 |

| Интегральный усилитель для стереофонической аппаратуры магнитной записи | 1979 |

|

SU1003138A1 |

| Устройство выделения синхронизирующих импульсов | 1978 |

|

SU930745A1 |

| Усилитель мощности | 2023 |

|

RU2796545C1 |

| Импульсный стабилизатор напряжения постоянного тока | 1986 |

|

SU1410003A1 |

| Стабилизатор постоянного напряжения | 1978 |

|

SU736077A1 |

| Преобразователь постоянного напряжения | 1979 |

|

SU773609A1 |

| Преобразователь импульсов | 1983 |

|

SU1145433A1 |

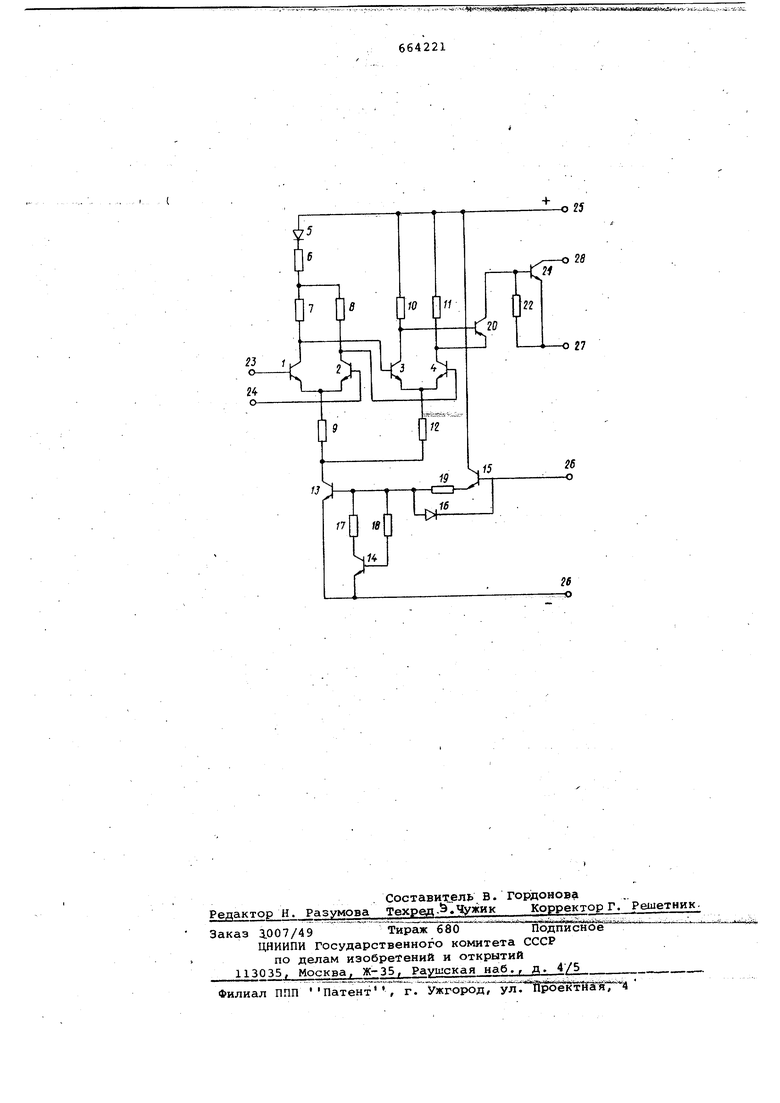

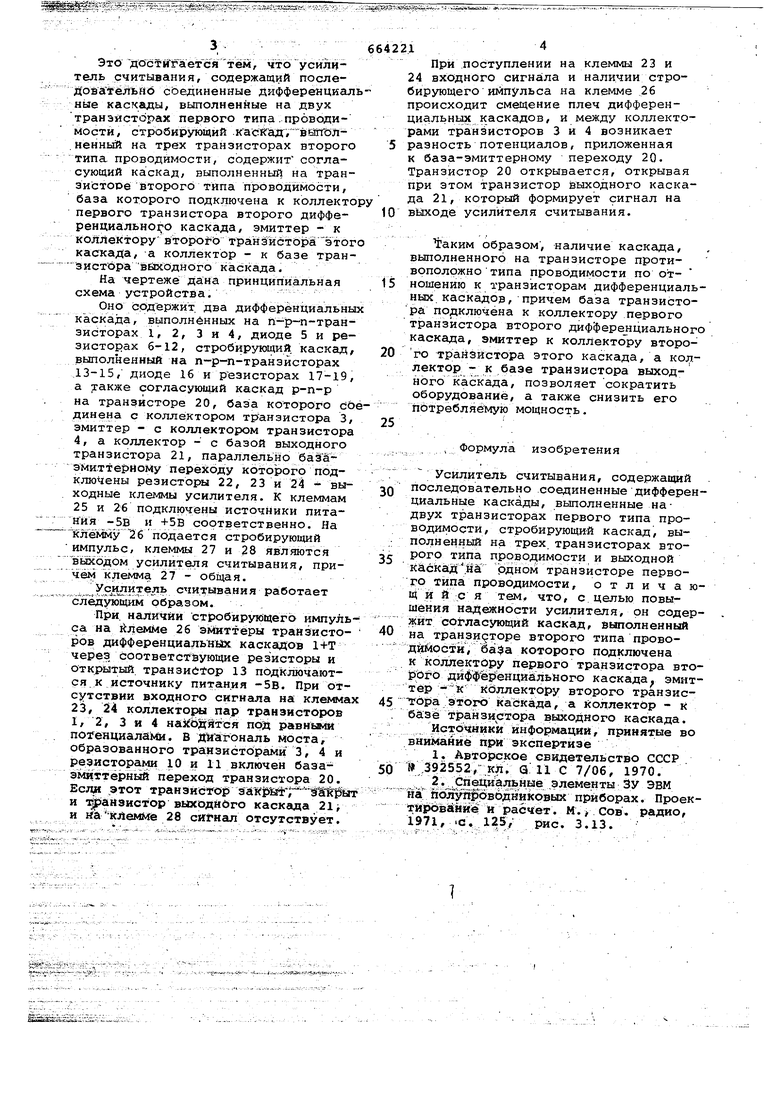

Изобретение относится к автомати ке и вычислительной техникеи может быть использовано в устройствах вычислительной техники, например в ЦВМ. Известны усилители считывания, содержащие дифференциальные и стробирующие каскады, -выполненные на транзисторах одной проводимости. Аналогичным устройством является усилитель считывания, который содер жит дифференциальный каскад и специальный переходной каскад, использование которого обеспечивает симметричную нагрузку для обоих плеч дифференциального каскада, а, следовательно, и подавление синфазной помехи. Однако использование специального переходного каскада для получения симметричного перехода с дифференциального усилителя на последующие несимметричные каскады усложняет схему усилителя, а также повышает потребляемую им мощность Наиболее близким к изобретению по технической сущТчости из известны является усилитель считывания, содержащий дифференциальный входной каскад, между коллекторами транзистора которого вк;1ючеи база-эмиттерный переход выходного транзистора, с коллектора которого снимается выходной сигнал. Выходной транзистор имеет тот же тип проводимости, что и транзисторы дифференциального каскада. Однако использование выходного транзистора той же проводимости приводит к необходимости сопряжения уровней напряжения питания устройства. Для нормальной работы выходного транзистора при этом необходимо подк.гаочить его ко.гшектор к более высокому напряжению питания, нежели кол.лекторы транзисторов дифференциального каскада. Это усложняет устройство, так как требует специальных узлов,, обеспечивающих сопряжение уровней питающих напряжений. Для этой цели используются лелитеЛи напряжения. Естественно, наличие специальных сопрягающих узлоь и необходимость более высокого питающего напряжения на выходном транзисторе не только усложняет схему усилителя, но и существенно пов1лиает его потребляемую мощность . Цель изобретения - повышение надежности усилителя. ЭтоflCic ifraieTCHтем, что усилитель считывания, содержащий последоватёЯьйб сЬединенные дифференциал ные каскады, вьтолненйые на двух транзисторах первого типа.проводимости, стробирукяций .,вШ1:Ьлненный на трех транзисторах второго типа проводимости, содержит согласующий каскад, выполненный на транэистоое второго типа проводимости, база которого подключена к коллекто первого транзистора второго дифференциально: О каскада, эмиттер - к коллектору второго транзйстЬра этог каскада, а коллектор - к базе тран зистбравйходного каскада. На чертеже цана принципиальная схема устройства. Оно содержит два дифференциальны каскада, выполненных на п-р-п-транзисторах 1, 2, 3 и 4, диоде 5 и резисторах 6-12, стробирующий. каскад выполненный на п-р-п-транзйсторах 13-15, диоде 16 и резисторах 17-19 а также согласующий каскад р-п-р на транзисторе 20, база которого сЬ динена с коллектором транзистора 3 эмиттер - с коллектором транзистора 4, а коллектор - с базой выходного транзистора 21, параллельно базаэмитте1 ному переходу которого подключены резисторы 22, 23 и 24 - выходные клеммы усилителя. К клеммам 25 и 26 подключены источники питанИя -5в и +5В соответственно. На клемму 26подается стробирующий импульс, клеммы 27 и 28 являются вЕлсодом усилителя считывания, причём клемма 27 - общая. Ус илитель считывания работает следующим образом. При наличии стробируйщего импуль са на йлемМе 26 эМнттёры транзисторов дифференциальных каскадов 1+Т через, соответствующие резисторы и открытый транзистор 13 подключаются, к источнику питания -5в. При отсутствии входного сигнала на клемма 23, 24 коллекторы пар транзисторов 1, 2, 3 и 4 на ЬдМтся пр равными пофенциалакси. В д агональ моста, образованного транзисторами 3, 4 и резисторами 10 и И включен базаэНедттёрньЙ переход транзистора 20. Ecjui этот транзистор з акЭМ 1§адр| а и -фанзистор выходного каскада 21; i a KЛемме 28 сйггнал отсутствует. При поступлении на клеммы 23 и 4 входного сигнала и наличии строирующего импульса на клемме 26 роисходит смещение плеч дифферениальных каскадов, и между коллектоами тра нзисторов 3 и 4 возникает азность потенциалов, приложенная база-змиттерному переходу 20. ранзистор 20 открывается, открывая ри зтом транзистор выходного каскаа 21, который формирует сигнал на 1аходе усилителя считывания. образом, наличие каскада, выполненного на транзисторе противоположно типа проводимости по отношению к транзисторам дифференциальных, каскадов, причем база транзистора подключена к коллектору первого транзистора второго дифференциального каскада, эмиттер к коллектору второго транзистора этого каскада, а коллектор - к базе транзистора выходного каскада, позволяет сократить оборудование, а также снизить его потребл:яёмую мощность. .Формула изобретения Усилитель считывания, содержащий последовательно соединенные дифференциальные каскады, выполненные надвух транзисторах первого типа проводимости, стробирующий каскад, выполненный на трех транзисторах второго типа проводимости,и выходной каскадни одном транзисторе первого типа проводимости, отличающ и Йен тем/что, с целью повышения надежности усилителя, он содержй:т согласующий каскад, выполненный на транзисторе второго типа провоДйМостй, ёаЗа которого подключена к коллектору первого транзистора вторЪгО диФФёЕ ёйциального каскада эмиттер - к коллектору второго транзистгора этого каскада, а коллектор - к базе т ранзистора выходного каскада. Источники информации, принят;ые во внимание при экспертизе 1,Авторское свидетельство СССР , Kji, а 11 С 7/06, 1970. 2..Специальные .элементы; ЗУ ЭВМ на йдлуйроводниковых приборах. ПроектйрЬзваШе и расчет. М. Сов. радио, 1971, .с. 125, рис. 3.13.

664221

о 25

Авторы

Даты

1979-05-25—Публикация

1978-02-20—Подача