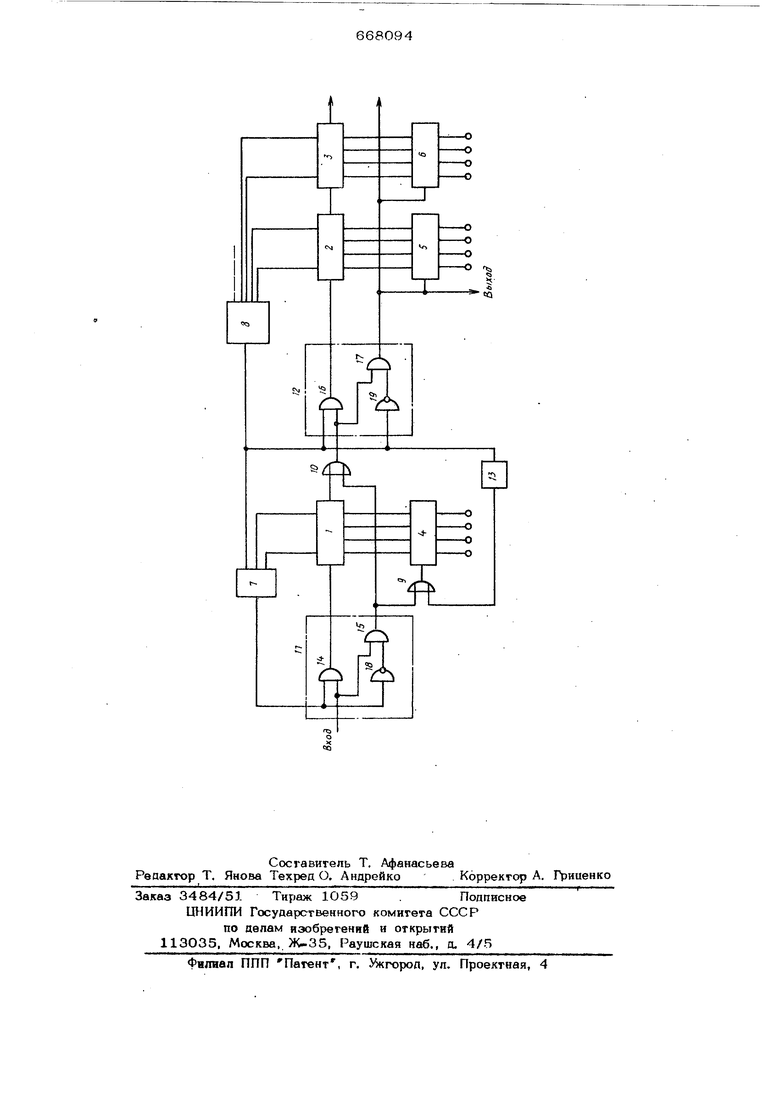

цовагельно, и обеспечить максимальную разрешаюшую способность пересчетного устройства по следующим причинам: при повышении входной частоты из-за зацерж ки входных сигналов в тракте счета и опо навания второй декады невозможно осуше ствлять малые коэффициенты пересчета де кады младших разрядов; в младшую счетную декаду запись осушествляется в промежутке между входными импульсами, для чего необходимо дополнительное устройство синхронизации в блоке занесения кода (иначе появляются сбои в работе этой декады); усложнена запись кода во вторую и последуюшие декады, что вызывает пропуски входных импульсов. С целью повыш:ения разрешаюшей способности устройства и повышения надежности его работы в делитель частоты с переменным коэффициентом деления, содер жащий счетные декады, блоки занесения кода и элементы совпадения, введены вен тили, элементы ИЛИ в формирователь, вход которого соединен с выходом второго элемента совпадения, а выход - с первым входом первого элемента ИЛИ, выхо которого подключен к входу блока занесения кода младшей счетной декады, при этом первый вход первого вентиля соединен с входной шиной, второй вход - с выходом первого элемента совпадения, первый выход через младшую счетную декаду с первым входом второго элемента ИЛИ, второй выход - со вторыми входами первого и второго элементов ИЛИ, а выход, второго элемента ИЛИ подключен к перво му входу второго вентиля, второй вход которого соединен с выходом втррого эле мента совпадения, первый выход - со вхо дом старшей счетной декады, а второй вы ход - со входами блоков занесения кода старших счетных декад. На чертеже представлена структурная электрическая схема предлагаемого делителя частоты с переменным коэффициентом деления. Устройство содержит младшую декаду 1 и старшие декады 2,3, блоки 4-6 занесения кода, элементы совпадения 7,8 (опознавание заполнения разрядов младше и старших декад), элементы ИЛИ 9, 10 вентили 11, 12 сигналов счета и установ ки начального состояния младшей и старших декад, формирователь 13, при этом вв1.тили 11, 12 состоят иэ элеменгов И 14 - 17 и инверторов 18, 19. Устройство рабогает следующим обра.аом. Перед началом счета в счетные декадр.г 1-3 записываются числа, соответстпуютгше дополнительному коду. При коэффициенте пересчета от 1 до 9, если запись в декады произведена, разрешающий сигнал на выходе элемента совпадения 8 подготавливает элемент совпадения 7 к работе, так как счетные /декады 2 и 3 находятся в состоянии 100 1. Входные импульсы проходят через вентиль 11 на младшую декаду 1, так как на выходе элемента совпадения 7 присутствует разрешающий сигнал. Когда в процессе счета в младшей декаде 1 устанавливается состояние 100 1, на выходе элемента совпадения 7 появляется разрешающий сигнал для элемента И 15, следующий входной импульс через элемент И 15 и элемент ИЛИ 9 записывает код в следующую декаду. Этот же сигнал, пройдя через элемент ИЛИ 10 и элемент И 17, является выходным. После записи кода младша.я счетная декада 1 опять считает входные импульсы с заданным коэффициентом пересчета. Повторная загрузка счетной декады заданным кодом здесь осуществляется самим входным сигналом. При коэффициенте пересчета от Ю до 99 в счете входных сигналов участвуют декады 1 и 2, а в декаде 3 сохраняется состояние 100 1. После записи кода в декады 1 и 2 происходит счет импульсов. Входы элементов И 15, 17 для записи кода в декады 1 и 2 блокированы запрещ.ающими сигналами с инверторов 18, 19. Сигнал переноса при насыщении младшей декады 1, снимаемый с ее выхода несет частоту в десять раз меньше входной и проходит через элемент ИЛИ 10 и вентиль 12 на вход декады 2.. При насыщении декады 2 выходной сигнал элемента совпадения 8 блокирует дальнейшее прохождение импульсов на вход декады 2, повторной записью дополнительного кода через формирователь 13 и элемент ИЛИ 9 восстанавливает исходное состояние декады 1, а также подготавливает элемент совпадения 7 и элемент И 17 к работе. При запойнении декады 1 элементом совпадения 7 формируется разрешающий уровень для записи кода в декаду 1 через элемент И 15 и элемент ИЛИ 9 следующим входным импульсом. Этот же импульс, являясь выходным для декады 1, в этом случав, пройдя через элемент И 16 и 17, производит запись кода в декады 2 и 3 через блоки 5 и 6. Одновременно он проходит и на выход устройства. При такой структуре коэффициент деления двух пекап равен Ю Кд ., где К - ко9г} иииент деления декапы 2, Л коэффициент деления декады 1. Такой коэ4 1ициенг деления реализуется псюреп- ством использования элемента ИЛИ Ю. Так как запись кода в декаду 2 произ- водится- входным сигналом, то вентиль 12 не пропускает импульсы на вход декады 2 до окончания процесса записи в ней при малых коэффициентах пересчета в декаде 1. При повышении входной частоты в тракте счета и опознавания декады 2 происходит задержка входных сигналов, что вызывает ложные заполнения входными импульсами декады 1 до прихода разрешаюшего сигнала на элемент совпадени 7 с элемента совпадения 8 и младшей счетной декады 1, причем разрешаюшая способность декады 1 понижается. Для устранения этого сформированный формиро вателем. 13 Импульс через элемент И ЛИ 9 очишает декаду 1 от лишних импульсов появляющихся в реальных схемах. Это позволяет получить максимальную разрешающую способность при реализации максимальногр быстродействия выбранных логических схем доступным способом. Лишние импульсы в декаде 1 могут быть учтены при необходимости установкой допол нительного счетчика в цепи записи кода в декаду 1. устройства при коэффициентах г ,. -9та от 100 до , где т- копкчество счетных декад, происходит с тем лишь различием, что выполнение старших декад происходит дольше и определяется .их числом. Формула изобретения Делитель частоты с переменным коэффициентом целения, содержащий счетные Декады, вхоцы которых соединены с выходами соответствующих блоков занесения кода, выходы младшей счетной декады попклк чены к двум входам первого элемента совпадения, третий вход которого подключен к выходу второго элемента совпадения, входы которого соединены с выходами старших счетных декад, соединенных последовательно, отличающийся тем, что, с целью повышения разрещаюшей способности устройства и повышения надежности его работы, в него введены .вентили, элементы ИЛИ и формирователь, вход которого соединен с выходом второго элемента совпадения, а выход - с первым входом первого элемента ИЛИ, выход которого подключен к входу блока занесения кода младшей счетной декады, при этом, первый вход первого вентиля соединен с входной шиной, второй вход - с выходом первого элемента совпадения, первый выход через младшую счетную декаду - с первым вхо дом второго элемента ИЛИ, второй выходсо вторыми входами первого и второго элементов ИЛИ, а выход второго элемента ИЛИ подключен к первому входу второго вентиля, второй вход которого соединен с выходом второго элемента совпадения, первый выход -со входом старшей счетной декады, а второй выход - со входами блоков занесения кода старших счетных декад. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 311268, кп. G 06 F 7/52, 1971; 2. Авторское свидетельство СССР № 446951, кл. Н ОЗ К 23/02, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многодекадное пересчетное устройство | 1972 |

|

SU446951A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| УСТРОЙСТВО для СЧЕТА ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1971 |

|

SU311406A1 |

| Каскад программируемого делителя частоты | 1980 |

|

SU919091A1 |

| Цифровой измеритель скорости | 1978 |

|

SU1029081A1 |

| Одноканальное устройство для управленияВЕНТильНыМ пРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU839007A1 |

| Одноканальное устройство для управления вентильным преобразователем | 1978 |

|

SU714618A1 |

| Электронные часы | 1984 |

|

SU1224786A1 |

| Многодекадное пересчетное устройство с управляемым коэффициентом пересчета | 1978 |

|

SU752814A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

Авторы

Даты

1979-06-15—Публикация

1976-12-16—Подача