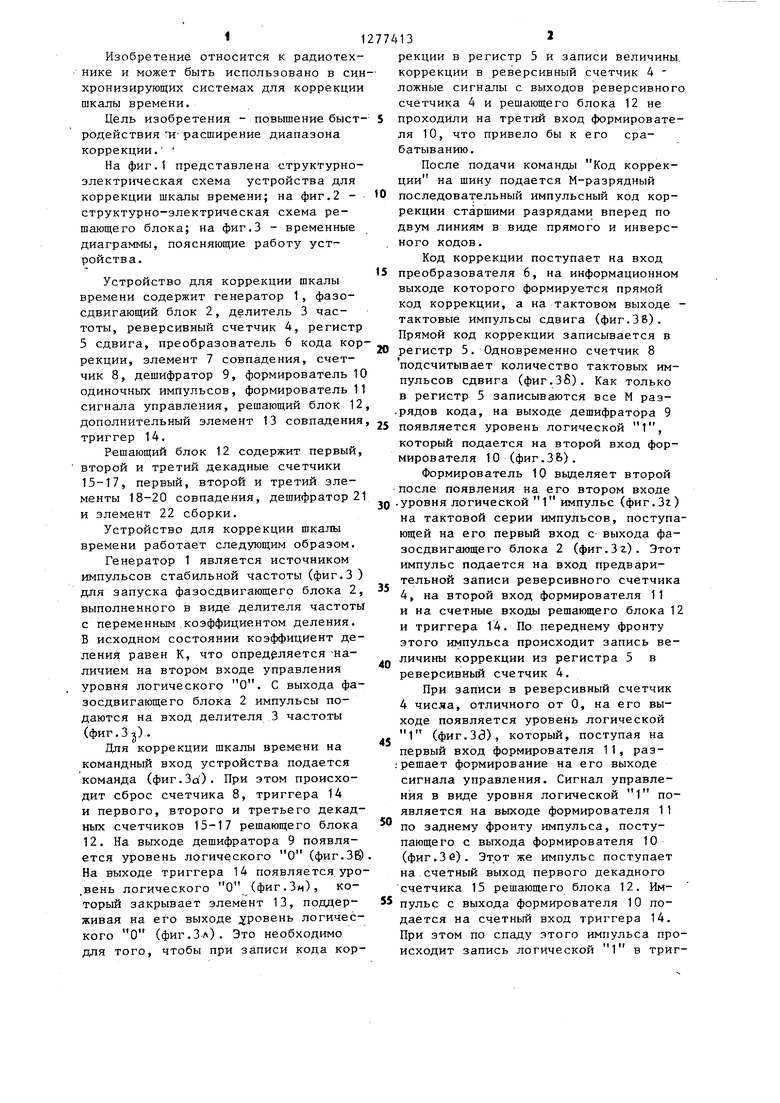

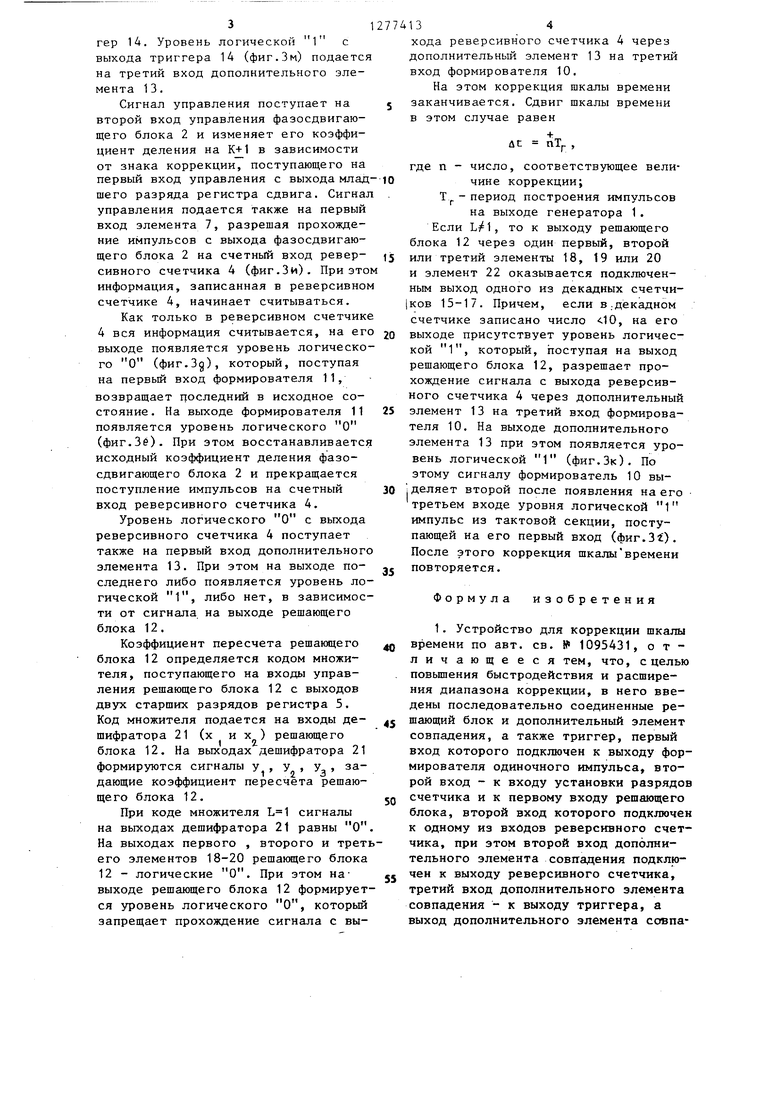

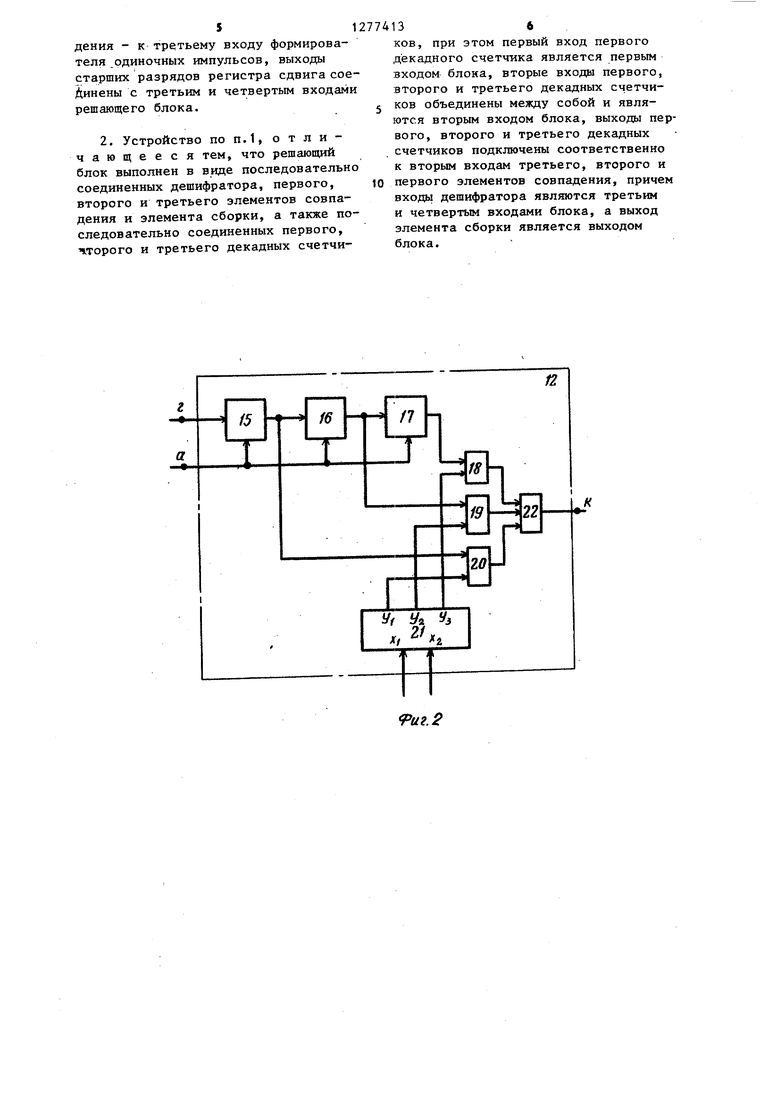

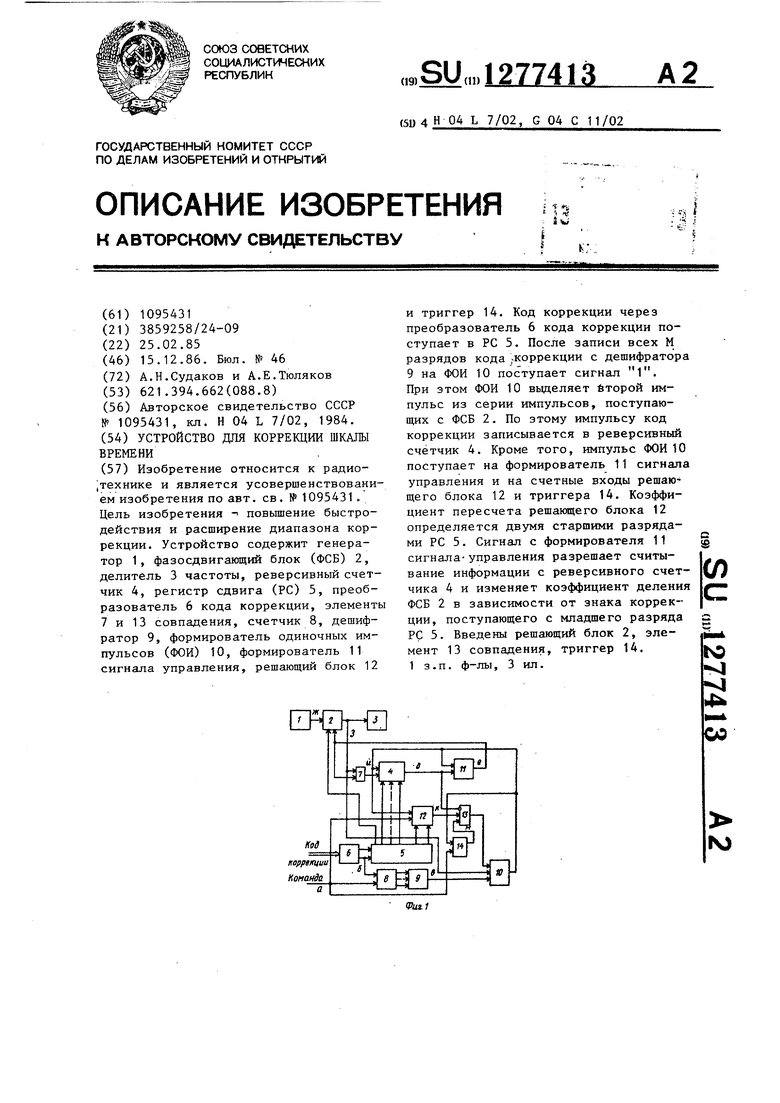

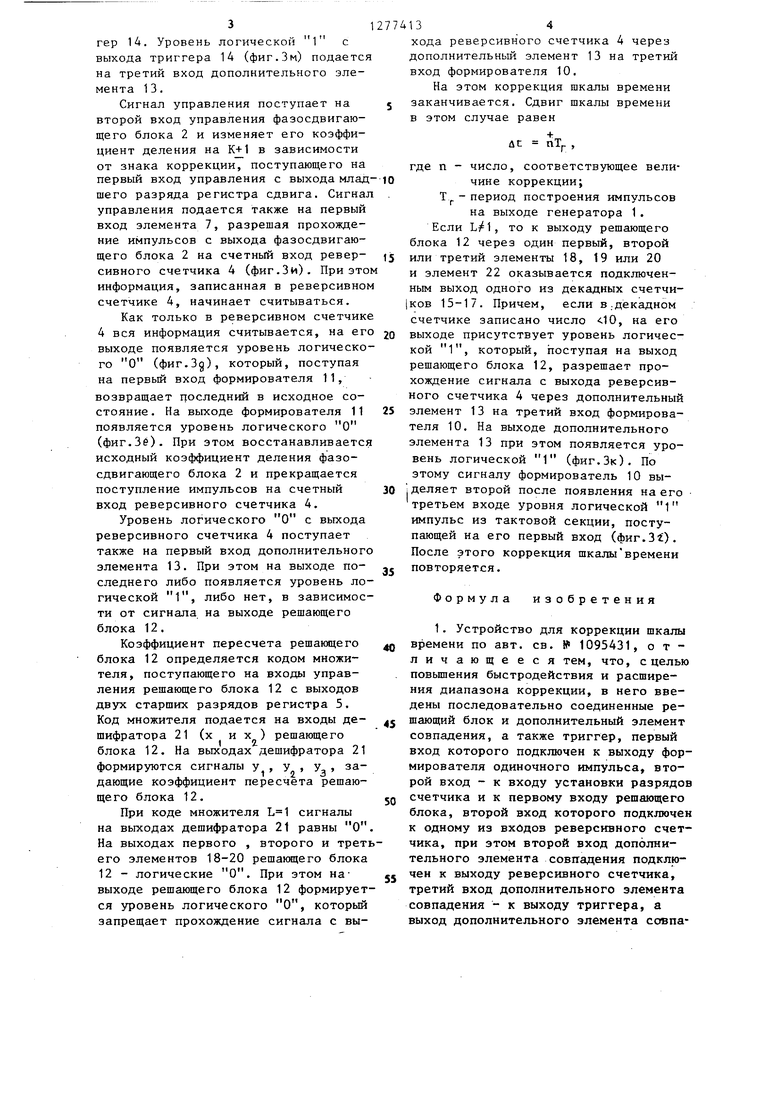

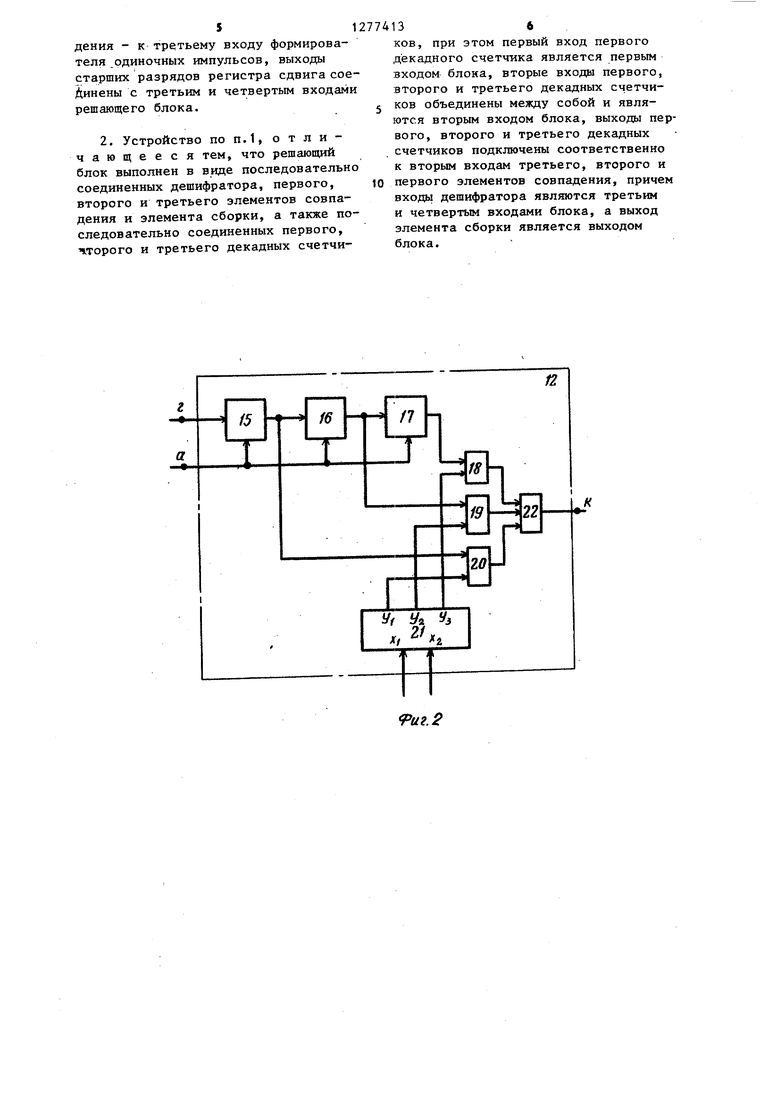

Изобретение относится к радиотехнике и может быть использовано в си хронизирующих системах для коррекции шкалы времени. Цель изобретения - повышение быст родействия И расширение диапазона коррекции. На фиг.1 представлена структурноэлектрическая схема устройства для коррекции шкапы времени; на фиг.2 структурно-электрическая схема решающего блока; на фиг.З - временные диаграммы, поясняющие работу устройства. Устройство для коррекции шкалы времени содержит генератор 1, фазосдвигающий блок 2, делитель 3 частоты, реверсивный счетчик 4, регистр 5 сдвига, преобразователь 6 кода кор рекции, элемент 7 совпадения, счетчик 8, дешифратор 9, формирователь 1 одиночных импульсов, формирователь 1 сигнала управления, решающий блок 12 дополнительный элемент 13 совпадения триггер 14. Решающий блок 12 содержит первый второй и третий декадные счетчики 15-17, первый, второй и третий элементы 18-20 совпадения, дешифратор 2 и элемент 22 сборки. Устройство для коррекции шкалы времени работает следующим образом. Генератор 1 является источником импульсов стабильной частоты (фиг.З ) для запуска фазосдвигающего блока 2 выполненного в виде делителя частоты с переменным .коэффициентом деления. В исходном состоянии коэффициент деления равен К, что определяется -наличием на втором входе управления уровня логического О. С выхода фазосдвигающего блока 2 импульсы подаются на вход делителя 3 частоты (фиг.З р. Для коррекции шкалы времени на командный вход устройства подается команда (фиг.За). При этом происходит сброс счетчика 8, триггера 14 и первого, второго и третьего декадных счетчиков 15-17 решающего блока 12. На выходе дешифратора 9 появляется уровень логического О (фиг.ЗВ На выходе триггера 14 появляется, уро .вень логического О (фиг.Зн) который закрывает элемент 13, поддерживая на его выходе уровень логического О (фиг.3л). Это необходимо для того, чтобы при записи кода коррекции в регистр 5 и записи величины, коррекции в реверсивный счетчик 4 ложные сигналы с выходов реверсивного счетчика 4 и решающего блока 12 не проходили на третий вход формирователя 10, что привело бы к его срабатыванию. После подачи команды Код коррекции на шину подается М-разрядный последовательный импульсный код коррекции старшими разрядами вперед по двум линиям в виде прямого и инверсного кодов. Код коррекции поступает на вход преобразователя 6, на информационном выходе которого формируется прямой код коррекции, а на тактовом выходе тактовые импульсы сдвига (фиг.38). Прямой код коррекции записывается в регистр 5. Одновременно счетчик 8 подсчитывает количество тактовых импульсов сдвига (фиг.38). Как только в регистр 5 записываются все М разрядов кода, на выходе дешифратора 9 появляется уровень логической 1, который подается на второй вход формирователя 10 (фиг.36). Формирователь 10 вьщеляет второй после появления на его втором входе уровня логической 1 импульс (фиг.Зг) на тактовой серии импульсов, поступающей на его первый вход с выхода фазосдвигающего блока 2 (фиг.Зг). Этот импульс подается на вход предварительной записи реверсивного счетчика 4, на второй вход формирователя 11 и на счетные входы решающего блока 12 и триггера 14. По переднему фронту этого импульса происходит запись величины коррекции из регистра 5 в реверсивный счетчик 4. При записи в реверсивный счетчик 4 числа, отличного от О, на его выходе появляется уровень логической 1 (фиг.ЗЭ), который, поступая на первый вход формирователя 11, разрешает формирование на его выходе сигнала управления. Сигнал управления в виде уровня логической 1 появляется на выходе формирователя 11 по заднему фронту рмпульса, поступающего с выхода формирователя 10 (фиг.Зи). Этот же импульс поступает на счетный выход первого декадного счетчика 15 решающего блока 12. Импульс с выхода формирователя 10 подается на счетный вход триггера 14. При этом по спаду этого импульса происходит запись логической 1 в тригrep 14. Уровень логической 1 с выхода триггера 14 (фиг.3м) подается на третий вход дополнительного элемента 13.

Сигнал управления поступает на второй вход управления фазосдвигающего блока 2 и изменяет его коэффициент деления на в зависимости от знака коррекции, поступающего на первый вход управления с выхода младшего разряда регистра сдвига. Сигнал управления подается также на первый вход элемента 7, разрешая прохождение импульсов с выхода фазосдвигающего блока 2 на счетный вход реверсивного счетчика 4 (фиг.Зи). При этом информация, записанная в реверсивном счетчике 4, начинает считываться.

Как только в реверсивном счетчике 4 вся информация считывается, на его выходе появляется уровень логического О (фиг.Зд), который, поступая на первый вход формирователя 11, возвращает последний в исходное состояние . На выходе формирователя 11 появляется уровень логического О (фиг.Зе). При этом восстанавливается исходный коэффициент деления фазосдвигающего блока 2 и прекращается поступление импульсов на счетный вход реверсивного счетчика 4.

Уровень логического О с выхода реверсивного счетчика 4 поступает также на первый вход дополнительного элемента 13. При этом на выходе последнего либо появляется уровень логической 1, либо нет, в зависимости от сигнала, на выходе решающего блока 12.

Коэффициент пересчета решаницего блока 12 определяется кодом множителя, поступающего на входы управления решающего блока 12 с выходов двух старших разрядов регистра 5, Код множителя подается на входы дешифратора 21 (х их) решающего блока 12. На выходах дешифратора 21 формируются сигналы у , у , у , задающие коэффициент пересчета решающего блока 12,

При коде множителя сигналы на выходах дешифратора 21 равны О. На выходах первого , второго и третьего элементов 18-20 решакнцего блока 12 - логические О. При этом на выходе решающего блока 12 формируется уровень логического О, который запрещает прохождение сигнала с выхода реверсивного счетчика 4 через дополнительный элемент 13 на третий вход формирователя 10.

На этом коррекция шкалы времени заканчивается. Сдвиг шкалы времени в этом случае равен

At пТр ,

где п - число, соответствующее величине коррекции; Т J. - период построения импульсов

на выходе генератора 1 . Если , то к выходу решающего блока 12 через один первый, второй или третий элементы 18, 19 или 20 и элемент 22 оказывается подключенным выход одного из декадных счетчиIKOB 15-17. Причем, если в.декадном счетчике записано число 10, на его выходе присутствует уровень логической 1, который, поступая на выход решающего блока 12, разрешает прохождение сигнала с выхода реверсивного счетчика 4 через дополнительный элемент 13 на третий вход формирователя 10, На выходе дополнительного элемента 13 при этом появляется уровень логической 1 (фиг,3к). По этому сигналу формирователь 10 вы|деляет второй после появления на его третьем входе уровня логической 1 импульс из тактовой секции, поступающей на его первый вход (фиг,3). После этого коррекция шкалывремени повторяется.

Формула изобретения

1, Устройство для коррекции шкалы времени по авт, ев, № 1095431, отличающееся тем, что, с целью повьш1ения быстродействия и расширения диапазона коррекции, в него введены последовательно соединенные решающий блок и дополнительный элемент совпадения, а также триггер, первый вход которого подключен к выходу формирователя одиночного импульса, второй вход - к входу установки разрядо счетчика и к первому входу решающего блока, второй вход которого подключе к одному из входов реверсивного счетчика, при этом второй вход дополнительного элемента совпадения подключен к выходу реверсивного счетчика, третий вход дополнительного элемента совпадения - к выходу триггера, а выход дополнительного элемента совпадения - к третьему входу формирователя одиночных импульсов, выходы старших разрядов регистра сдвига сое Динены с третьим и четвертым входам решающего блока. 2. Устройство по п.1, отличающееся тем, что решающий блок выполнен в виде последовательн соединенных дешифратора, первого, второго и третьего элементов совпадения и элемента сборки, а также по следовательно соединенных первого, второго и третьего декадных счетчи13ков, при этом первый вход первого декадного счетчика является первым входом блока, вторые входы первого, второго и третьего декадных счетчиков объединены между собой и являются вторым входом блока, выходы первого, второго и третьего декадных счетчиков подключены соответственно к вторым входам третьего, второго и первого элементов совпадения, причем входы дешифратора являются третьим и четвертым входами блока, а выход элемента сборки является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1413590A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство коррекции шкалы времени | 1988 |

|

SU1525932A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

Изобретение относится к радио|технике и является усовершенствованием изобретения по авт. св. № 1095431. Цель изобретения - повышение быстродействия и расширение диапазона коррекции. Устройство содержит генератор 1, фазосдвигающий блок (ФСБ) 2, делитель 3 частоты, реверсивный счетчик 4, регистр сдвига (РС) 5, преобразователь 6 кода коррекции, элементы 7 и 13 совпадения, счетчик 8, дешифратор 9, формирователь одиночных импульсов (ФОИ) 10, формирователь 11 сигнала управления, решающий блок 12 и триггер 14. Код коррекции через преобразователь 6 кода коррекции поступает в PC 5. После записи всех М разрядов кода коррекции с дешифратора 9 на ФОИ 10 поступает сигнал 1. При зтом ФОИ 10 вьщеляет бторой импульс из серии импульсов, поступающих с ФСБ 2. По зтому импульсу код коррекции записывается в реверсивный счётчик 4. Кроме того, импульс ФОИ 10 поступает на формирователь 11 сигнала управления и на счетные входы решающего блока 12 и триггера 14. Козффициент пересчета решакяцего блока 12 определяется двумя старшими разрядаi ми PC 5. Сигнал с формирователя 11 сигнала-управления разрешает считы(Л вание информации с реверсивного счетчика 4 и изменяет коэффициент деления ФСБ 2 в зависимости от знака коррекции, поступающего с младшего разряда PC 5. Введены решающий блок 2, элемент 13 совпадения, триггер 14. 1 3.п. ф-лы, 3 ил. К)

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-15—Публикация

1985-02-25—Подача