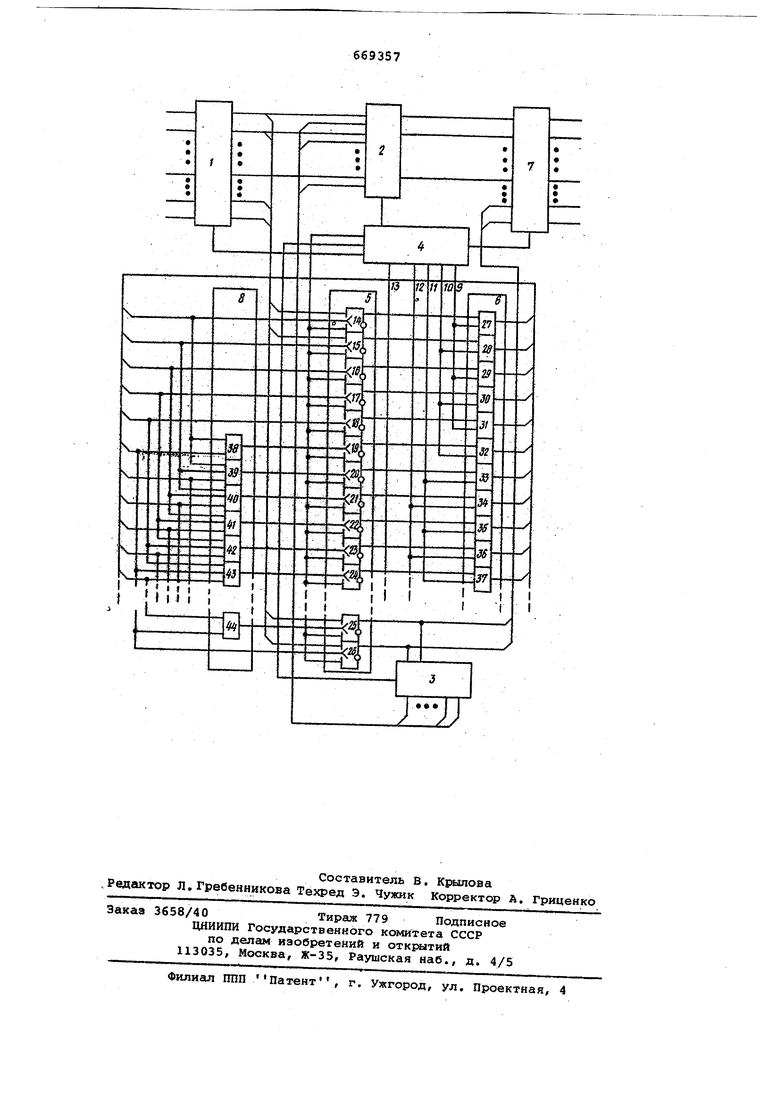

Изобретение отиосится к вычислительной технике и может быть использовано как при передаче информации между вычислительной машиной и внеШ ними устройствс1ми, так и между устро ствами внутри машины. Кроме того, оно может применяться в технике дискретной связи. Известно устройство для кодирования и декодирования циклических кодов , содержащее регистр с фиксированными цепями сложения (вычитания) по модулю два порождающего полинома G(X)f через которые последовательно продвигается кодируемое -декодируемое слово 1. Недостатком такого устройства является малое быстродействие, объясняемое тем, что его цикл работы Тц-е-Тс где - разрядность кодируемого двоичного слова; TcgT период следования сдвигающих импульсов Наиболее близкое к предлагаемому изобретению устройство для кодирования и декодирования циклических кодо содержит блок ввода информации, приемный и операционный регистры, группу злементов И, группу элементов ИЛИ блок управления, блок вывода результата и дешифратор остатка, причем входы блока ввода являются входами устройства, а выходы соединены соответственно с входами приемного и операционного регистров, выходы приемного регистра соединены соответственно с входами блока вывода результата, выходы операционного регистра соединены с первыми входами элементов И группы, выходы которых соединены с входами операционного регистра и элементов ИЛИ группы в соответствии с кодом, выходы элементов ИЛИ группы соответственно соединены с входгъмиоперационного регистра, роответствующие выходы которого соединены с входами дешифратора остатка и блока вывода результата, выходы дияифратора остатка соединены соответственно с входами приет 1ного регистра, выходы блока управления соединены с управляющими входами блока ввода информации, приемного и операционного регистров, дешифратора остатка и блока вывода результата 2. Недостатком этого устройства является малое быстродействие, так как цикл работы зависит от количества единиц в кодируемом (декодируемом) сло-зоф -xraf Т ве -t(, Val Xq - rt eg Цель изобретения - повышение быст родействия. Это достигается тем, что соответствующие выходы блока управления сое .динены с вторыми входами тех элементов И группы, выходы которых соедине ны с входами разноименных элементов ИЛИ группы. Время кодирования (декодирования) этого устройства Тц const; К -eg , где К - степень порождающего полином Повышение быстродействия достигается совмещением во времени прибавлений порождающего полинома, исключающем одновременное появление еди ниц на счетных входах операционного регистра. На чертеже дана блок-схема устрой ства для кодирования и декодирования циклических кодов. Устройство содержит блок 1 ввода информации, приемный регистр 2, дешифратор 3 остатка, блок 4 управления, операционный регистр 5, группу элементов И 6, блок 7 вывода результата, группу элементов ИЛИ 8, выходы 9-13 блока управления. Операционный регистр 5 содержит разряды 14-26 Группа элементов И 6 содержит элемен ты И 27-37. Группа элементов ИЛИ 8 содержит элементы ИЛИ 38-44. Выполнение операционного регистра 5, группы элементов И б, группы элементов ИЛИ 8 и их связей произведено в соответствии с порождающим поли номом G(X) Х 4- X + 1 (1000011). Блоц 1 ввода информации предназначен для занесения кодируемого и декодируемого слов на операционный 5 и приемный 2 регистры в соответствии с сигналом, поступающим из блока 4 управления. Его выходы соединены с входами соответствующих разрядов приемного 2 и операционного 5 регистров. Приемный регистр 2 служит для хра нения г старших разрядов слова в тбнение цикла кодирования и декодировдния. в случае обнаружения ошибки в декодируемом слове, здесь же произво дится ее исправление. Регистр 2 содержит разрядов, вы ходы которых соединены с входами соо ветствуюдих разрядов блока 7 вывода результата, а входы - с выходами бло ка 1 ввода информации. Входы его раэ I рядов соединены с выходами дешифратора 3 остатка. Дешифратор 3 остатка предназначен для анализа состояния (е+1 - К) разрядов операционного регистра 5, целью выявления ошибки в принятом ко довом слове и выдачи сигналов корре ции в соответствукэдий ра-зряд приемнбго регистра 2.. Его входы соединены выходами i+i - I +к разрядов опера-, ционного регистра 5, выходы - со счетными входами приемного регистра 2. Блок 4 управления управляет работой устройства. Он соединен с элементами И 6 группы, с операционным регистром 5, с дешифратором 3 остатка, с блоком 1 ввода информации, с приемным -регистром 2 и блоком 7 вывсзда результата. Блок 7 вывода результата предназначен для выдачи слова, содержащего Е+ k разрядов, из устройства. старших разрядов поступают с выхода приемного регистра 2, а К младших разрядов - с выхода операционного регистра 5. Операционный регистр 5 содержит I + К разрядов и осуществляет фиксирование промежуточных результатов при кодировании и декодировании. Выходы старших разрядов соединены с соответствующими входами элементов И 6 группы, а выходы К. младших разрядов - с входами дешифратора 3 остатка и блока 7 вывода результата. Входа разрядов операционного регистра 5 соединены с выходами элементов ИЛИ 8 группы. Элементы И б группы анализируют состояние групп разрядов операционного регистра 5. Выходы элементов И 6 соединены с входшли разрядов операционного регистра 5 и эле чентов ИЛИ 8 группы в соответствии с видом порождающего полинома, а первые входы - с выходами операционного регистра 5, Вторые входы элементов И 6 в пределах групп из К. разрядов, начиная со .старшего, выходы которых соединены с входами разноименных элементов ИЛИ 8 группы, соединены с выходами блока 4 управления. Элементы ИЛИ.8 группы предназна-. чены для объединения сигналов с выходов элементов И 6 группы на входах разрядов операционного регистра 5. При кодировании блок 4 управления устанавливает регистры 2 и 5 в нуль, подготавливая устройство к работе. Его следующим сигналом - блок 1 ввода информации параллельно зано- . сит 1-Е разряды кодируемого слова в приемный регистр 2. Одновременно они заносятся на операционный регистр 5. При этом разряды + 1 - . + к операционного регистра 5 остаются нулевыми , Далее, блок 4 управления выдает серию импульсов таким образом, что первый из них идет на выход 9, второй - на выход 10 и т.д. При получении импульса, приходящего с выхода 9, группа элементов. И б элементами 27, 29, 31 опрашивает разряды 14, 16, 18 операционного регистра 5. В случае наличия в них единиц, сигналы с выходов элементов И 6 группы через элементы ИЛИ 8 группы поступают на

входы разрядов операционного регистра 5, производя тем самым соответствующее прибавление по модулю два порождающих полиномов. Таким образом, при наличии 1 в анализируемых разрядах, одновременно может произойти изменение состояния разрядов 14, 16, 18, 19, 20, 21, 22, 23 и 24, но ни на один из входов не может прийти два или более импульса.

Картина повторяется с приходом .импульса с выхода 10. Элементы И 28, 30, 32 производят опрос разрядов 15, 17, 19 и соответствующее прибавление порождающих полиномов. Процесс кодирования оканчивается анализом последней, из числа I старших разрядов, группы разрядов импульсом, проходящим с выхода 13. После чего в разрядах +1 - L+ К операционного регистра 5 получается остаток.

Блок 7 вывода результата получает импульс от блока 4 управления, в соответствии с которым он производит выдачу закодированного Е + К разрядного числа. При этом 1- разр ды числа Поступают в блок 7 вывода результата из приемного 2, а разряды E+l-t+К-из операционного 5 регистров.

Аналогично процессу кодирования, декодирование начинается с установки в нуль регистров 2 и 5 сигналом блока управления. Далее, € + К разрядное, слово с блока 1 ввода информации заносится на операционный регистр 5 в соответствии с сигналом блока 4 управления. Разряды 1-Е декодируемого слова заносятся также на приемный регистр 2. Обработка слова на операционном регистре 5 производится аналогично обработке при кодировании . И если оно содержало ошибку, по окончании обработки в + 1 - + К разрядах операционного регистра 5-ПОЯВИТСЯ код, отличный от нуля, В соответствии с ним, по команде блока 4 управления, на одном из выходов дешифратора 3 остатка образуется импульс. Поступая на вход соответствующего разряда приемного регистра 2, он устанавливает его в противоположное состояние. Если слов не было искажено в процессе передачи то разряды + 1 - 1 +К операционно6693576

го регистра 5 будут нулевыми и ни яа одном из выходов дешифратора 3 импульса не появится.

Вьадача результата производится так же, как при кодировании. Он получается на выходах 1-е разрядов блока 7 вывода результата.

Формула изобретения

Устройство для кодирования и декодирования циклических кодов, содержащее блок ввода информации, приемный и операционный регистры, группу элементов И, группу элементов ИЛИ, блок управления, .блок вывода результата и дешифратор остатка, входы блока ввода являются входами устройства , а выходы соединены соответственно с входами приемного и операционного регистров, выходы приемного регистра соединены соответственно с входами блока вывода результата, выходы onepauHOHHOi.o регистра соединены с первыми входами элементов И группы, выходы которых coesqHнены с входами операционного регистра и элементов ИЛИ группы в соответствии с кодом, выходам элементов ИЛИ группы соответственно соединены с входами операционного регистра, соответствующие выходы которого соединены с входами дешифратора остатка и блока вывода результата, выходы дешифратора остатка соединены соответственно с входами приёмного регистра, выходы блока управления соединены с упра:вляющими входами блока вво- да информации, приемного и операционного регистров, дешифратора остатка и блока вывода результата, отличающееся тем, что, с целью

повышения быстродействия, соответствукяцие выходы блока управления соединены с вторыми входами тех элементов И группы, выходы которых соединены с входами разноименных элементов ИЛИ группы-.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 318939, кл. G Об F 5/02, 1970.

2. Авторское свидетельство ССС 397904, кл. G 06 F 5/00, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразованиядВОичНОгО КОдА B избыТОчНыйциКличЕСКий КОд | 1978 |

|

SU798797A1 |

| Декодер укороченного кода Хэмминга | 1983 |

|

SU1109924A1 |

| Устройство для кодирования информации циклическим кодом | 1974 |

|

SU600740A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Способ диагностики недвоичных блоковых кодов | 2018 |

|

RU2693190C1 |

| Способ декодирования длинного блокового кода с помощью алгоритма Витерби | 2020 |

|

RU2747881C1 |

| Способ диагностики циклических кодов | 2016 |

|

RU2631142C2 |

| СПОСОБ КОДИРОВАНИЯ ИНФОРМАЦИИ ОТРЕЗКАМИ ЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2568320C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ОБНАРУЖЕНИЕМ ОШИБОК В СООБЩЕНИЯХ ПЕРЕМЕННОЙДЛИНЫ | 1972 |

|

SU328461A1 |

| ПАРАЛЛЕЛЬНЫЙ РЕКОНФИГУРИРУЕМЫЙ КОДЕР БЧХ КОДОВ | 2015 |

|

RU2591474C1 |

Авторы

Даты

1979-06-25—Публикация

1973-03-14—Подача