1

Изобретение относится к области вычислительной техники и предназначено для преобразования двоичного кода в циклические и избыточные корректирующие коды, обеспечивающие обнаружение и коррекцию ошибок в передаваемой информации.

Известно устройство кодирования, содержащее входной блок, приемный и операционный регистра, генератор ШушулъсоБ, блок управления, первый и второй блоки коммутации и блок выдачи результата Х7

Недостатком устройства является то, что его рабочий цикл зависит от количества единиц в кодируемом слове. То есть, скорость кодирования зависит от вида кЪдируемого слова и изменяется в п . раз (где п - количество разрядов кодируемого слова).

Известно также устройство для кодирования и декодирования циклических кодов, содержащее блок ввода информации, приемный и операционный регистры, группу элементов И, группу элементов ИЛИ, блок управления, блок вывода результата и дешифратор остатка 2 .

Недостатком устройства является то, что его структура зависит от вида применяемого порождающего полинома. А следовательно, оно не может применяться в тех случаях, где необходима смена порождающего полинома.

Известно также устройство декодирования циклического кода, содержащее сдвиговый регистр с обратной связью, детектор нуля, компаратор и счетчик f3 .

o

Однако это устройство обладает низким быстродействием.

Наиболее близким к предлагаемому является устройство для преобразования двоичного кода в избыточный ци5клический код, содержащее буферный регистр, регистр контрольных символов, блок многовходовых сумматоров по модулю основания кода, элемент И цепи выдачи результата и блок управления .

0

Недостатком устройства является его узкая специализация, т.е. то, что устройство позволяет кодировать двоичную последовательность только

5 в заданный циклический код, в соответствии с порождающим полиномом которого выполнена коммутация на входе регистра контрольных символов.

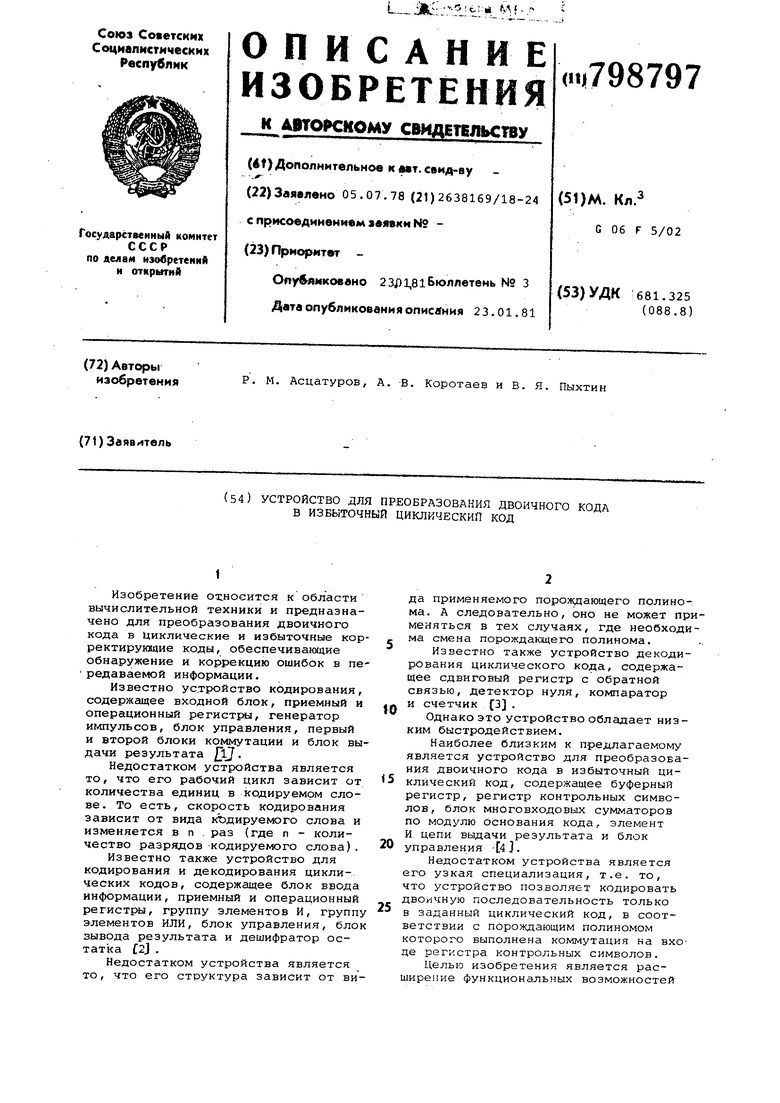

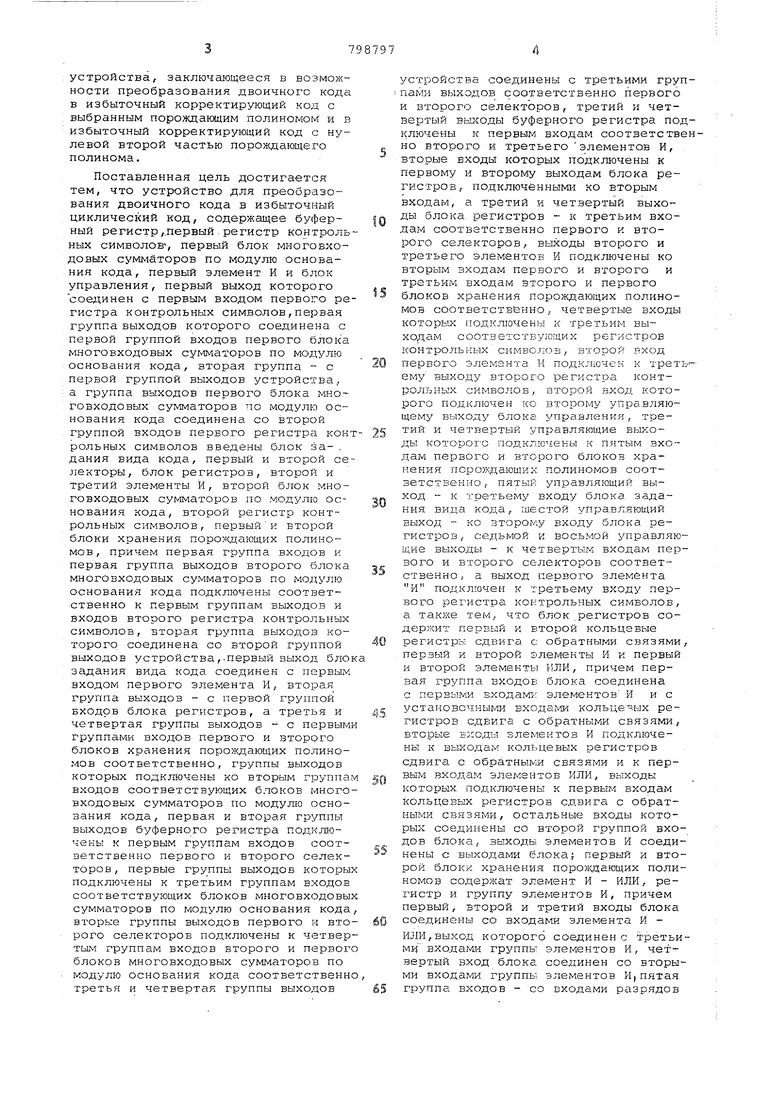

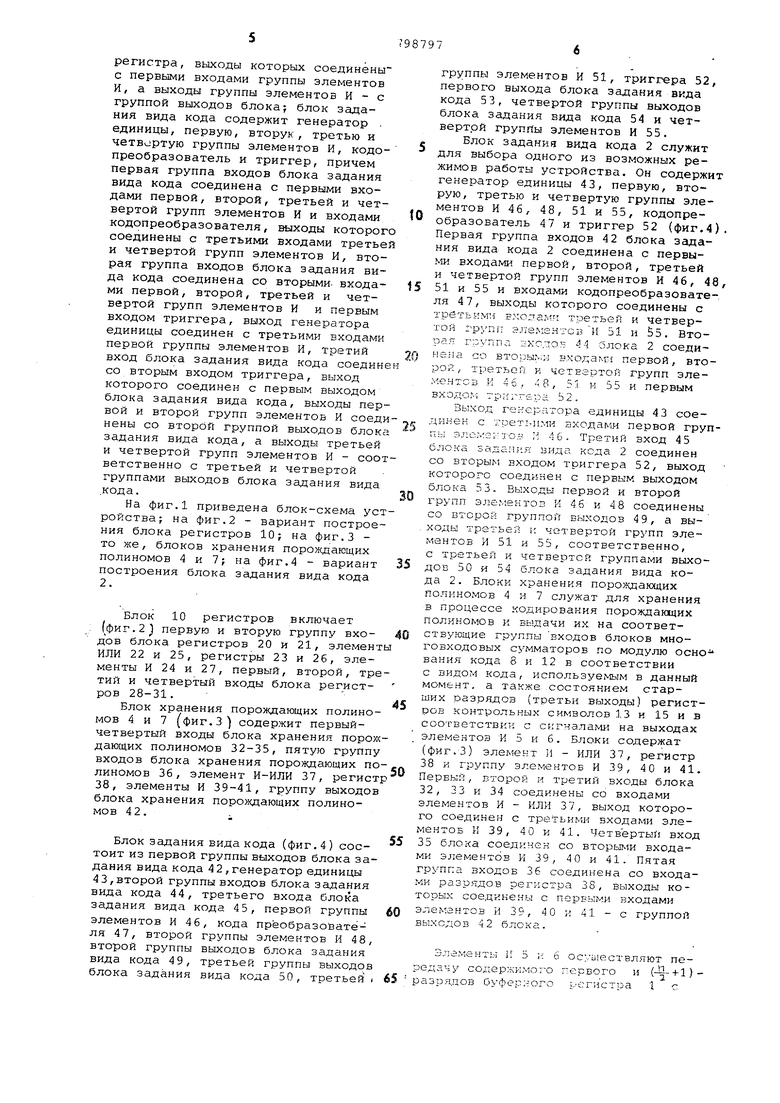

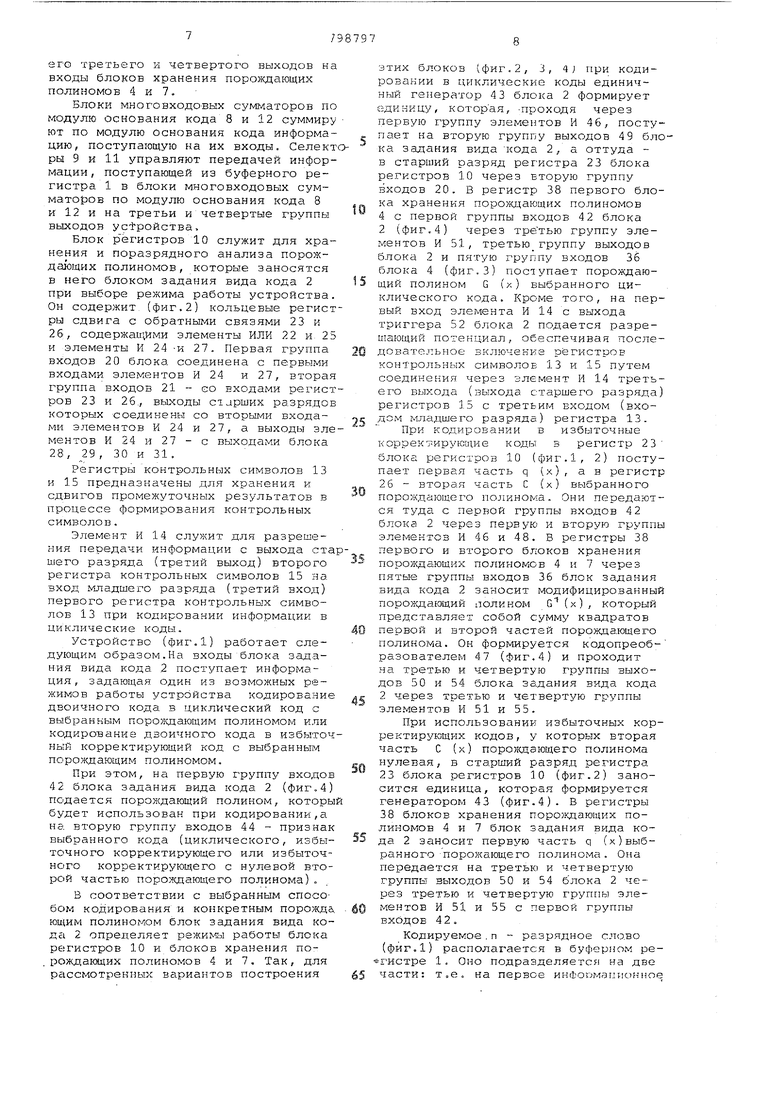

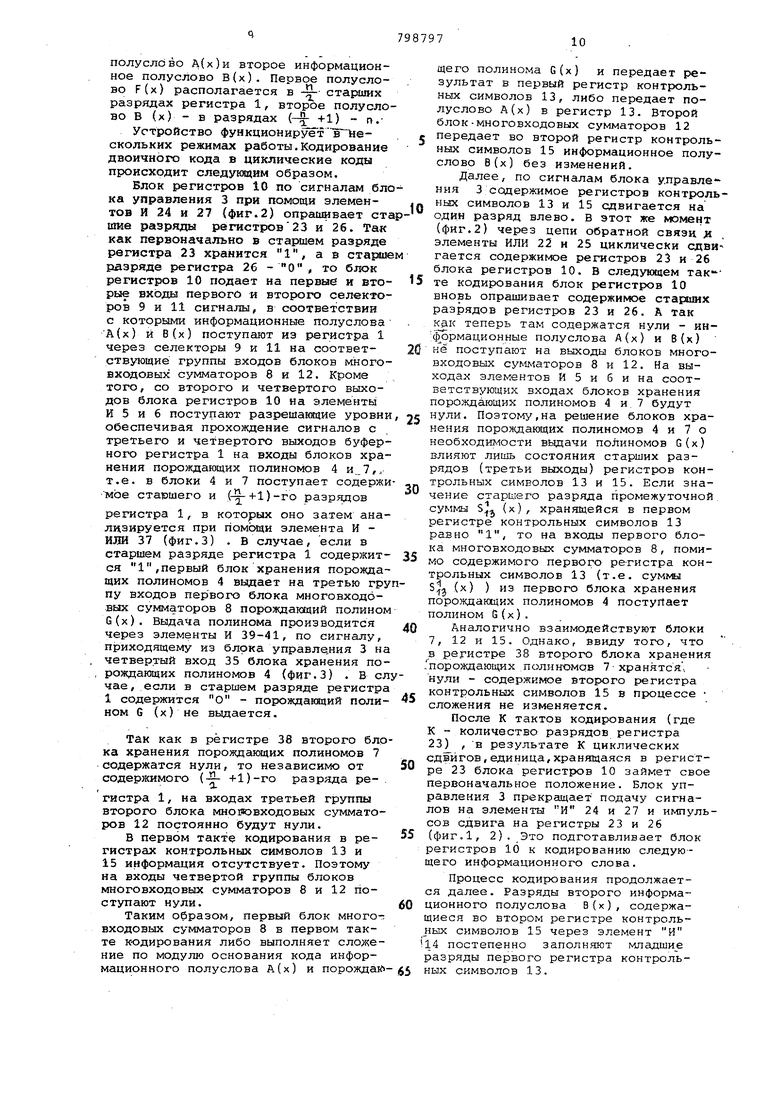

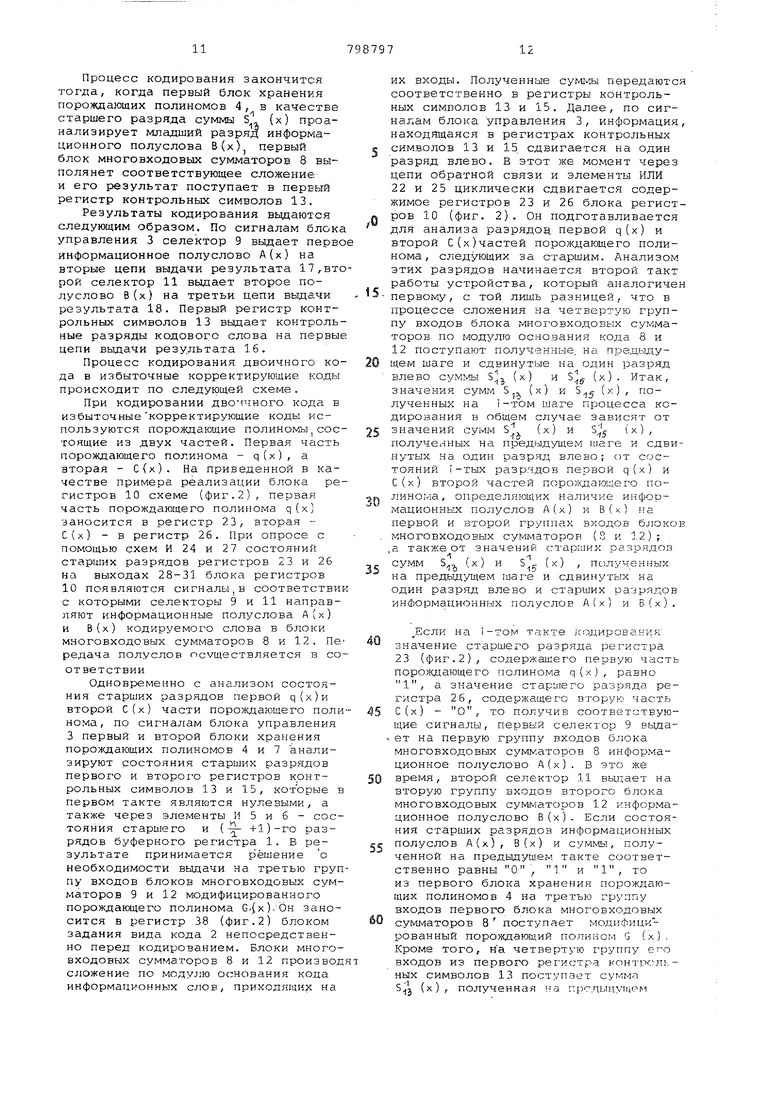

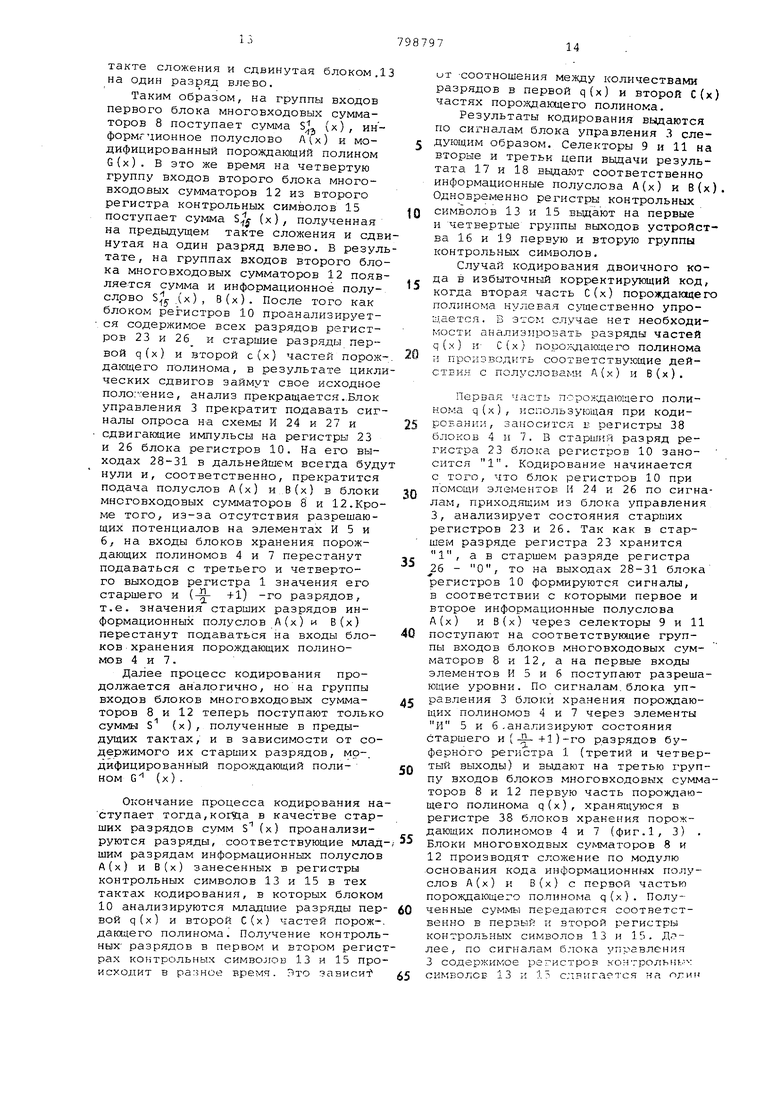

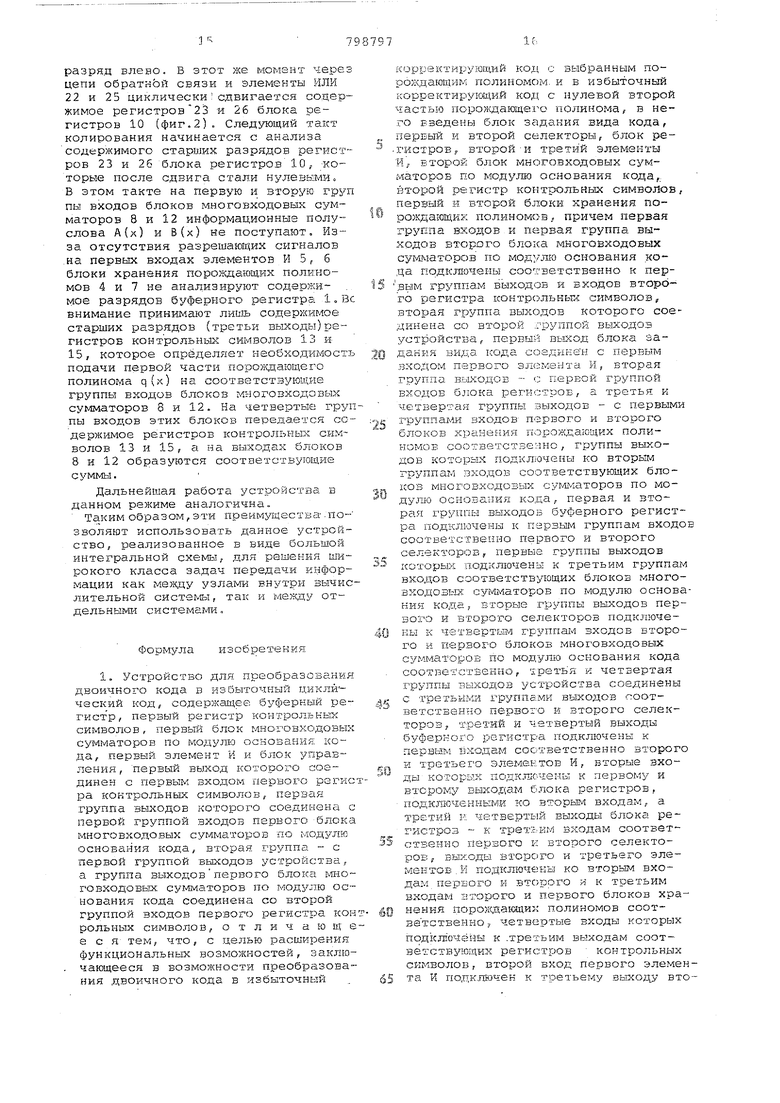

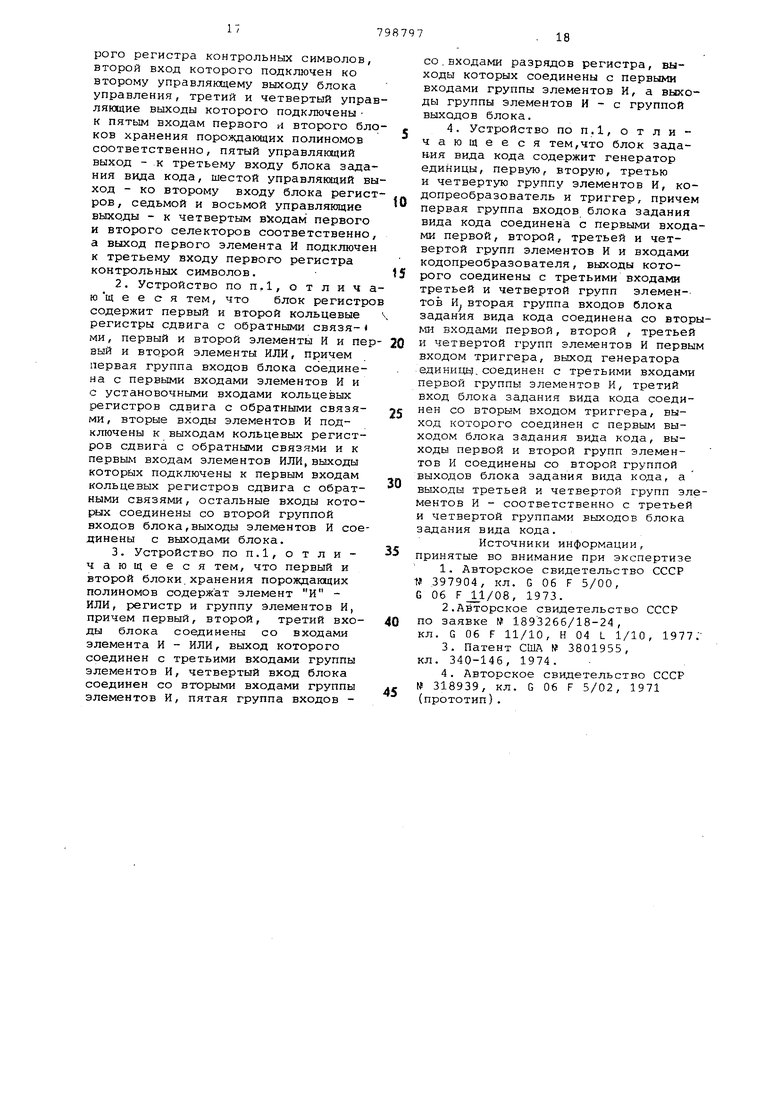

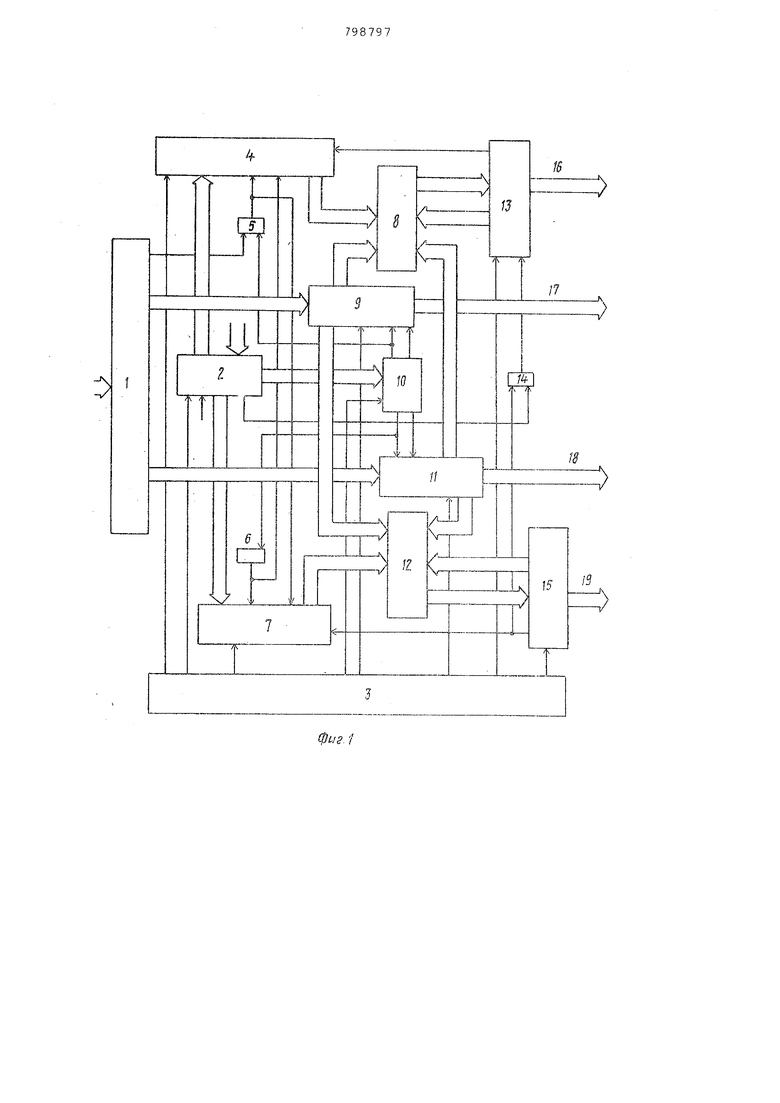

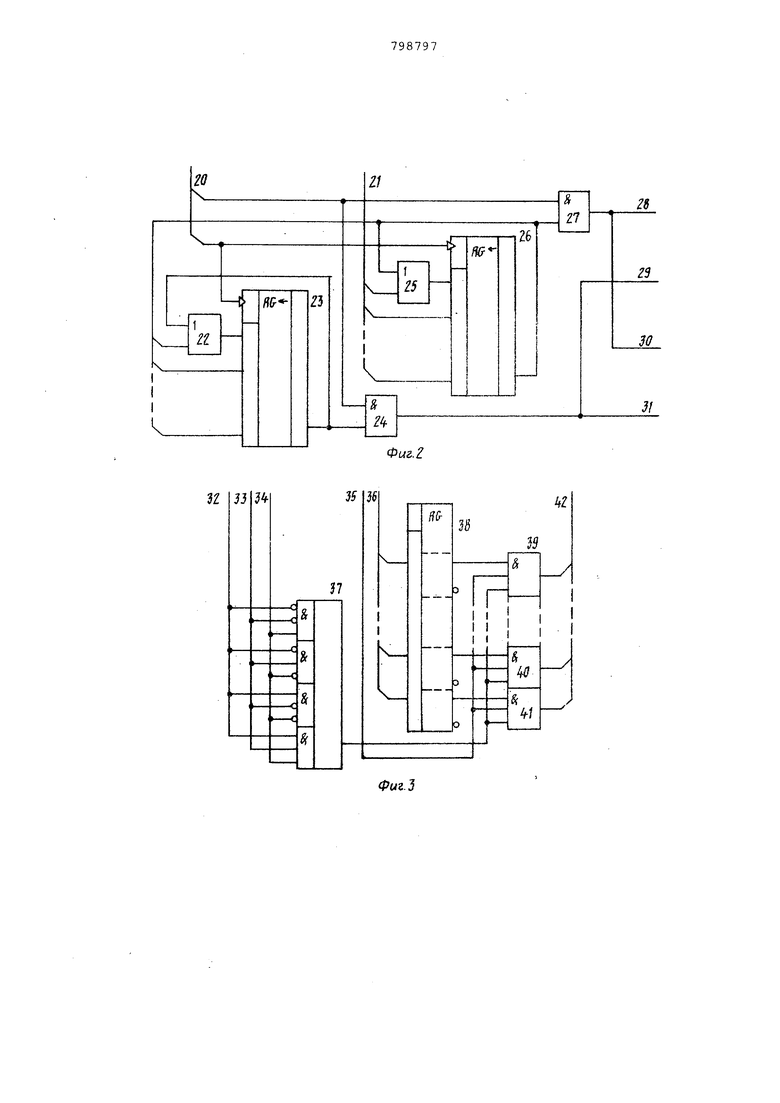

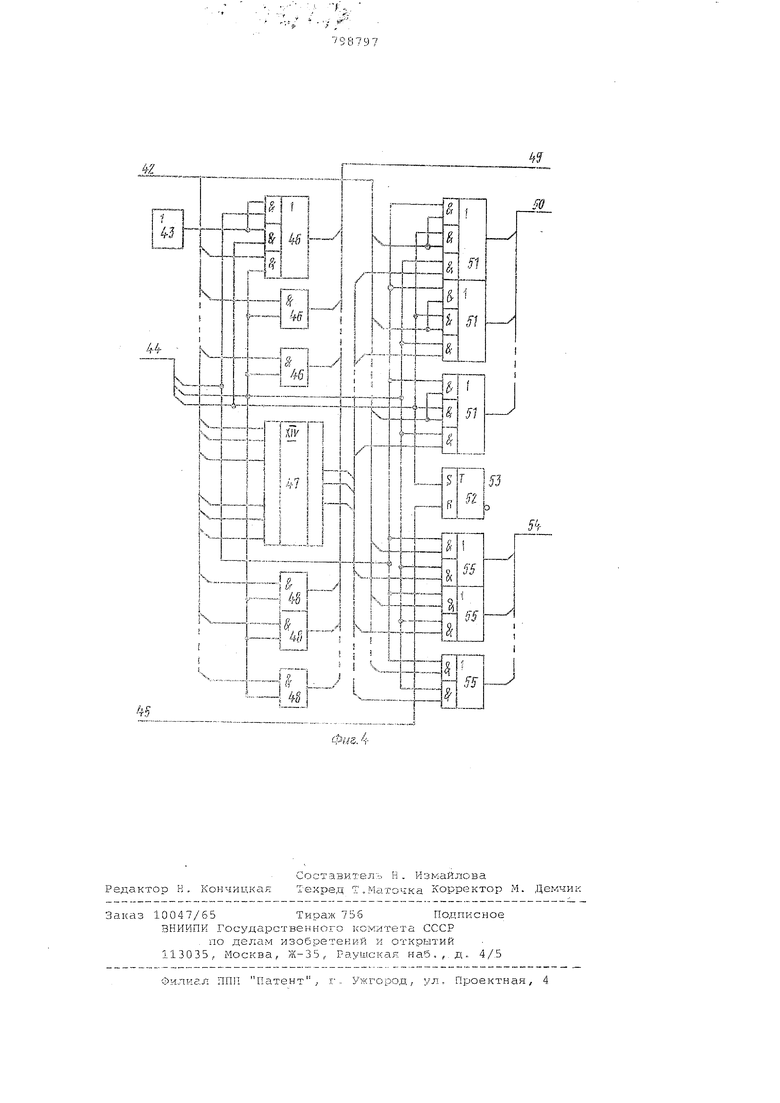

Целью изобретения является расширение функциональных возможностей устройства, заключающееся в возможности преобразования двоичного кода в избыточный корректирующий код с выбранным порождаквдим полиномог и в избыточный корректирующий код с нулевой второй частью порождающего поликома. Поставленная цель достигается тем, что устройство для преобразования двоичного кода в избыточный циклический код, содержащее буферный регистр,.первый - регистр контроль ных символов, первый блок многовходовых cyiviMaTopoB по модулю основания кода, первый элемент И и блок управления, первый выход которого соединен с первым входом первого ре гистра контрольных символов,первая группа выходов которого соединена с первой группой входов первого блока многовходовых cyiviMaTopOB по модулю основания кода, вторая группа - с первой группой выходов устройства, а группа выходов первого блока многовходовых сумматоров по модулю основания кода соединена со второй группой входов первого регистра кон рольных символов введены блок за-, Дания вида кода, первый и второй се лекторы, блок регистров, второй и третий элементы И, второй блок многовходовых сумматоров по модулю основания кода, второй регистр контрольных символов, первыйи второй блоки хранения порождающих полиномов, причем первая группа входов и первая группа выходов второго блока многовходовых сумматоров по модулю основания кода подключены соответственно к первым группам выходов и входов второго регистра контрольных символов, вторая группа выходов которого соединена со второй группой выходов устройства , .первый выход бло задания вида кода соединен с первым входом первого элемента И, вторая группа выходов - с первой группой входов блока регистров, а третья и четвертая группы выходов - с первым группами входов первого и второго блоков хранения порождающих полиномов соответственно, группы выходов которых подключены ко вторым группа входов соответствующих блоков много входовых сумматоров по модулю основания кода, первая и вторая группы выходов буферного регистра подключены к первым группам входов соответственно первого и второго селекторов , первые группы выходов которы подключены к третьим группам входов соответствующих блоков многовходовы сумматоров по модулю основания кода вторые группы выходов первого и вто рого селекторов подключены к четвер тым группам входов второго и первог блоков многовходовых сумматоров по модулю основания кода соответственн третья и четвертая группы выходов устройства соединены с третьими группами ВЕЛходов соответственно первого и второго селекторов, третий и четвертый вьшоды буферного регистра подключены к первым входам соответственно второго и третьего элементов И, вторые входы которых подключены к первому и второму выходам блока регистров, подключенными ко вторым входам, а третий и четвертый выходы блока регистров - к третьим входам соответственно первого и второго селекторов, выходы второго и третьего элементов И подключены ко вторым входам первого и второго и третьим входам второго и первого блоков хранения порождающих полиномов соответственно, четвертые входы которьж подключены к третьим выходам соответстгзующих регистров контрольных символоз, второй вход первого элемента 1-1 подключен к треть -ему выходу второго регистра контрольных символов, второй вход которого подключен со второму управляющему выходу блока управления, третий и четвертый управляю1цие выходы которого подключены к пятым входам первого и второго блоков хра1- ения порождающих полиномов соотзетстзенно, пятый управляющий выход - к третьему входу блока задания вида кода, шестой управляющий выход - ко второму входу блока регистров , седьмой к восьмой управляющие выходы - к четвертым входам первого и второго селекторов соответственно,- а выход первого элемента И подключен к третьему входу первого регистра контрольных символов, а также тем, что блок регистров содержит первый и второй кольцевые регистры сдвига с обратными связями, первый и второй элементы И к первый к второй элементы ИЛИ, причем первая группа входов блока соединена с первыми входами элементов И и с установочныг.-1и входаг-да кольцевых регистров сдвига с обратными связями, вторые Ез:оды элементов И подключены к выходам кольцевых регистров сдвига с обратными связями и к первым входам элементов ИЛИ, выходы которых подключены к первым входам кольцевых регистров сдвига с обратными связями, остальные входы которых соединены со второй группой входов блока, выходы элементов И соединены с выходами блокаJ первый и второй блоки хранения поролодающих полиномов содержат элемент И - ИЛИ, регистр и группу элементов И, причем первый, второй и третий входы блока соединены со вxoдa ш элемента И ИЛИ,выход которого соединено т-ретьими входаг/ш группы элементов И, четвертый вход блока соединен со вторыми входаг и группы элементов И( пятая группа входов - со входами разрядов регистра, выходы которых соединены с первыми входами группы элементов И, а выходы группы элементов И - с группой выходов блока; блок задания вида кода содержит генератор . единицы, первую, вторук, третью и группы элементов И, кодопреобразователь и триггер, причем первая группа входов блока задания вида кода соединена с первыми входами первой, второй, третьей и четвертой групп элементов И и входами кодопреобразователя, выходы которог соединены с третьими входами третье и четвертой групп элементов И, вторая группа входов блока задания вида кода соединена со вторыми- входами первой, второй, третьей и четвертой групп элементов И и первым входом триггера, выход генератора единицы соединен с третьими входами первой группы элементов И, третий вход блока задания вида кода соедин со вторым входом триггера, выход которого соединен с первым выходом блока задания вида кода, выходы пер вой и второй групп элементов И соед нены со второй группой выходов блок задания вида кода, а выходы третьей и четвертой групп элементов И - соо ветственно с третьей и четвертой группами выходов блока задания вида .кода. На фиг.1 приведена блок-схема ус ройства; на фиг.2 - вариант построе ния блока регистров 10; на фиг.З то же, блоков хранения порождающих полиномов 4 и 7; на фиг.4 - вариант построения блока задания вида кода 2. Блок 10 регистров включает (фиг.2) первую и вторую группу входов блока регистров 20 и 21, элемен ИЛИ 22 и 25, регистры 23 и 26, элементы И 24 и 27, первый, второй, тре тий и четвертый входы блока регистров 28-31, Блок хранения порожда ацих полино мов 4 и 7 (фиг.З) содержит первыйчетвертый входы блока хранения порож дающих полиномов 32-35, пятую группу входов блока хранения порождающих по линомов 36, элемент И-ИЛИ 37, регист 38, элементы И 39-41, группу выходов блока хранения порождающих полиномов 42.i Блок задания вида кода (фиг. 4) состоит из первой группы выходов блока за дания вида кода 42,генератор единицы 43,второй группы входов блока задания вида кода 44, третьего входа блока задания вида кода 45, первой группы элементов И 46, кода преобразователя 47, второй группы элементов И 48 второй группы вЕлходов блока задания вида кода 49, третьей группы выходов блока задания вида кода 50, третьей группы элементов И 51, триггера 52, первого выхода блока задания вида кода 53, четвертой группы выходов блока задания вида кода 54 и четвертой группы элементов И 55. Блок задания вида кода 2 служит для выбора одного из возможных режимов работы устройства. Он содержит генератор единицы 43, первую, вторую, третью и четвертую группы элементов И 46, 48, 51 и 55, кодопреобразователь 47 и триггер 52 (фиг.4). Первая группа входов 42 блока задания вида кода 2 соединена с первыми входами первой, второй, третьей и четвертой групп элементов И 46, 48, 51 и 55 и входами кодопреобразователя 47, выходы которого соединены с третьим; Ехолам третьей и четвертой групп эламгнтсхз Н 51 и 55. Вторая группа sxc.-jos 44 блока 2 соединена со втo:oь. входаг.с первой, второй, третьей к четвартой групп элементов И 46, -ч 8 , 55 и 55 и первым входом тр;{; т ра 52. Выход генератора единицы 43 соединен с третм1.ми зходами первой группы элсма;-лов И 46. Третий вход 45 блока задси 1я вида кеда 2 соединен со вторым входом триггера 52, выход которого соединен с первым выходом блока 53. Выходы первой и второй групп э;земенгов И 46 и 48 соединены со второй группой выходов 49, а выходы 7гретьей и четвертой групп элементов И 51 и 55, соответственно, с третьей и четвертой группами выходов 50 и 54 блока задания вида кода 2. Блоки хранения порож,цающих полиномов 4 и 7 служат для хранения в процессе кодирования порождающих полиномов к выдачи их на соответствующие группы входов блоков многовходовых сумматоров по модулю основания кода 8 и 12 в соответствии с видом кода, используе1 ым в данный момент, а также состоянием старших разрядов (третьи выходы) регистров контрольных символов 13 и 15 и в соответствии с сигналами на выходах элементов И 5 и 6. Блоки содержат (фиг.З) элемент Н - ИЛИ 37, регистр 38 к группу элементов И 39, 40 и 41. Первый, второй и третий входы блока 32, 33 и 34 соединены со входами элементов И - ИЛИ 37, выход которого соединен с третьими входами элементов И 39, 40 и 41. Четвертый вход 35 блока соединен со вторыми входами элементов И 39, 40 и 41. Пятая группа входов 36 соединена со входами разрядов регистра 38, выходы которых соединены с первыми входами элe eктoз И 39, 40 и 41 - с группой выходов 42 блока.

его третьего и четвертого выходов на входы блоков хранения порождающих полиномов 4 и 7.

Блоки многовходовых сумглаторов по модулю основания кода 8 и 12 суммиру ют по модулю основания кода информацию, поступающую на их входы. Селектры 9 и 11 управляют передачей информации, поступающей из буферного регистра 1 в блоки многовходовых сумматоров по модулю основания кода 8 и 12 и на третьи и четвертые группы выходов устройства.

Блок р егистров 10 служит для хранения и поразрядного анализа порождающих полиномов, которые заносятся в него блоком задания вида кода 2 при выборе режима работы устройства. Он содержит (фиг.2) кольцевые регистры сдвига с обратными связями 23 и 26, содержаи: ;ми элементы ИЛИ 22 и 25 и элементы И 24 -и 27. Первая группа входов 20 блока, соединена с первыми входами элементов И 24 и 27, вторая группа входов 21 - со входами регистров 23 и 26,, в Аходы саарших разрядов которых соединены со вторыми входами элементов И 24 и 27, а выходы элементов И 24 и 27 - с выходами блока 28, 29, 30 и 31.

Регистры контрольных символов 13 и 15 предназначены для хранения к сдвигов промежуточных результатов в процессе формирования контрольных символов.

Элемент И 14 служит для разрешения передачи информации с выхода сташего разряда (третий выход) второго регистра контрольных символов 15 на вход младшего разряда (третий вход) первого регистра контрольных символов 13 при кодировании информации в циклические коды.

Устройство (фиг.1) работает следующим образом.На входы блока задания вида кода 2 поступает информация, задающая один из возможных режимов работы устройства кодирование двоичного кода в циклический код с выбранным поролодающим полиномом или кодирование двоичного кода в избыточный корректирующий код с выбранным порождающим полиномом.

При этом, на первую группу входов 42 блока задания вида кода 2 (фиг,4) подается порождающий полином, которы будет использован при кодировании,а на вторую группу входов 44 - признак выбранного кода (циклического, избыточного корректирующего или избыточного корректирующего с нулевой второй частью порождающего полинома).

В соответствии с выбранным способом кодирования и конкретным порожда ющим полиномом блок задания вида кода 2 определяет режимы работы блока рб;гистров 10 и блоков хранения по. рождакхцих полиномов 4 и 7. Так, для рассмотренных вариантов построения

этих блоков (фиг.2, 3, 4J при кодировании в г,иклические коды единичный генератор 43 блока 2 формирует единицу, которая, -проходя через первую группу элементов И 46, поступает на вторую группу выходов 49 блока задания вида кода 2, а оттуда в старший разряд регистра 23 блока регистров 10 через вторую группу входов 20. В регистр 38 первого блока хранения порождающих полиномов 4 с первой группы входов 42 блока 2 (фиг. 4) через третью группу элементов И 51, третью группу выходов блока 2 и пятую группу входов 36 блока 4 (фиг.З) поступает порождающий полином G (у.) выбранного циклического кода. Кроме того, на первый вход элемента И 14 с выхода триггера 52 блока 2 подается разрешарощий потенциал, обеспечивая последовательное включение регистров к-онтрольных символов 13 и 15 путем соединеЕ1Ия через элемент И 14 третьего выхода (выхода старшего разряда регистров 15 с третьим входом (входом младшего разряда) регистра 13.

При кодировании в избыточные коррект-ирующие коды в регистр 23 блока рег.чстров 10 (фиг.1, 2) поступает первая часть q (х), а в регистр 26 - вторая часть С (х) выбранного порождающего полинома. Они передаются туда с первой группы входов 42 блока 2 через первую и вторую группы элементов И 46- и 48. В регистры 38 первого и второго блоков хранения порождающих полиномов 4 и 7 через пятые группы входов 36 блок задания вида кода 2 заносит модифицированный порождающий полином С (х) , который представляет собой сумму квадратов первой и второй частей порождающего полинома. Он формируется кодопреобразователем 47 (фиг.4) и проходит на третью и четвертую группы выходов 50 и 54 блока задания вида кода 2 через третью и четвертую группы элементов И 51 и 55.

При использовании избыточных ко-рректир л-ощих кодов, у которых вторая часть С (х) п-орождающего полинома нулевая, в старший разряд регистра 23 блока регистров 10 (фиг.2) заносится единица, которая формируется генератором 43 (фиг.4). В регистры 38 блоков хранения порождающих полиномов 4 и 7 блок задания вида кода 2 заносит первую часть q (х)выбранного -порожающего полинома. Она передается на третью и четвертую группы выходов 50 и 54 блока 2 через третью и четвертую группы элементов И 51 и 55 с первой группы входов 4 2.

Кодируемое . п - разрядное с.кз.во (фиг,1) располагается в буферном ре гистре 1. Оно подразделяется на две части: т.е. на первое инфопмаиисжное полуслсзво А(х)и второе информационное полуслово В(х). Первое полуслово F(x) располагается в старших разрядах регистра 1, второе полусло во В (х) - в разрядах (- +1) - п.Устройство функционирует в ескольких режимах работы.Кодирование двоичного кода в циклические коды происходит следующим образом. Блок регистров 10 по сигналам бло ка управления 3 при помощи элементов К 24 к 27 (фиг.2) опрашивает ст шие разряды регистров23 и 26. Так как первоначально в старшем разряде регистра 23 хранится 1, а в старяае разряде регистра 26 - О, то блок регистров 10 подает на первые и вторые входы первого и второго селекгоров 9 и 11 сигналы, в соответствий с которыми информационные полуслова А{х) и В(х) поступают из регистра 1 через селекторы 9 и 11 на соответствующие группы входов блоков многовходовых сумматоров 8 и 12. Кроме того, со второго и четвертого выходов блока регистров 10 на элементы И 5 и 6 поступают разрешанвдие уровни обеспечивая прохождение сигналов с третьего и четвертого выходов буферного регистра 1 на входы блоков хранения порождающих полиномов 4 и 7,л т.е. в блоки 4 и 7 поступает содержи мЬе ставшего и ()-го разрядов регистра 1, в которых оно затем анализируется при помощи элемента И ИЛИ 37 (фиг.З) . В случае, если в старшем разряде регистра 1 содержится 1,первый блок хранения порождащих полиномов 4 вьщает на третью гру пу входов первого блока многовходбвых сумматоров 8 порождакхций полином G(x). Выдача полинома производится через элементы И 39-41, по сигналу, приходящему из блока управле,ния 3 на четвертый вход 35 блока хранения порождающих полиномов 4 (фиг.З) . В сл чае, если в старшем разряде регистра 1 содержится О - порождаквдий полином G (х) не выдается. так как в регистре 38 второго бло ка хранения порождсшедих полиномов 7 содержатся нули, то независимо от содержимого (- +1)-го разряда регистра 1, на входах третьей группы второго блока МНО1ЯЭВХОДОВЫХ сумматоров 12 постоянно будут нули. В первом такт кодирования в регистрах контрольных символов 13 и 15 информация отсутствует. Поэтому на входы четвертой группы блоков многовходовых сумматоров 8 и 12 поступают нули. Таким образом, первый блок многовходовых сумматоров 8 в первом такте кодирования либо выполняет сложение по модулю основания кода информационного полуслова А(Х) и порожда1й щего полинома G{x) и передает результат в первый регистр контрольных символов 13, либо передает полуслово А(х) в регистр 13. Второй блок-многовходовых сумматоров 12 передает во второй регистр контрольных символов 15 информационное полуслово В(х) без изменений. Далее, по сигналам блока управления 3 содержимое регистров контрольных символов 13 и 15 сдвигается на один разряд влево. В этот же момент (фиг.2) через цепи обратной связи л элементы ИЛИ 22 и 25 циклически сдвигается содержимое регистров 23 и 26 блока регистров 10. В следующем так-те кодирования блок регистров 10 вновь опрашивает содержимое старошх разрядов регистров 23 и 26. А так кдк теперь там содержатся нули - инДормационные полуслова А(х) и В{х) не поступают на выходы блоков многовходовых сукчматоров 8 и 12. На выходах элементов И 5 и 6 и на соответствующих входах блоков хранения порождающих полиномов 4 и.7 будут нули. Поэтому,на решение блоков хранения порождающих полиномов 4 и 7 о необходимости выдачи полиномов G(x) влияют лишь состояния старших разрядов (третьи выходы) регистров контрольных символов 13 и 15. Бели значение cTapaiero разряда промежуточной, суммы S (х), хранящейся в первом регистре контрольных символов 13 равно 1, то на входы первого блока многовходовых сумматоров 8, помимо содержимого первого ре-гистра контрольных символов 13 (т.е. сумки (х) ) из первого блока хранения порожданхцих полиномов 4 поступает полином G(х) . Аналогично взаимодействуют блоки 7, 12 и 15. Однако, ввиду того, что в регистре 38 второго блока хранения порождающих .полиномов 7-хранятся, нули - содержимое второго регистра контрольных символов 15 в процессе сложения не изменяется. После К тактов кодирования (где К - количество разрядов регистра 23) , В результате К циклических сдвигов,единица,хранящаяся в регистре 23 блока регистров 10 займет свое первоначальное положение. Блок управления 3 прекращает подачу сигналов на элементы И 24 и 27 и импульсов сдвига на регистры 23 и 26 (фиг,1, 2). Это подготавливает блок регистров 10 к кодированию следующего информационного слова. Процесс кодирования продолжается далее. Разряды второго информационного полуслова В(х), содержащиеся во втором регистре контрольных символов 15 через элемент И 14 постепенно заполняют младши е разряды первого регистра контрольных символов 13. Процесс кодирования закончится тогда, когда первый блок хранения порождающих полиномов 4, в качестве старшего разряда суммы (х) проанализирует младший разряд информационного полуслова В(х), первый блок многоБходовых сумматоров 8 выполянет соответствующее сложение и его результат поступает в нервный регистр контрольных символов 13. Результаты кодирования выдаются следующим образом. По сигналам блок управления 3 селектор 9 выдает перв информационное полуслово А(х) на вторые цепи выдачи результата 17,вт рой селектор 11 выдает второе полуслово В(х) на третьи цепи выдачи результата 18. Первый регистр контрольных символов 13 выдает контроль ные разряды кодового слова на первы цепи выдачи результата 16. Процесс кодирования двоичного ко да в избыточные корректирующие коды происходит по следукрщей схеме. При кодировании двоччиого кода в избыточныекорректирующие коды используются порождающие полиномы сос тоящие из двух частей. Первая чешть порождающего полинома - q(x), а вторая - С{х). На приведенной в качестве примера реализации блока ре гистров 10 схеме (фиг. 2), первая часть порождающего полинома q(x) заносится в регистр 23, вторая -С(х) - в регистр 26. При опросе с помощью схем И 24 и 27 состояний старших разрядов регистров 23 и 26 на выходах 28-31 блока регистров 10 появляются сигналы I в соответстви с которыми селекторы 9 и 11 направляют информационные полуслова А(х) и В(х) кодируемого слова в блоки многовходовых сумматоров 8 и 12, Пе редача полуслов осуществляется в со ответствии Одновременно с анализом состояния старших разрядов первой р(х)и второй С(х) части порождающего пол нома, по сигналам блока управления 3 первый и второй блоки хранения порождающих полиномов 4 и 7 анализируют состояния старших разрядов первого и второго регистров контрольных символов 13 и 15, которые первом такте являются нулевыми, а также через элементы И 5 и б - сос тояния старшего и (- +1)-го разрядов буферного регистра 1. В результате принимается решение о необходимости выдачи на третью гру пу входов блоков многовходовых сум маторов 9 и 12 модифицированного порождающего полинома С.{х).0н зано сится в регистр 38 (фиг.2) блоком задания вида кода 2 непосредственно перед кодированием. Блоки много входовых сумматоров 8 и 12 произво сложение по моду;;ю основания кода информационных слов, приходящих на их входы. Полученные cyMjviH передаются соответственно в регистры контрольных символов 13 и 15. Далее, по сигналам блока управления 3, информация, находящаяся в регистрах контрольных символов 13 и 15 сдвигается на один разряд влево, В этот же момент через цепи обратной связи и элементы ИЛИ 22 и 25 циклически сдвигается содержимое регистров 23 и 26 блока регистров 10 (фиг. 2). Он подготавливается для анализа разрядоц первой q(x) и второй С(х)частей порождающего полинома, следующих за старшим. Анализом этих разрядов начинается второй такт работы устройства, который аналогичен первому, с той лишь разницей, что в процессе сложения на четвертую группу входов блока многовходовых сумматоров по модулю основания кода 8 и 12 поступают полученные, на предыдущем шаге и сдвинутые на один разряд (х ) . Итак , влево суммы S, (х) значения сум1А S . (х) и S (х) , получекных на I-TOM шаге процесса кодирования в общем случае зависят от значений сумм S. (х) и S (х), полученных на предыдущем шаге и сдвинутых на один разряд влево; от состояний i-тых разрядов первой q(x) и С(х) второй частей порождающего полинома, определяющих наличие и формационных полуслов А(х) к В(х) ь;а первой и второй группах входов блоков многовходовых сумматоров (S и 12); ,а также от значений старших разрядов сумм S (х) и S (х) , полученных на предьщущем шаге и сдвинутых на один разряд влево и старших разрядов информационных полуслов Alx) и Б(х}. Если на i-TOM такте 1;одированик значение старшего разряда регистра 23 (фиг.2), содержащего первую часть порождающего полинома q(x), равно 1, а значение старшего разряда регистра 26, содержащего вторую част.ь С(х) - О, то получив соответствующие сигналы, первый селектор 9 выдает на первую группу входов блока многовходовых сумматоров В информационное полуслово А(х). В это же время, второй селектор 11 выдает на вторую группу входов второго блока многовходовых сумимэ.торов 12 информационное полуслово В(х). Если состояния старших разрядов информационных полуслов А(х), S(х) и суммы, полученной на предьщущ.ем такте соответственно равны О , 1 и 1, то из первого блока хранения порождающих полиномов 4 на третью группу входов первого блока многовходовр х сумматоров 8 поступает модиФици рованный порождающий полином G (х). Кроме того, на четвертую группу входов из первого регистра контр :;льных символов 13 поступает (х), полученная пpcлыцyII e 1

такте сложения и сдвинутая блоком.1 на один разряд влево.

Таким образом, на группы входов первого блока многовходовых сумматоров 8 поступает сумма (х), информгдионное полуслово Л(х) и модифицированный порождающий полином G{x). В это же время на четвертую группу входов второго блока многовходовых сумматоров 12 из второго регистра контрольных символов 15 поступает сумма (х), полученная на предыдущем такте сложения и сдвинутая на один разряд влево. В результате, на группах входов второго блока многовходовых сумматоров 12 появляется сумма и информационное полуслово S:fy (х), В(х). После того как блоком регистров 10 проанализируется содержимое всех разрядов регистров 23 и 26 и старшие разряды первой q(x) и второй с(х) частей порождающего полинома, в результате циклических сдвигов займут свое исходное поло.--ение, анализ прекращается ..Блок управления 3 прекратит подавать сигналы опроса на схемы И24и27и сдвигающие импульсы на регистры 23 и 26 блока регистров 10. На его выходах 28-31 в дальнейшем всегда буду нули и, соответственно, прекратится подача полуслов А(х) и В(х) в блоки многовходовых сумматоров 8 и 12.Кроме того, из-за отсутствия разрешающих потенциалов на элементах И 5 и 6 на входы блоков хранения порождающих полиномов 4 и 7 перестанут подаваться с третьего и четвертого выходов регистра 1 значения его старшего и (- +1) -го разрядов, т.е. значения старших разрядов информационных полуслов А(х) и В(х) перестанут подаваться на входы блоков хранения порождающих полиномов 4 и 7.

Далее процесс кодирования продолжается аналогично, но на группы входов блоков многовходовых сумматоров 8 к 1.2 теперь поступают только суммы S (х), полученные в предыдущих тактах, и в зависимости от содержимого их старших разрядов, мр-. дифицированный порождающий полином G (х) .

Окончание процесса кодирования наступает тогда,ког5ца в качестве старших разрядов сумм S (х) проанализируются разряды, соответствующие млад шим разрядам информационных полуслов А(х) и В(х) занесенных в регистры контрольных символов 13 и 15 в тех тактах кодирования, в которых блоком 10 анализируются младшие разряды пер вой q{x) и второй С(х) частей порождаквдего полинома. Получение контрольных- разрядов в первом и втором регисрах контрольных символов 13 и 15 происходит Б разное время. Это зависит

их -соотношения между количествами разрядов в первой q(x) и второй С(х частях порожл,ающего полинома.

Результаты кодирования выдаются по сигналам блока управления 3 следующим образом. Селекторы 9 и 11 на вторые и третьи цепи выдачи результата 17 и 18 выдают соответственно информационные полуслова А(х) и В{х Одновременно регистры контрольных символов 13 и 15 вьщают на первые и четвертые группы выходов устройства 16 и 19 первую и вторяо группы контрольных символов.

Случай кодирования двоичного кода в избыточный корректирующий код, когда вторая часть С(х) порождающег полинома нулевая существенно упрощается. Б за-о. случае нет необходимости аналиэнрозать разряды частей q(x) и С{х) порощ1аюа1его полинома и произволнть соответствующие действия с полусловами А(х) и В(х).

Первая часть поро; щаю1цего полинома q(x), использующая при кодирСЕании, заносится Е регистры 38 блоков 4 и 7. В старо:нй разряд регистра 23 блока регистров 10 заносится 1. Кодирование начинается с того, что блок регистров 10 при помощи элементов И 24 и 26 по сигналам, приходящим из блока управления 3, анализирует состояния старших регистров 23 и 26. Так как в старшем разряде регистра 23 хранится 1, а в старшем разряде регистра 26 - О, то на выходах 28-31 блока регистров 10 формируются сигналы, в соответствии с которыми первое и второе информационные полуслова А(х) и В{х) через селекторы 9 и 11 поступают на соответствуквдие группы входов блоков многовходовых сумматоров 8 и 12, а на первые входы элементов И 5 и 6 поступают разрешающие уровни. По сигналам.блока управления 3 блоки хранения порождающих полиномов 4 и 7 через элементы И 5 и 6 -анализируют состояния старшего н()-го разрядов буферного регистра 1 (третий и четвертый выходы) и выдают на третью группу входов блоков многовходовых сумматоров 8 и 12 первую часть порождающего полинома q(x), хранящуюся в регистре 38 блоков хранения порождающих полиномов 4 и 7 (фиг.1, 3) . Блоки МНСговходвых сумматоров 8 и 12 производят сложение по модулю основания кода информационных полуслов А(х) и В(х) с первой частью порождающего полинома q{x). Полученные суммы передаются соответственно в первый и второй регистры контрольных символов 13 и 1Г. , по сигналам б:юка управления 3 содержимое регистров контрольш.-у символов 13 и 13 слвагается на олии

разряд влево. В этот же момент через цепи обратной связи и элементы ИЛИ 22 и 25 циклически:сдвигается содержимое регистров23 и 26 блока регистров 10 (фиг.2). Следующий такт колирования начинается с анализа содержимого старших разрядов регистров 23 и 26 блока регистров 10,- которые после сдвига стали нулевыми В этом такте на первую и вторую труп пы входов блоков многовходовых сумматоров 8 и 12 информационные полуслова А{х) и В(х) не поступают. Изза отсутствия разрешающих сигналов ,на первых входах элементов И 5, б блоки хранения порождающих полиномов 4 и 7 не анализируют содержимое разрядов буферного регистра 1. В внимание принимают лииш содержимое старших разрядов (третьи выходы)регистров контрольных СШЛВОЛОВ 12 и

15, которое определяет необходимост подачи первой части порождающего поликома q(x) на соответствующие группы входов блоков многозходовых сумматоров 8 и 12. На четвертые групы входов этих блоков передается ссдерж -омое регистров контрольных символов 13 и IS, а на выходах блоков 8 и 12 образуются соответствующие суммы.

Дальнейшая работа устройства в данном режиме аналогична. Таким образом, э-ти преимутцества-позволяют использовать данное устройство, реализованное в виде большой интегральной схемы,- для решения широкого класса задач передачи информации как узлаг-ш внутри вычислительной системы, так и между отдельнь М1-1 системаг та.

Формула изобретения

1. устройство для преобразования двоичного кода в избыточный циклйческий код, содержащее буферный регистр, первый регистр контрольных символов, первый блок многовходовых сумматоров по модулю основания кода, первый элемент И и блок управления, первый выход которого соединен с первым входом первого регисра контрольных символов, первая группа выходов которого соединена с первой группой входов первого блока многовходовых сумматоров по модулю основания кода,- вторая группа - с первой группой выходов устройства, а группа выходовпервого блока многовходовых сумматоров по модулю основания кола соединена со второй группой входов первого регистра конрольных символов, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей, заключающееся в возможности преобразования двоичного кода в избыточный

корректирующий код с выбранным порождающим полиномом, и в избыточный корректирукщий код с нулевой второй частью поро :дающего полинома, в него г-;звдены блок задания вида кода, перБый и второй селекторы, блок ре гистрову второйИ третий элементы и, второй блок многовходовых сумматоров по модулю основания кода, второй регистр контрольных символов, первый и второй блоки хранения порождающих полиномов, причем первая группа входов и первая группа выходов второго блока многовходовых cyiv&iaTOpOB по модулю основания кода подключены соответственно к первым группам выходов и входов второго регистра контрольньк символов вторая группа выходов которого соединена со второй группой выходоэ устройства, первый вьзход блока задания вида кода соединен с первым входном первого элемента И, вторая группа выходов - с; первой группой входов блока регистров, а третья и четверта.я группы выходов - с первыми группами входов первого и второго

5 t блоков хранения порождающих полиномов соответстве: шс , группы выходов которых подключены ко вторым группам входов соответствующих блоков многовходовых сумматоров по модулю оснозатшя кода, первая и вторая группы выходов буферного регистра подключены к первым группам входов соответственно первого и второго селекторов, первые группы выходов которых подключена к третьим группам входов соответствующих блоков многовходозьп сус-Ф.аторов по модулю основания кода, вторые группы выходов первого и второг-о селекторов подключеО кы к четвертым группам входов второго и первого блоков многовходовых сумматоров по модулю основания кода соответстБенно. третья и четвертая группы выходов устройства соединены ,jiij с третьими группеми выходов соот ветственно первого и второго селекторов , третий и четвертый выходы буферного регистра подключены к первым входам соответственно второго др, и третьего элементов И, вторые sxo ды KOTOptiK подключены к первому и второму выходам блока регистров, подключенными ко вторым входам, а третий и четвертый выходы блока регистроз - к трет:-:-им входам соответственно первого к второго селектоюоЕ. выходы второго и третьего элементов. И подключена ко вторым входам первого и второго н к третьим входам второго и первого блоков хра(1П нения порождаюадах полиномов соответственно, четвертые входы которых подкл1очёны к .третьим выходам соответствующих регистров контрольных символов, второй вход первого элеменАЭ та и подключен к третьему выходу второго регистра контрольных символов второй вход которого подключен ко второму управляющему выходу блока управления, третий и четвертый упра ляющие выходы которого подключены к пятым входам первого и второго бл ков хранения порождающих полиномов соответственно, пятый управляющий выход - к третьему входу блока зада ния вида кода, шестой управляющий в ход - ко второму входу блока регис ров , седьмой и восьмой управляющие выходы - к четвертым входам первого и второго селекторов соответственно а выход первого элемента И подключе к третьему входу первого регистра контрольных символов, 2.Устройство поп,1,отлич ю щ е е а я тем, что блок регистр содержит первый и второй кольцевые регистры сдвига с обратными связями, первый и второй элементы И и пе вый и второй элементы ИЛИ, причем первая группа входов блока соединена с первыми входами элементов И и с установочными входами кольцевых регистров сдвига с обратными связями, вторые входы элементов И подключены к выходам кольцевых регистров сдвига с обратными связями и к первым входам элементов ИЛИ,выходы которых подключены к первым входам кольцевых регистров сдвига с обратными связями, остальные входы котоptjx соединены со второй группой входов блока,выходы элементов И сое динены с выходами блока. 3.Устройство по п.1, отличающееся тем, что первый и второй блоки.хранения порождающих полиномов содержат элемент И ИЛИ, регистр и группу элементов И, причем первый, второй, третий входы блока соединены со входами элемента И - ИЛИ, выход которого соединен с третьими входами группы элементов И, четвертый вкод блока соединен со вторыми входами группы элементов И, пятая группа входов со.входами разрядов регистра, выходы которых соединены с первыми входами группы элементов И, а выходы группы элементов И - с группой выходов блока. 4. Устройство по п.1, отличающееся тем,что блок задания вида кода содержит генератор единицы, первую, вторую, третью и четвертую группу элементов И, кодопреобразователь и триггер, причем первая группа входов блока задания вида кода соединена с первыми входами первой, второй, третьей и четвертой групп элементов И и входами кодопреобразователя, выходы которого соединены с третьими входами третьей и четвертой групп элемен-тов И вторая группа входов блока задания вида кода соединена со вторыNffl входами первой, второй , третьей и четвертой групп элементов И первым входом триггера, выход генератора единиин.соединен с третьими входами первой группы элементов И, третий вход блока задания вида кода соединен со вторым входом триггера, выход которого соединен с первым выходом блока задания вида кода, выходы первой и второй групп элементов И соединены со второй группой выходов блока задания вида кода, а вЕзгходы третьей и четвертой групп элементов И - соответственно с третьей и четвертой группами выходов блока задания вида кода. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР W .397904, кл. G 06 F 5/00, G 06 , 1973. 2.Авторское свидетельство СССР по заявке № 1893266/18-24, кл. G 06 F 11/10, Н 04 L 1/10, 1977. 3.Патент США № 3801955, кл. 340-146, 1974. 4.Авторское свидетельство СССР № 318939, кл. G 06 F 5/02, 1971 (прототип).

28

26

Ib

23

3ff

31

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Устройство для кодирования линейных полиномиальных кодов | 1989 |

|

SU1711338A1 |

| Способ диагностики недвоичных блоковых кодов | 2018 |

|

RU2693190C1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| ПАРАЛЛЕЛЬНЫЙ РЕКОНФИГУРИРУЕМЫЙ КОДЕР БЧХ КОДОВ | 2015 |

|

RU2591474C1 |

| Устройство для кодирования информации циклическим кодом | 1974 |

|

SU600740A1 |

| ПАРАЛЛЕЛЬНЫЙ КОДЕР БЧХ С РЕКОНФИГУРИРУЕМОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2021 |

|

RU2777527C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В ИЗБЫТОЧНЫЙ ЦИКЛИЧЕСКИЙ КОД | 1971 |

|

SU318939A1 |

n

kl

Авторы

Даты

1981-01-23—Публикация

1978-07-05—Подача