Изобретение относится к вычиспитепь- ной технике, к специагтизированным устройствам дпя опредепения статистических характеристик случайных процессов, и предназначено дпя опрэдепения среднего гармонического значения поспедоватепь ности ограниченного чиспа временных интервалов ограниченной дпитепьности.

Известны устройства, определяющие различные виды средних значений, например, среднее арифметическое 11 .

Известно также устройство, позволяющее определять среднее гармоническое значение случайного процесса 2 . Это устройство содержит первый и второй триггеры, счетчик входных сигналов, первый и второй временные селекторы, счетчик результата, счетный вход которого подключен к выходу первого временного селектора, первый вход которого соединен с единичным выходом первого триггера, а второй вход подкгаочен к выходу генератора импульсов, единичный вход второ,го триггера подключен к входу устройст

ва и к первому входу второго временно1-ю селектора, второй вход которого соединен с единичным выходом второго триггера, а выход подключен к счетному входу счетчика входных сигналов. Устройство обладает ограниченными функциональными возможностями, оно не позволяет, в частности, определять среднее гармоническое значение интервалов импульсной последовательности.

Цель изобретения - расширение функциональных возможностей устройства.

Для этого в устройство для опредепения среднего гармонического значения случайного процесса введены дешифратор, комsпаратор, ингегратор, первый и второй элементы ИЛИ, третий временной селектор, ГТ блоков анализа интервалов импульсной пос ледовательности, элемент И, блок деления, источник опорного напряжения и

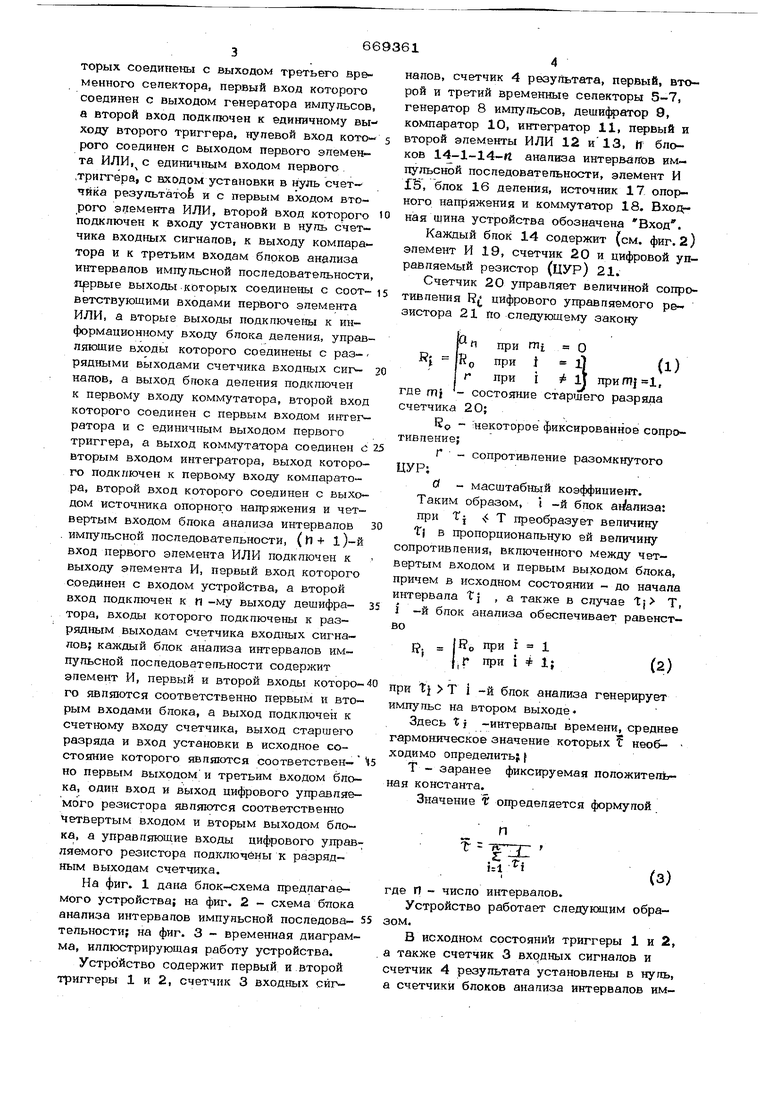

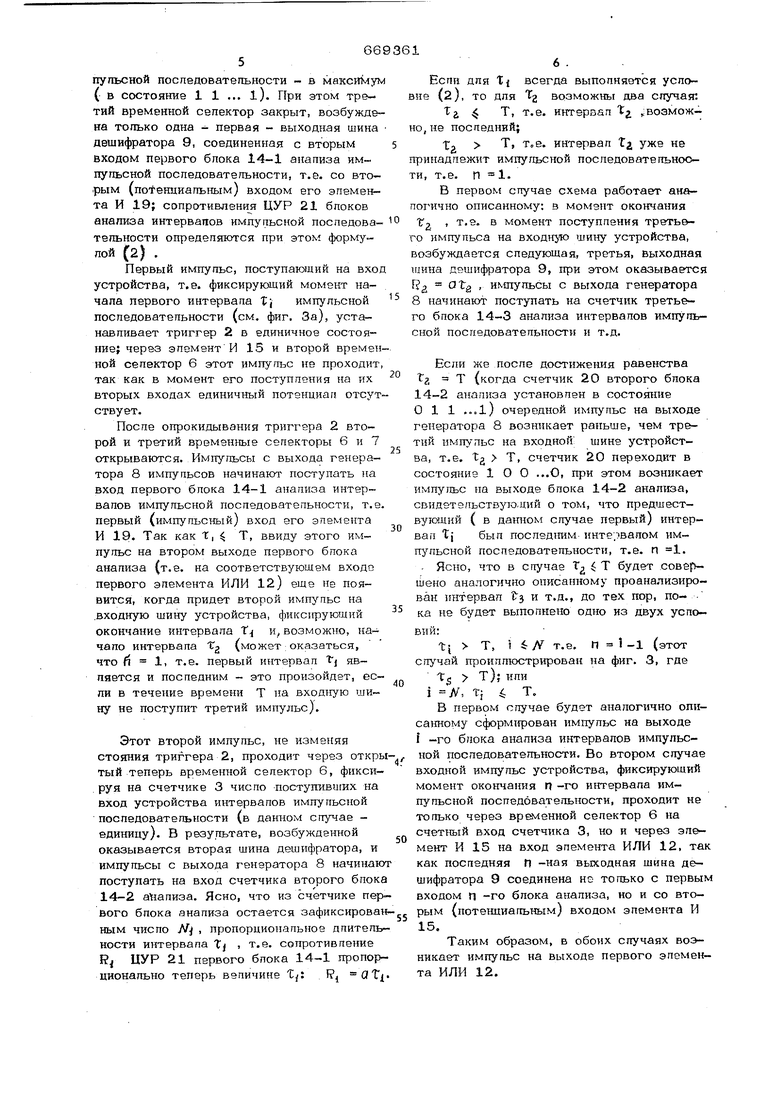

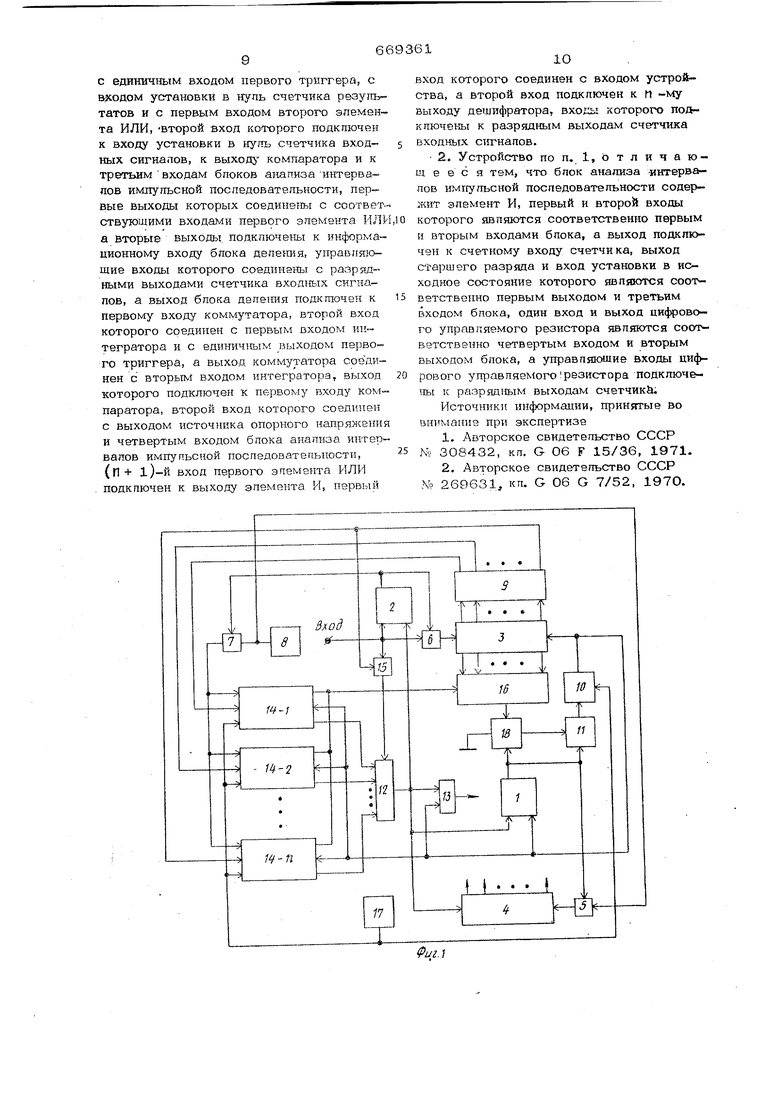

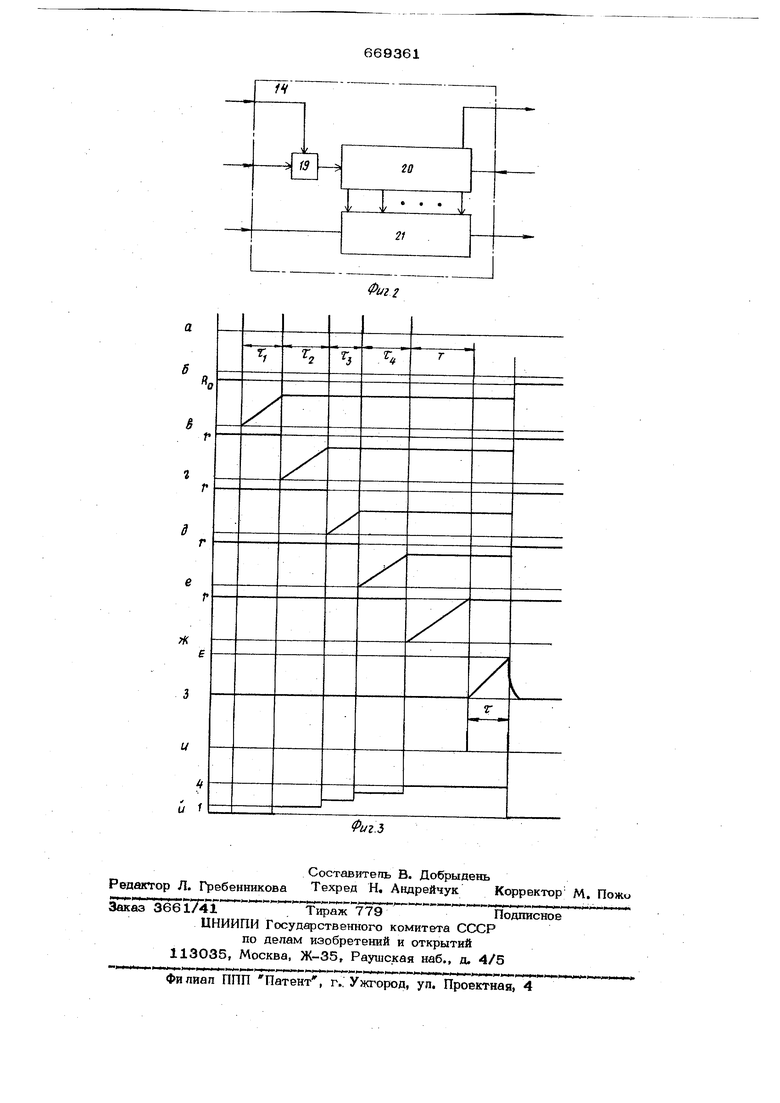

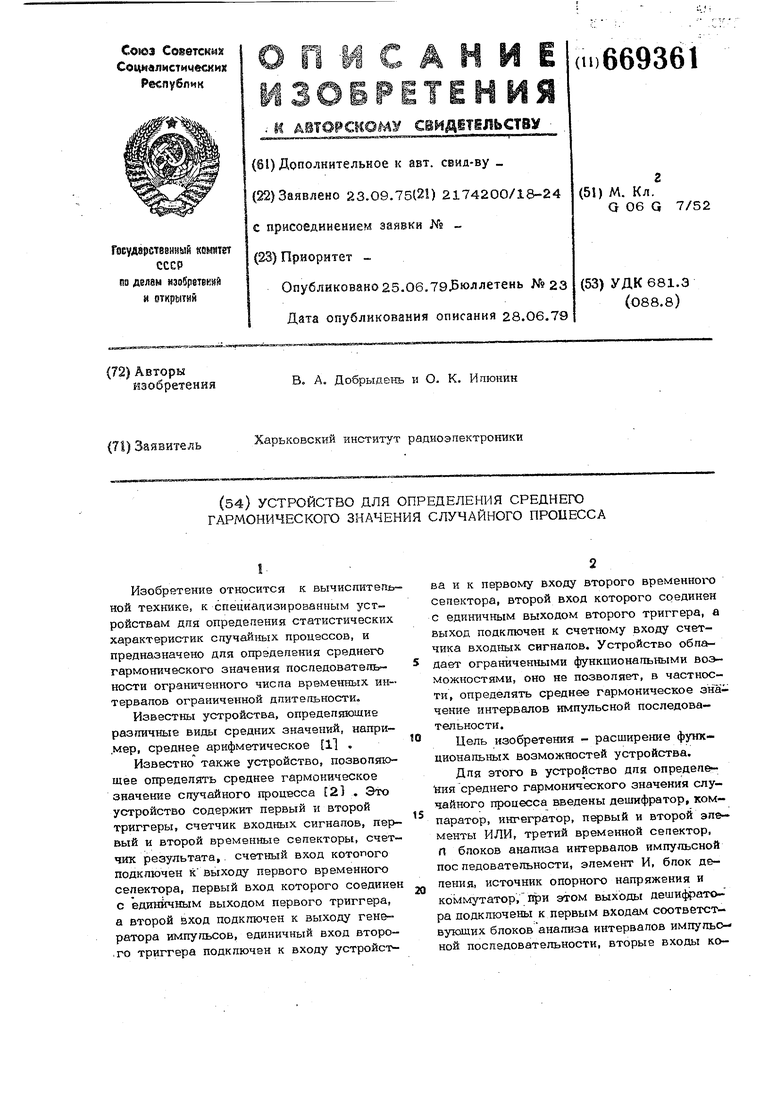

0 коммутатор,при этом выходы деши атора подключены к первым входам соответст вуюших блоков анализа интервалов импульсной последовательности, вторые входы которых соединены с выходом третьего временного селектора, первый вход которого соединен с выходом генератора импульсов, а второй вход подктпочен к единичному выходу второго триггера, нулевой вход кото- рого соединен с выходом первого эпемента ИЛИ, с единичным входом первого .триггера, с нходом установки в нуль счетчйка результатов и с первым входом второго элемента ИЛИ, второй вход которого подключен к входу установки в нуль счетчика входных сигналов, к выходу компаратора и к третьим входам блоков анализа интервалов импульсной последовательности, пррвые выходы.которых соединены с соответствуюшими входами первого элемвнта ИЛИ, а вторые выходы подключены к информационному входу блока деления, управляющие входы которого соединены с раз- рядными выходами счетчика входт ых сигналов, а выход блока деления подключен к первому входу коммутатора, второй вход которого соединен с первым входом ингег- ратора и с единичным выходом первого триггера, а выход коммутатора соединен с вторым входом интегратора, выход которого подключен к первому входу компаратора, второй вход которого соединен с выходом источника опорного напряжения и четвертым входом блока анализа интервалов импульсной последовательности, (П+ 1)-й вход первого элемента ИЛИ подключен к выходу апемента И, первый вход которого соединен с входом устройства, а второй вход подключен к и -му выходу дешифратора, входы которого подключены к разрядным выходам счетчика входных сигналов; каждый блок анализа интервалов импульсной последовательности содержит элемент И, первый и второй входы которого являются соответственно первым и вторым входами блока, а выход подключен к счетному входу счетчика, выход старшего разряда и вход установки в исходное состояние которого являются соответствен- но первым выходом и третьим входом блока, один вход и выход цифрового управляемого резистора являются соответственно четвертым входом и вторым выходом блока, а управ Л гющие входы цифрового управляемого резистора подключены к разрядным выходам счетчш а. На фиг. 1 дана блок-схема предлагаемого устройства; на фиг. 2 - схема бтгока анализа интервалов импульсной последовательности; на фиг. 3 - временная диаграмма, иллюстрирующая работу устройства. Устройство содержит первый и второй триггеры 1 и 2, счетчик 3 входных сигналов, счетчик 4 результата, первый, второй и третий временные селекторы 5-7, генератор 8 импульсов, дешифратор 9, компаратор 10, интегратор 11, первый и второй элементы ИЛИ 12 и13, И блоков 14-1-14-rt анализа интервалов импульсной последовательности, элемент И ГВ, блок 16 деления, источник 17 опорного напряжения и коммутатор 18. Входная шина устройства обозначена Вход, Каждый бпок 14 содержит (см. фиг. 2} элемент И 19, счетчик 20 и цифровой управляемый резистор (ЦУР) 21. Счетчик 20 управляет величиной сопротивления R/ цифрового управляемого резистора 21 по следующему закону при mi о при t (l) при i 3 Ij приЛ7 -I, где (Т)} состояние старшего разряда счетчика 20; RO некоторое фиксированное сопротивпение:f- . сопротивление разомкнутого ЦУР; О - масштабный коэффициент. Таким образом, t -и блок анализа: при Т| s Т преобразует величину Т| в пропорциональную ей величину сопротивления, включенного между четвертым входом и первым выходом блока, причем в исходном состоянии - до начала интервала tj , а также в случае tj Т, j „g блок анализа обеспечивает равенствопри i 1 Г при I f 1; „ри Ц Т I -и блок анализа генерирует импульс на втором выходе. Здесь t j -интервалы времени, среднее гармоническое значение которых f необ- ходимо определить; { Т - заранее фиксируемая положительная константа. Значение V определяется формулой где г) - число интервалов. Устройство работает следующим образом. В исходном состояний триггеры 1 и 2, а также счетчик 3 входных сигналов и счетчик 4 результата установлены в нуль, а счетчики блоков анализа интервалов импупьсной поспедоватепьности - в максимум ( в состояние 1 1 ... l). При этом третий временной селектор закрыт, возбуждена только одна - первая - выходная шина дешифратора 9, соединенная с вторым входом первого блока 14-1 анализа импульсной поспедоватепьности, т.е. со вторым (потенциальным) входом его эпемента И 19; сопротивления ЦУР 21 блоков анализа интервалов импульсной поспедоватепьности определяются при этом форму пой (2) . Первый импульс, поступаюдий на вхо устройства, т.е. фиксирующий момент начала первого интервала Т} импульсной последовательности (см. фиг. За), устанавливает триггер 2 в единичное состояние; через элементИ 15 и второй времен ной селектор 6 этот импупьс не проходит так как в момент его поступления на их вторых входах единичный потенциал отсут ствует. После опрокидывания триггера 2 второй и третий временные селекторы 6 и 7 открываются. Импульсы с выхода генератора 8 импульсов начинают поступать на вход первого блока 14-1 анализа интервалов импульсной последовательности, т.е первый (импульсный) вход его элемента И 19. Так как Т, Т, ввиду этого импульс на втором выходе первого блока анализа (т.е. на соответствующем входе первого элемента ИЛИ 12) еще не появится, когда придет второй импульс на .входную шину устройства, фикс1фующий окончание интервала Т и, возможно, наможет:оказаться. чало интервала что fi 1, т.е. первый интервал fj является и последним - это произойдет, если в течение времени Т на входтгую шину не поступит третий импульс). Этот второй импульс, не изменяя стояния триггера 2, проходит через откры тый теперь временной селектор 6, фикси- руя на счетчике 3 число поступивших на вход устройства интервалов импульсной последовательности (в данном случае единицу). В результате, возбужденной оказывается вторая шина дешифратора, и импульсы с выхода генератора 8 начинаю поступать на вход счетчика второго блок 14-2 анализа. Ясно, что из счетчике пер вого блока анализа остается зафиксирова ным число NJ , пропорциональное длитель ности интервала Tj , т.е. сопротивление RJ ЦУР 21 первого блока 14-1 пропор ционально теперь величине Rj ClTx Еслн для ti всегда выполняется уелоне (2), то ддя Tg возможны два случая: Т, т.е. интервал t возможо, не последний; Хз Т, т.е. интервал Т уже не ринадлежит импульсной последовательноси, т.е. П 1. В первом случае схема работает анаогично описанному: в момент окончания Г. .т.е. в момент поступления третьео импульса на входн то шину устройства, возбуждается следующая, третья, выходная тина дешифратора 9, при этом оказывается R atg , икшульсы с выхода генератора 8 начинают поступать на счетчик третьего блока 14-3 анализа интервалов сной последовательности и т.д. Если же после достижения равенства 2 Т {когда счетчик 20 второго блока 14-2 анализа установлен в состояние 011 ...l) очередной импульс на выходе генератора 8 возникает раньше, чем третий импульс на входной шине устройства, т.е. tg Т, счетчик 120 переходит в состояние 100 ...О, при этом возникает импульс на выходе блока 14-2 анализа, свидетепьствую.ций о том, что предшествующий ( в данном случае первый) интервал tj был последним- инте; валом импульсной последовательности, т.е. П 1. - Ясно, что в случае Т Т будет совершено аналогично описанному проанализирован интервал t и т.д., до тех пор, по- ка не будет выполнено одно из двух условий:ti Т, t jV т.е. П 1-1 (этот случай проиллюструфован на фиг. 3, где t т); или i N, tj i Т. В первом случае будет аналогично описанному сформтфован импульс на выходе f -го блока анализа интервалов импупьсной последовательности. Во втором случае входной импульс устройства, фиксирующий момент окончания П -го интервала импульсной последовательности, проходит не только через временной селектор 6 на счетный вход счетчика 3, но и через элемент 1-1 15 на вход элемента ИЛИ 12, так как последняя П -ная выходная щина дешифратора 9 соединена не только с первым входом П -го блока анализа, но и со вто- рым (нотетшиальным) входом элемента И Таким образом, в обоих случаях возникает импульс на выходе первого элемента ИЛИ 12. К этому моменту на счетчике входны скгнапов будет зафиксировано ч:нсг:с ; анализированных интервалов ( j на фиг. 3 П « 4, т.е. проводимость f ЦУР блока 16 деления будет при этпм пропорциональной ri, а сопротивпеьл-1я ЦУР блоков 14-1-14 п анализа будут пропорциональны величинам t/ при ,-Пи бесконечны (разрыв цепи) при п , Прн этом напряжение на. выходе блока 16 де лений ; J . г аЬп Ь| (4) Импульс с Выхода элемента ИЛИ 12 тгооходит через элемент ИЛИ 13 на выходную шину устройства, возврапдает тртйт-ер 2 в нуль и опрокидывает в едйнкиу триггер ;L Прк STOM, во-первых, времешгьш Сйяеко;0- ры 6 и 7, закрываются а ..врэмвкно1 c&лектор 5 открывается, во-вторых, комму-татор 18 соединяет рабочий (второй/ вход интегратора 1.1 с выходом б дока 16 де-пэнияг а сам интегратор переводится в режим интегрирования Спустя время i после начала интегрировал-шя напряжение W на выходе нктегратора будет равноУ -СУГ, где кОчЭффкциент С определяется парамет-рамй интегратора, ИЕ тегркровакие продо жается до момента ;доетйженкя равенства Из BbipaJKeHHS имеем п |эдесь I нйент „ В (б) возннкеет кмкупьс на выходе компаратора Юг выполняющий спедз схциа (|;у.а&скгпaj установка в исходное .-OC-TOS:HHS счетчика 3 входных снгнапоэ б) установка в исходное Ст-гупевое соетояинэ Tpsirrepa 1, т.е. за{ рьЕТйе йре-менного селектора S и яеревод интеграто ра 13, в исходное состо ягие (зход зазам:лен через комгшутатор 3, Sj выходкой равен jiymo)|, - в) устанодка внеходкое состояние всех бноков14-1-14-и анализа ййтервалов HJ пупьсгаой последоаатеяьностн это сущест-- венкр ДЛИ h первых блоков, остагхьЕ-шэ (есш1 ) отбвага-:сь в исходжгм со-стодагаиг) форыгфоаанне 1гмпульса на выходе эпемегтга ИЛИ 13, Число ш-лпульсов. 61 ступивших на счет}а1Й вход счетчика 4 резутътата за время t , ра&но Т- fgf Таким образом, интервал между импульсами на выходной шине устройства (выход элемента ИЛИ 13) и числоs зафиксированкое на счетчике 4 результата будут с коэффициентами и f соответственно пропорциональны среднему гармонич& скому значению интервалов t| импульс ной последозатепьности, Для определения среднего гармонического значения аналогового случайного процесса достаточно преобразовать значеш-ш этого процесса, взятые в различные момекты времени, в последовательность лтропорциональных этим значения я времен vfax ннтерБалов, например, с помощью ааиюфоннопз врем& импульсного преобра- -. зователя развертывающего типа. Ф о р м у п а изобретения U Устройство для ощэедепения среднего гарлюннческого значения случайного процесса, содержащее первый и второй грйггерьь счет-чик входных сигналов, пер«вый и второй временные сйпекторы, счеэ чйк ре-зультата, счетный вход которого т эдкяючен к выходу первого временного секйктора, яервьЕЙ вход которого соедикеп с единичным выходом первого триггера, а второй вход подключен к выходу г&кератора импульсов, единичный вход второго триггера подк-лючен к входу устройства и к первому входу второго враменного censKTopaj. второй вход которого соединен с вnкнwчгi.ы.I выходом второго трг-шгера, а выход подключен к счетному входу - счегчйяа шшдкьг). сигналов; отяйчающе- е с я что, с целью расширения функгдяональЕьгх Боамо7каостей устройства, в не- Г ) ввег.йнь дешйфрат-ор, коМ1тара.тор, интег ратср, яарвый н второй элементы ИЛИ, третий временной селектор h. блоков анФfBsa гштервалов импульсной последоватегаьности; элемент 1Л, блок деления., источникoriopHoro нйлражешгя и KOMMji-TaTop, при s.coM Выходи дешиЬратора подключены к первым входам соответс-гв5 7ощих блоков ав:ализа интервалов имщсльской последо ватешдности, вторые входы которых соединэщ-, с выходом третьего временного се™ пзктора, первый вход кот-орого соединён с выходомгенера-гора нмпупьсов, а второй вход подключен к едншмному выходу второго триггера, 1улевой вход которого со- эйннэк с выходом первого элемента ИЛИ

с единичттым входом первого триггера, е BjcoaoM установки в нуль счетчика результатов и с первым входом второго эпемента ИЛИ, -второй вход которого подключен к входу установки в нуль счетчика входных сигналов, к выходу- компаратора и к третьим входам блоков а1шпиза интервапов импульсной последовательности, первые выходы которых соединены с соответствующими входами первого элемента ИЛИ а вторые выходы, подключены к информационному входу блока деления, управляющие входы которого соединены с разрядными выходами счетчика входных сигналов, а выход блока делетшя подкточен к первому входу коммутатора, второй вход которого соединен с первым входом интегратора и с единичным врлходом первого триггера, а выход коммутатора соединен с вторым входом интегратора, выход которого подключен к не-рвому входу ком- паратора, второй вход которого соединен с выходом источника опорного напряжения и четвертым входом блока анализа интервалов импупьсной поспедоватепьности, (П+ 1)-й вход первого элемента ИЛИ подключен к выходу элемента И, первый

вход которого соединен с входом устройства, а второй вход подключен к п -му выходу дешифратора, которого подключены к разрядным выходам счетчика входных сигналов.

2. Устройство по п. 1, о т л и ч а ющ е е с я тем, что блок анализа -интервалов импульсной последовательности содержит элемент И, первый и второй входы которого 5шл$оотся соответственно первым и вторым входами бпока, а выход подключен к счетному входу счетчика, выход старшего разряда и вход установки в исходное состояние которого явпшотся соответственно первым выходом и третьим входом блока, один вход и выход цифрового управляемого резистора явлшотся соответственно четвертым входом и вторым выходом блока, а управпяюшие входы цифрового управляемого резистора подключеiibi к разряд1Сз1М выходам счетчике.

Источники информации, щэинятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 308432, кп, G 06 F 15/36, 1971.

2,Авторское свидетельство СССР .N 269631, кл. G 06 G 7/52, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов | 1979 |

|

SU822333A1 |

| Селектор импульсов по длительности | 1979 |

|

SU817997A1 |

| Устройство для определения характеристик случайных импульсных потоков | 1979 |

|

SU773627A1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Диапазонный измеритель временных интервалов последовательного счета | 1985 |

|

SU1307440A1 |

| Дишифратор времяимпульсного кода | 1985 |

|

SU1367162A1 |

| Селектор импульсов по длительности | 1981 |

|

SU1005290A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Устройство для цифрового измерения разности частот электрических колебаний | 1973 |

|

SU495616A1 |

| Селектор импульсов | 1981 |

|

SU993465A1 |

Авторы

Даты

1979-06-25—Публикация

1975-09-23—Подача