18

ГО

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для измерения отношения сигнал/шум | 1987 |

|

SU1465827A1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Селектор импульсных сигналов | 1982 |

|

SU1058043A1 |

| Цифровой фильтр | 1980 |

|

SU888335A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

Изобретение относится к автоматике, а именно к устройствам преобразования информации, и может быть использовано в системах вторичной радиолокации для декодирования время импульсных кодов. Изобретение позволяет повысить вероятность декодирования кодов, а также повышает помехоустойчивость дешифратора при образовании ложных интервалов из импульсов помех, за счет чего достигается повьш1ение достоверности преобразуемой информации. Дешифратор времяим- пульсного кода содержит два элемен- . та И 1 и 2, два регистра 3 и 4 сдвига, селектор 5 импульсов, пять триггеров 6-10, блок 11 элементов.1 2 И-НЕ, элемент 1Э.ИЛИ-НЕ, два элемента 14 и 15 И-НЕ, делитель 16 частоты, генератор 17 тактовых импульсов. Делитель 16 частоты содержит два селектора переднего фронта импульсов, два элемента задержки, три элемента И, триггер, элемент ИЛИ и счетчик импульсов. 1 з.п. ф-лы, 2 ил. С

Ц

J

Jis

ё

5

J

Jis

.JLфиг-f

Изобретение относится к автоматике, а именно к устройствам преобразования информации, и может быть использовано в системах вторичной радиолокации для декодирования время- импульснь;х кодов. . .

Цель изобретения - повьшение достоверности преобразуемой информации..

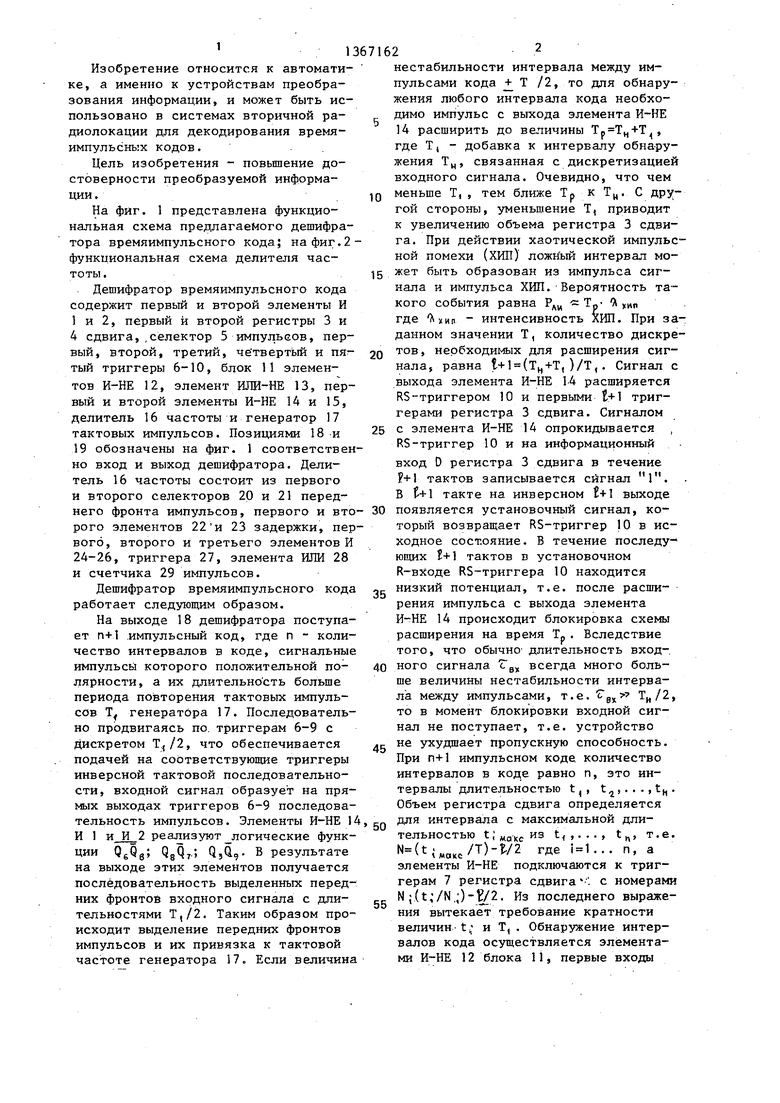

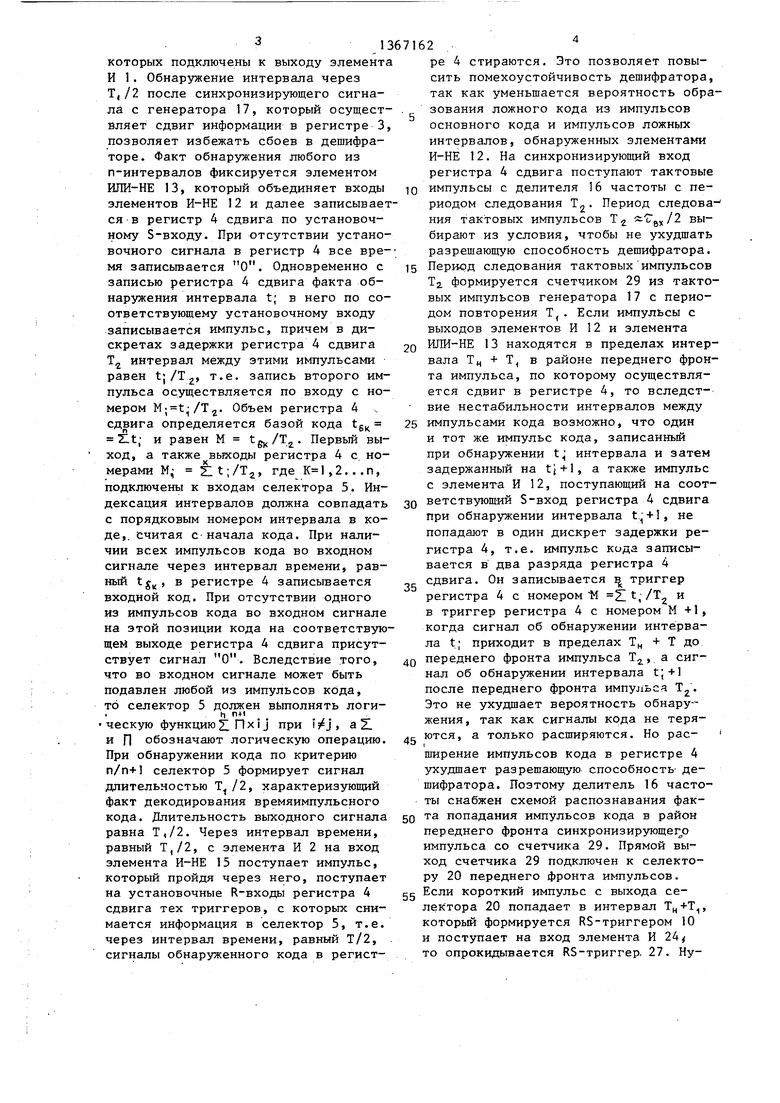

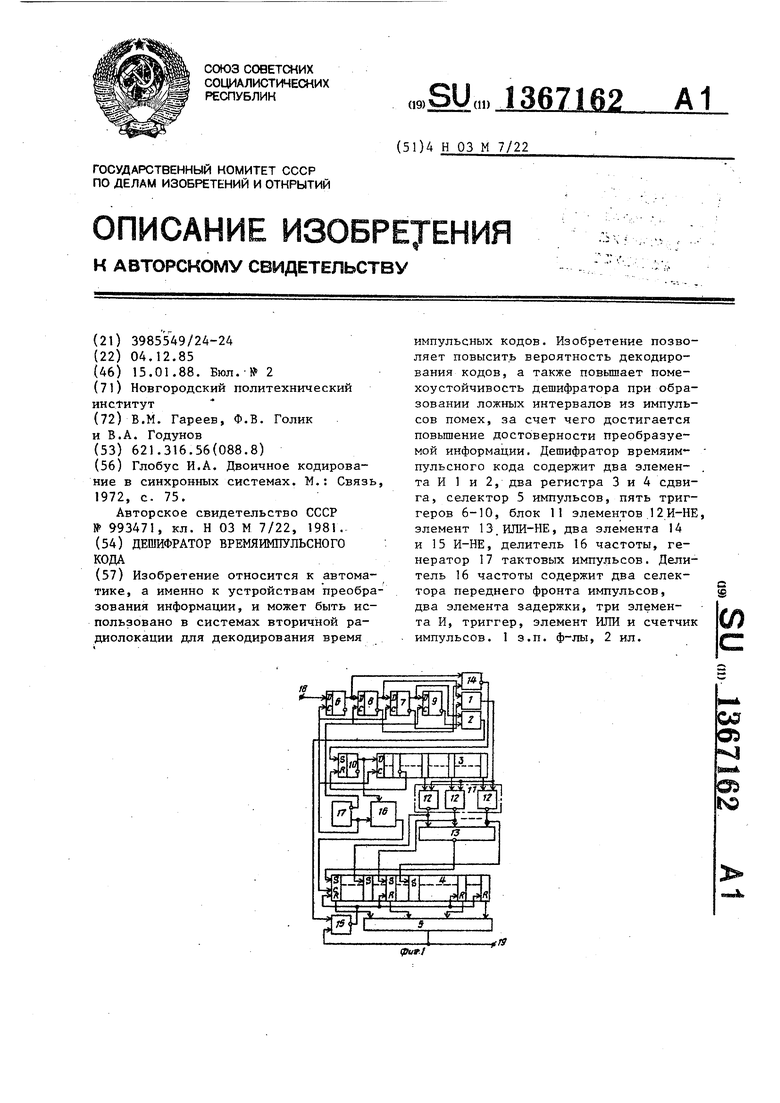

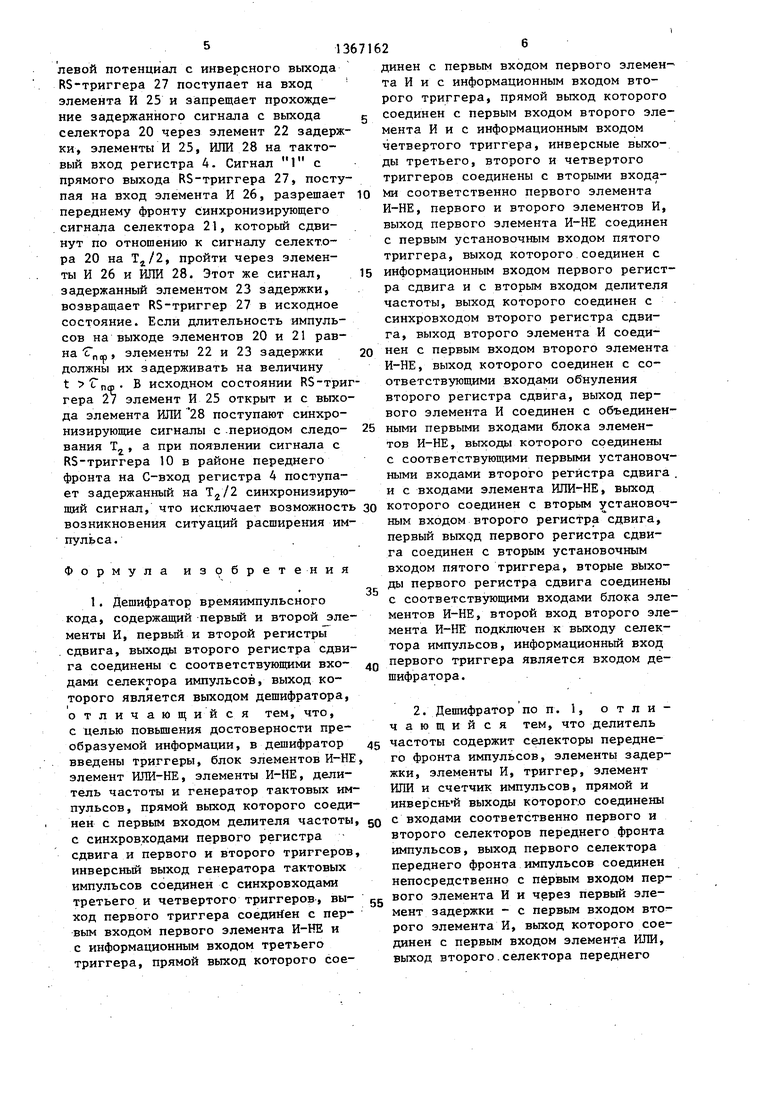

На фиг. 1 представлена функциональная схема предлагаемого дешифратора времяимпульсного кода; на фиг.2 функциональная схема делителя частоты.

Дешифратор времяимпульсного кода содержит первый и второй элементы И 1 и 2, первый и второй регистры 3 и 4 сдвига, .селектор 5 импульсов, первый, второй, третий, че твертЬгй и пя тый триггеры 6-10, блок 11 элементов И-НЕ 12, элемент ИЛИ-НЕ 13, первый и второй элементы И-НЕ 14 и 15, делитель 16 частоты и генератор 17 тактовых импульсов. Позициями 18 и 19 обозначены на фиг. 1 соответственно вход и выход дешифратора. Делитель 16 частоты состоит из первого и второго селекторов 20 и 21 переднего фронта импульсов, первого и второго элементов 22 и 23 задержки, первого, второго и третьего элементов И 24-26, триггера 27, элемента ИЛИ 28 и счетчика 29 импульсов.

Дешифратор времяимпульсного кода работает следующим образом.

На выходе 18 дешифратора поступает п+1 .импульсный код, где п - количество интервалов в коде, сигнальные импульсы которого положительной полярности, а их длительность больше периода повторения тактовых импульсов Т генератора 17. Последовательно продвигаясь по. триггерам 6-9 с дискретом Т,/2, что обеспечивается подачей на соответствующие триггеры инверсной тактовой последовательности, входной сигнал образует на прямых выходах триггеров 6-9 последова

тельность импульсов. Элементы И-НЕ 14,дд дпя интервала с максимальной длиИ 1 и И 2 реализуют логические функции OeQe S результате на выходе этих элементов получается последовательность выделенных перед-: них фронтов входного сигнала с длительностями Т,/2. Таким образом происходит выделение передних фронтов импульсов и их привязка к тактовой частоте генератора 17. Если величина

N(ti,,/T)-t/2 элементы И-НЕ

55

тельностью t,,,.., t,, т

где ... n, а подключаются к три герам 7 регистра сдвига . с номер N ;(t, /N.;), Из последнего выраж ния вытекает требование кратности величин и Т, . Обнаружение интер валов кода осуществляется элемент ми И-НЕ 12 блока 11, первые входы

5

0

с

нестабильности интервала между импульсами кода + Т /2, то для обнаружения любого интервала кода необходимо импульс с выхода элемента И-НЕ 14 расширить до величины , где Т, - добавка к интервалу обнаружения Т„, связанная с дискретизацией входного сигнала. Очевидно, что чем меньше Т, , тем ближе Тр к Т. С цру- гой стороны, уменьшение Т, приводит к увеличению объема регистра 3 сдвига. При действии хаотической импульсной помехи (ХИП) ложн ый интервал может быть образован из импульса сигнала и импульса ХИП. Вероятность такого события равна , - Тр- Л «„ где Лхип - интенсивность лИП. При заданном значении Т, количество дискретов, нербходш ых для расширения сигнала, равна .+ I (TJ,+T, )/Т,. Сигнал с выхода элемента И-НЕ 1-4 расширяется RS-триггером 10 и первыми t+1 триггерами регистра 3 сдвига. Сигналом 5 с элемента И-НЕ 14 опрокидывается RS-триггер 10 и на информационный

вход D регистра 3 сдвига в течение +1 тактов записывается сигнал 1. В t+l такте на инверсном t+l выходе появляется установочный сигнал, который возвращает RS-триггер |0 в исходное состояние. В течение последу- ющих +1 тактов в установочном R-входе RS-триггера 10 находится низкий потенциал, т.е. после расширения импульса с выхода элемента И-НЕ 14 происходит блокировка схемы расширения на время Т., Вследствие того, что обычно-длительность вход- 0 ного сигнала Тц, всегда много больше величины нестабильности интерва0

5

ла между импульсами, т.е.

в.

Т„/2,

то в момент блокировки входной сигнал не поступает, т.е. устройство не ухудшает пропускную способность. При п+1 импульсном коде количество интервалов в коде равно п, это интервалы длительностью t,, t,.,.,t. Объем регистра сдвига определяется

дпя интервала с максимальной длиN(ti,,/T)-t/2 элементы И-НЕ

тельностью t,,,.., t,, т.е.

где ... n, а подключаются к триггерам 7 регистра сдвига . с номерами N ;(t, /N.;), Из последнего выражения вытекает требование кратности величин и Т, . Обнаружение интервалов кода осуществляется элементами И-НЕ 12 блока 11, первые входы

которых подключены к выходу элемент И 1. Обнаружение интервала через Т,/2 после синхронизирующего сигнала с генератора 17, который осущест вляет сдвиг информации в регистре 3 позволяет избежать сбоев в дешифраторе. Факт обнаружения любого из п-интервалов фиксируется злементом ИЛИ-НЕ 13, который объединяет входы элементов И-НЕ 12 и далее записывается в регистр 4 сдвига по установочному S-входу. При отсутствии установочного сигнала в регистр 4 все время записьтается О. Одновременно с записью регистра 4 сдвига факта обнаружения интервала t; в него по соответствующему установочному входу записывается импульс, причем в дискретах задержки регистра 4 сдвига Т интервал между этими импульсами равен t|/T, т.е. запись второго импульса осуществляется по входу с номером . Объем регистра 4 ,. сдвига определяется базой кода tg ilt; и равен М ,. Первый выход, а также выходы регистра 4 с, номерами М Zlti/Tj, где ,2...п, подключены к входам селектора 5. Индексация интервалов должна совпадать с порядковым номером интервала в коде,. Считая с-начала кода. При наличии всех импульсов кода во входном сигнале через интервал времени, равный tj, в регистре 4 записывается входной код. При отсутствии одного Из импульсов кода во входном сигнале на этой позиции кода на соответствующем выходе регистра 4 сдвига присутствует сигнал О. Вследствие того, что во входном сигнале может быть подавлен любой из импульсов кода,

то селектор 5 должен вЬшолнять логиh ческую функцию 2 П X i j при , а Z.

и П обозначают логическую операцию. При обнаружении кода по критерию п/п+1 селектор 5 формирует сигнал длительностью , характеризующий факт декодирования времяимпульсного кода. Длительность выходного сигнала равна Т,/2. Через интервал времени, равный Т,/2, с элемента И 2 на вход элемента И-НЕ 15 поступает импульс, который пройдя через него, поступает на установочные R-входы регистра 4 сдвига тех триггеров, с которых снимается информация в селектор 5, т.е. через интервал времени, равный Т/2, сигналы обнаруженного кода в регист62 ..

ре 4 стираются. Это позволяет повысить помехоустойчивость дешифратора, так как уменьшается вероятность образования ложного кода из импульсов основного кода и импульсов ложных интервалов, обнаруженных элементами И-НЕ 12. На синхронизирующий вход регистра 4 сдвига поступают тактовые импульсы с делителя 16 частоты с периодом следования Т. Период следова ния тактовых импульсов Т бирают из условия, чтобы не ухудшать разрешающую способность дешифратора. Период следования тактовых импульсов Tj. формируется счетчиком 29 из тактовых импульсов генератора 17 с периодом повторения Т. Если импульсы с выходов элементов И 12 и элемента ИЛИ-НЕ 13 находятся в пределах интервала Тц + Т в районе переднего фронта импульса, по которому осуществляется сдвиг в регистре 4, то вследствие нестабильности интервалов между импульсами кода возможно, что один и тот же импульс кода, записанный при обнаружении t интервала и затем задержанный на tj+l, а также импульс с элемента И 12, поступающий на соот- ветствующ-ий S-вход регистра 4 сдвига при обнаружении интервала t. + 1, не попадают в один дискрет задержки регистра 4, т.е. импульс кода записывается в два разряда регистра 4 сдвига. Он записывается триггер регистра 4 с номером М ZI t,/Т и в триггер регистра 4 с номером М +1, когда сигнал об обнаружении интервала t; приходит в пределах „ + Т до переднего фронта импульса 1, а сигнал об обнаружении интервала tj+1 после переднего фронта импу:1Ьса Т. Это не ухудшает вероятность обнаружения, так как сигналы кода не теряются, а только расширяются. Но рас-

ширение импульсов кода в регистре 4 ухудшает разрешающую способность- дешифратора. Поэтому делитель 16 частоты снабжен схемой распознавания факта попадания импульсов кода в район переднего фронта синхронизирующег,о импульса со счетчика 29. Прямой выход счетчика 29 подключен к селектору 20 переднего фронта импульсов. Если короткий импульс с выхода селектора 20 попадает в интервал Т„+Т,, который формируется RS-триггером 10 и поступает на вход элемента И 24 то опрокидьгаается RS-триггер. 27.

левой потенциал с инверсного выхода RS-триггера 27 поступает на вход элемента И 25 и запрещает прохождение задержанного сигнала с выхода селектора 20 через элемент 22 задерки, элементы И 25, ИЛИ 28 на тактовый вход регистра 4. Сигнал 1 с прямого выхода RS-триггера 27, постпая на вход элемента И 26, разрешае переднему фронту Синхронизирующего сигнала селектора 21, который сдвинут по отношению к сигналу селект.о

ра 20 на Tj,/2, пройти через элементы И 26 и ИЛИ 28. Этот же сигнал, задержанный элементом 23 задержки, возвращает RS-триггер 27 в исходное состояние. Если длительность импульсов на выходе элементов 20 и 21 равна rntp, элементы 22 и 23 задержки должны их задерживать на величину t Гп(р. В исходном состоянии RS-триггера 2/ элемент И 25 открыт и с выхода элемента ИЛИ 28 поступают синхронизирующие сигналы с .периодом следования Tj, а при появлении сигнала с RS-триггера 10 в районе переднего фронта на С-вход регистра 4 поступает задержанный на синхронизирующий сигнал, что исключает возможность возникновения ситуаций расширения им- .

Формула изобретения

I

отличающийся тем, что, с целью повышения достоверности преобразуемой информации, в дешифратор введены триггеры, блок элементов И-НЕ элемент Ш1И-НЕ, элементы И-НЕ, делитель частоты и генератор тактовых импульсов, прямой выход которого соединен с первым входом делителя частоты с синхровходами первого регистра сдвига и первого и второго триггеров инверсный выход генератора тактовых импульсов соединен с синхровходами третьего и четвертого триггеров, выход первого триггера соедийен с первым входом первого элемента И-НЕ и с информационным входом третьего триггера, прямой выход которого сое0

15

0

ЗО

динен с первым входом первого элемента И и с информационным входом второго триггера, прямой выход которого соединен с первым входом второго элемента И и с информационным входом четвертого триггера, инверсные выходы третьего, второго и четвертого триггеров соединены с вторыми входа- Ми соответственно первого элемента И-НЕ, первого и второго элементов И, выход первого элемента И-НЕ соединен с первым установочным входом пятого триггера, выход которого соединен с информационным входом первого регистра сдвига и с вторым входом делителя частоты, выход которого соединен с синхровходом второго регистра сдвига, выход второго элемента И соединен с первым входом второго элемента И-НЕ, выход которого соединен с соответствующими входами обнуления второго регистра сдвига, выход первого элемента И соединен с объединеи- 25 ными первыми входами блока элементов И-НЕ, выходы которого соединены с соответствующими первыми установочными входами второго регистра сдвига . и с входами элемента ИЛИ-НЕ, выход которого соединен с вторым установочным входом второго регистра сдвига, первый выхдд первого регистра сдвига соединен с вторым установочным входом пятого триггера, вторые выходы первого регистра сдвига соединены с соответствующими входами блока элементов И-НЕ, второй вход второго элемента И-НЕ подключен к выходу селектора импульсов, информационный вход первого триггера является входом де35

40

45

50

55

шифратора.

фронта импульсов соединен с первым входом третьего элемента И, выход которого соединен непосредственно с вторым входом элемента ИЛИ и через второй элемент задержки - с первым установочным входом триггера, прямой и инверсный выходы которого соединены с вторыми входами соответственно

третьего и второго элементов И, выход первого элемента И соединен с вторым установочным входом триггера, вход счетчика импульсов и второй вход первого элемента И являются соответственно первым и вторым входами делителя, выход элемента ИЛИ является выходом делителя.

cpi/ff.Z

| Глобус И.А | |||

| Двоичное кодирование в синхронных системах | |||

| М.: Связь, 1972, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Дешифратор | 1981 |

|

SU993471A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-15—Публикация

1985-12-04—Подача