(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1981 |

|

SU962946A1 |

| Многоканальное устройство для обслуживания запросов со сменными кодами приоритетов | 1984 |

|

SU1180892A2 |

| Многоканальное устройство приоритета | 1981 |

|

SU1012259A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1282128A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Многоканальное устройство динамического приоритета | 1981 |

|

SU970371A1 |

| Многоканальное устройство для приоритетного обслуживания запросов | 1983 |

|

SU1111164A1 |

| Устройство для приоритетного опроса | 1983 |

|

SU1105894A1 |

| Многоканальное устройство переменного приоритета | 1978 |

|

SU746521A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1983 |

|

SU1109754A1 |

Изобретение относится к области j вычислительной техники, в частности, к устройствам приоритетного обслуживания запросов и может быть использовано в системах обработки данных.

Известно многоканальное устройство приоритета, содержащее элементы И, два регистра, дешифраторы, схему сравнения, триггер, счетчик 1.

Недостаток устройства - необходимость большого количества оборудования.

Известно также многоканальное устройство приоритета, содержащее регистр заявок, регистры приоритета, счетчики, триггеры, генератор импульсов , группы элементов И, элементы ИЛИ t 2.

Недостатками данного устройства являются необходимость иметь счетчик на каждый запросный вход устройства и малое быстродействие, которое определяется быстродействием счетчика и содержимым кода приоритета.

Известно также приоритетное устройство, содержащее регистр приоритета, счетчик, блок управления, циклический регистр сдвига, блок анализа счетчика на нуль, блок анализа

на единицу старшего разряда циклического регистра сдвига 3.

Недостаток устройства - низкое быстродействие, обусловленное последов ат ель ньв.1 характером анализа приоритетов.

Наиболее близким к изобретению является многоканальное устройство приоритета, содержащее Глифратор, а в

0 каждом канале элемент И, элемент НЕ, элемент ИЛИ, причем каждый запросный вход устройства соединен с первыми входами элемента И и элемента ИЛИ соответствующего канала, выход эле5мента НЕ канала соединен со вторым входом элемента И канала, выходы элементов И каналов через шифратор соединены с выходом устройства 4).

Недостатком устройства является

0 наличие ограниченных функциональных возможностей, поскольку оно позволяет организовать лишь жесткий порядок обслуживания запросов.

Цель изобретения - расширение

5 функциональных возможностей за счет переменного порядка обслуживания запросов .

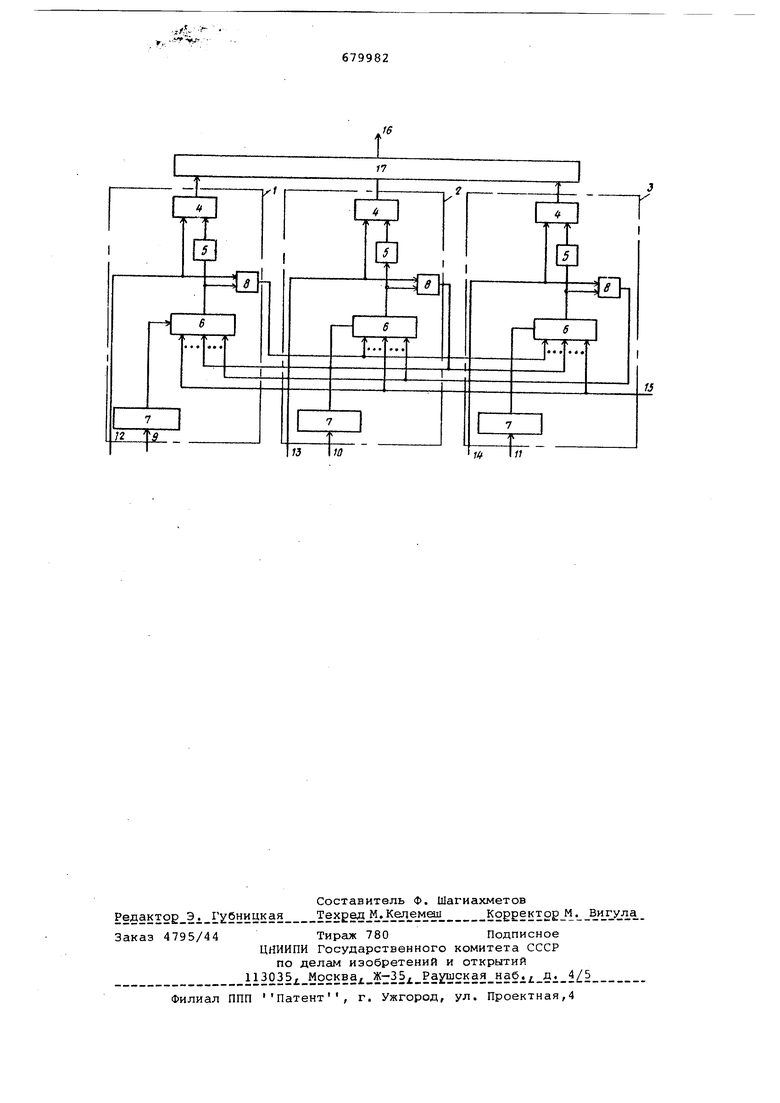

Поставленная цель достигается тем, что устройство содержит в каждом ка0 .нале регистр кода приоритета и коммутатор, причем каждый кодовый вход устройства через регистр кода приори тета соответствующего канала соедине с управляющим входом коммутатора это го канала, выход коммутатора канала соединен со входом элемента НЕ канала и со вторым входом элемента ИЛИ канала, выход элемента ИЛИ i-ro кана ла соединен с i-ми сигнальными входа ми коммутаторов предыдущих и последу щих каналов, а разрешающий вход устройства соединен в каждом канале с сигнальным входом коммутатора, соответствующим номеру каНсша. Структурная схема устройства приведена на чертеже. Многокансшьное устройство приоритета содержит: каналы 1-3, каждый из которых содержит элемент И 4, элемент НЕ 5, коммутатор б, регистр кода приоритета, элемент ИЛИ 8. Устройство содержит также кодовые входы 9-11, запросные входы 12-14, разрешающий вход 15, выход 16, шифратор 17. Устройство работает следующим образом. Перед Началом работы устройства, на регистр 7 кода устройства приоритета, через входы 9-11 заносятся коды, которые совместно с коммутаторами б и элементами ИЛИ 8 обеспечивают начальное распределение запросов по приоритетам. По мере необходимости распределение приоритетов может динамически изменяться, для чего достаточно изменить содержимое регистров 7 кода приоритета, в соответствии с требуемым распределением запросов по приоритетам. Изменение должно производиться в паузах работы устройства, когда на входах 12-14 отсутствуют запросы. Необходимые кодовые комбинации на регистрах 7 кода приоритета определяются в соответствии с требуемым распределением запросов по приоритатам по следующим правилам 1. Регистр 7 кода приоритета самого старшего по приоритету канала должен содержать код, равный номеру данного канала, обеспечивая тем самым подключение к выходу коммутатора 6 данного канала входа 15, подклю ченного к шине логического нуля. Нол на выходе этого когФ1утатора через эл мент НЕ 5 разрешает прохождение запроса со входа 12 (или 13, 14) через элемент И 4 ланного канала на вход шифратора 17, Крометого, появление запроса ка запросном входе данного к нала вызывает последовательную блоки ровку обслуживания остальных, более младших по приоритету каналов устрой ства через элемент ИЛИ 8 данного канала и коммутаторы б элементы ИЛИ 8 ост аль ных к ан алов, 24 2, Регистр 7 кода приоритета каждого последукядего младшего по приоритету канала устройства должен содержать код, равный номеру предыдущего старшего по приоритету канала. Например, для четырехвходового устройства, имеющего каналы 1,2,3,4 при распределении (в порядке убывания) приоритетов следукядим образом: 2,1,4,3 регистр 7 кода приоритетов должны содержать следующие коДы:НОМЕР КАНАЛА УСТРОЙСТВА 1234 СОДЕРЖИМОЕ РЕГИСТРОВ КОДА ПРИОРИТЕТА2241 Указанные коды в регистрах 7 кода приоритета формируют структуру устройства таким образом, что появление запроса в старшем по приоритету вто ром канале устройства блокирует обслуживание запросов, возникших на входах 1, 4 и 3 каналов 6 устройства в порядке убывания приоритетов. Код, равный двум в регистре 7 второго канала, самого старшего по приоритету, вызывает появление нулевого ° выходе коммутатора 6 канала 2 (так как второй вход ксдамутатора б соединен со входом 15) и через элемент НЕ 5 обеспечивает прохождение запроса через элемент И 4 канала 2 на вход шифратора 17, Кроме того на; выходе элемента ИЛИ 8 канала 2f. при наличии запроса на входе 13 вырабатывается единичный сигнал. ЕДИНИЧНЫЙ сигнал выхода элемента ИЛИ 8 канала 2 блокирует через коммутатор б и элемент ЯЕ 5 канала 1 запрос со входа 12, так как код, равный двум регистрам 7 кода приоритета канала 1,подключает первый вход коммутатора б к его выходу. Единичным сигналом с выхода элемента ИЛИ 8 канала 1 через первый вход коммутатора 6 и элемент ЯЕ 5 четвертого канала (не показан) блокируется обслуживание запроса, поступившего на вход четвертого канала. так как код, равный единице в регистре 7 кода приоритета четвертого канала подключает первый вход коммутатора 6 четвертого канала к выходу этого коммутатора . Единичным сигналом с выхода элемента ИЛИ 8 четвертого канала через четвертый вход коммутатора б и эле мент НЕ 5 канала 3 блокируется обс-луживание запроса канала 3, так как , равный четырем, на регистре 7 кода приоритета четвертого канала подключает четвертый вход коммутатора б канала 3 к выходу этого коьшутатора, Отсутствие запроса на входе 13 самого старшего по приоритету (в данном случае канала 2) снимает вышеописанную последовательную цепь блокировок и появляется возможность удовлетворения возникающих запросов по запросным входам каналов 1, 3 и четвертого канала. Другими словами, запрос пост пивший на вход i-ro канала пропуска ся н вход шифратора 17, если отсут ствует блокировка запроса со стороны канала, старшего по приоритету, то есть, если выполняется условие Vзапросы в младших по приоритету каналах, чем i-йУблокируются с помощью выработки сигнала . где у - функция необходимости обслуживания запроса хо) . i - номер рассматриваемого канала, i 1, 2,. . ./i; n - количество разрядов устройства Л - код в регистре 7 кода приоритета 1-го канала, который определяет предыдущий (стар ший по приоритету) канал устройства, d 1,2,...)п; f . - сигнал блокировки запроса с стороны канала, старшего по в завиприоритету. симости от кода d в регист ре кода приоритета i-ro канала может принимать значения Р , . . . , ; О , P-f ц.-( , « Р(и определяет выход того канала, который вызывает блокировку в данном канш1е Канал, в котором выполняется условие et ; имеет наивысший приоритет. Из комбинации сигналов на выхода элементов И 4 (единичный сигнал при сутствует всегда только на выходе одного, и только одного элемента И шифратор 17 формирует код номера приоритетного канала на выходе 16, Таким образом, изобретение позво ляет организовать в известном устройстве режим переменного порядка обсл5Ькивания запросов, что обеспечивает расширение функциональных во можностей известного устройства. Формула изобретения Многоканальное устройство приоритета, содержащее шифратор, а в каждом канале элемент И, элемент НЕ и элемент ИЛИ, причем каждый запросный вход устройства соединен с первыми входами элемента И и элемента ИЛИ соответствующего канала, выход элемента ЯЕ канала соединен со вторым входом элемента И канала, выходы элементов И каналов через шифратор соединены с выходом устройства, о тличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения переменного порядка обслуживания запросов, оно содержит в каждом канале регистр кода приоритета и коммутатор, причем каждый кодовый вход устройства через регистр кода приоритета соответствующего канала соединен с управляющим входом коммутатора этого канала, выход коммутатора канала соединен со входом элемента НЕ канала и со вторым входом элемента ИЛИ канала, выход элемента ИЛИ i-ro канала соединен с i-ми сигнальными входами коммутаторов предыдущих и последующих каналов, а разрешающий вход устройства соединен в каждом канале с сигнальным входом коммутатора, соответствующим номеру канала. Источники информации, прин.ятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 292155, кл. G Об f 9/18, 1971. 2.Авторское свидетельство СССР № 475622, кл. G 06 f 9/18, 1975. 3,Авторское свидетельство СССР, 506854, кл. G 06 F 9/18, 1976. 4,Коган Б.М., Каневский М.М, Цифровые вычислительные машины и системы, М., Энергия, 1974, с. 467, р. 85.

679982

Авторы

Даты

1979-08-15—Публикация

1977-07-11—Подача