Изобретение относится к вычислительной технике, в частности к устройствам приоритетного обслуживания запросов и может быть использовано в системах обработки данных.

Известно приоритетное устройство, содержащее регистр приоритета, счетчик, блок управления, циклический регистр сдвига, блок анализа счетчика на нуль и блок анализа старшего разряда циклического регистра сдвига на единицу }

Недостаток устройства - низкое быстродействие, обусловленное последовательным характером анализа приоритетов.

Наиболее близким по технической сущности к предлагаемому является многоканальное устройство приоритета, содержащее шифратор, каналы,в каждом из которых - элемент И, элемент НЕ и элемент ИЛИ .

Недостаток устройства - ограниченные функциональные возможности, так как изменение распределения запросов производится в паузах работы устройс|тва при отсутствии из на входах.

Цель изобретения - расширение функциональных воз 4ожностей устройст ва за счет возможности перемены порядка обслуживания запросов в любой момент времени.

Поставленная цель достигается тем,, что в многоканальное устройство приоритета, содержшдее шифратор, выход которого является информационным вы-, ходом устройства, канашы, а в каждоЦ канале - первый элемент И, первый элемент НЕ, элемент ИЛИ, регистр и

10 коммутатор, причем казхдый запросный вход устройства соединен с первыми входами первого элемента И и элемента ИЛИ соответствующего канала,выход первого элемента НЕ каждого канала

15 соединен с вторым входом первого эл&мента И своего канала, каждый кодо- , вый вход устройства соединен с входом регистра соответствующего канала, выход регистра канала соединен с инфорг

20 мационным входом колмутатора своего канала, выход коммутатора каждого ка|нала соединен с входом первого эле- I мента НЕ своего канала и с вторым входом элемента ИЛИ своего кангша, выход

25 элемента ИЛИ каждого канала соединен с соответствующими управляющими входами KONMyTaTOpoB предыдущих и после:дующих каналов, разрешающий вход устройства соединен в каждом канале

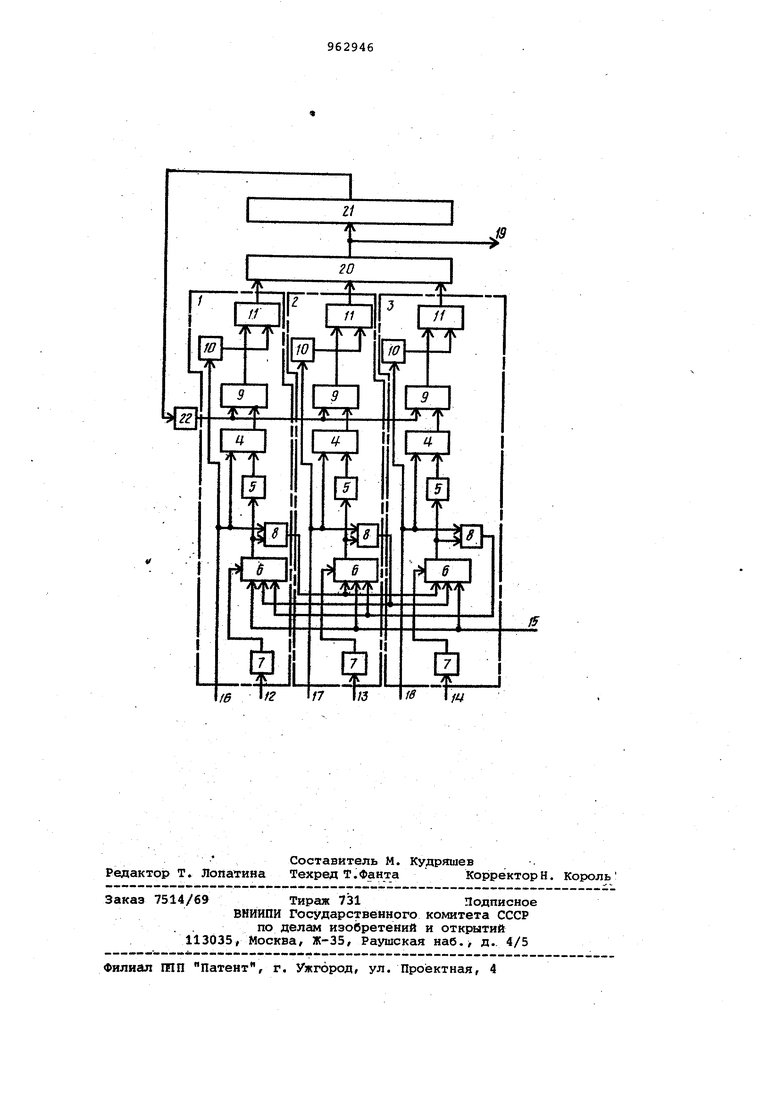

30 с управляющим входом коммутатора, соответ.ствующим номеру канала, введены элемент ИЛИ и элемент НЕ, а в каждом канале-триггер, второй элемент НЕ и второй элемент И, причем запросный вход устройства через второй элемент НЕ соответствующего ка|нала соединен с нулевым входом триггера своего канала, первый вход второго элемента И каждого канала соеди4 нен с выходом первого элемента И сво его канала, выход второго элемента И каждого канала соединен с единичным входом триггера своего канала, выход триггера каждого канала соединен с соответствующим входом шифратора, выход которого соединен с входом эле мента ИЛИ, выход которого через элемент НЕ соединен с вторым входом вто рого элемента И каждого канала. На чертеже приведена структурная схема устройства. Многоканальное устройство приори тета имеет каналы 1-3, каждый из которых содержит элемент И 4, элемент НЕ 5, коммутатор 6, регистр 7, элемент ИЛИ 8, элемент И 9, элемент НЕ триггер 11, кодовые входы 12-14 устройства, разреглающий вход 15 устройст ва, запросные входы 16-18 устройства информационный выход 19, шифратор 20 элемент ИЛИ 21 и элемент НЕ-22. Устройство работает следующим образом. Перед началом работы на регистр 7 через входы 12-14 заносится коды, которые совместно с коммутаторами 6 и элементами ИЛИ 8- обеспечивают начальное распределение запросов по приоритетам. По мере Необходимости распределение приоритетов может динамически изменяться, для этого достаточно изменить содержимое регистров 7 соответственно требуемому распределению запросов по приоритетам. Необходимые кодовые комбинации на регистрах 7 определяются по следующим правилам. 1.Регистр 7 самого старшего по Приоритету канала должен содержать код, равный номеру данного канала, обеспечивая подключение к выходу коммутатора 6 данного канала входа 15, подключенного к шине логического нуля Нуль на выходе коммутатора через эле.мент НЕ 5 разрешает прохождение запро су с входа 16 (или 17, 18) через И 4 данного канала на вход элемента И 9 этого канала. Кроме того, появление запроса на запросном входе данного канала вызывает последовательную блокировку обслуживания остальных, более младших по приоритету каналов,устройс ва через элемент ИЛИ 8 данного канала и через ко лмутаторы 6 и элементы ИЛИ остальных каналов. 2.Регистр 7каждого последующего младшего по приоритету канала должен содержать код, равный номеру предьщущего старшего по приоритету кангша. Например, регистр 7 для устройства, имеющего каналы 1-3, при распределении; (в порядке убывания) приоритетов 2,, 1, 3 должен.содержать следующие коды: Номер канала Код приоритет . Указанные коды в регистрах 7 формируют структуру устройства таким образом, что появление запроса в старшем по приоритету втором канале устройства блокирует обслуживание запросов, возникших на входах каналов 1и 3 устройства в порядке убывания приоритетов. Код, равный двум, в регистре 7 канала 2, самого старшего по приоритету, вызывает появление нулевого уровня на выходе коммутатора 6 канала 2 (так как второй вход коммутатора 6 соединен с входом 15) и через элемент НЕ 5 обеспечивает прохождение запросов через элемент И 4 канала 2на выход элемента И 9, открытого по второму входу элементом НЕ 22, а также обеспечивает установку в единичное состояние триггера 11, сигнал с единичного выхода которого поступает на соответствующий вход шифратора 20. Кроме того, на выходе элfeмeнтa ИЛИ 8 канала 2 при наличии запроса на входе 17 вырабатывается единичный сигнал, который блокирует через коммутатор 6 и элемент НЕ 5 канала 1 запрос с входа 16,так как код, равный двум, в регистре 7 кангща 1 подключает второй вход коммутатора к его выходу. Единичным сигналом с выхода элемента ИЛИ 8 канала 1 через первый вход коммутатора 6 и элемент НЕ 5 канала 3 блокируется обслуживание запроса, поступившего на вход канала 3, так как код, равный единице, в регистре 7 канала 3 подключает первый вход коммутатора 6 канала 3 к выходу этого коммутатора. Из комбинации сигналов на единичных выходах триггеров 11 (единичный сигнал всегда присутствует только на выходе одного триггера 11) шифратор. 20 формирует код номера приоритетного канала на выходе 19. Этот же код поступает на элемент ИЛИ 21, единичный сигнал с выхода . которого через элемент НЕ 22 запирает элементы И 9. При перемене порядка обслуживания запросов при новом распределении запросов по приоритетам/ возникший сигнал запроса в любом канале не пройдет через, соответствующий второйэлемент И 9 до тех пор (чтобы не было ложного кода номера канала на выходе шифратора , пока не будет отслужен запрос возникший до перемены порядка обслуживания запросов. После этого снятый с соответствующего запросного Входа сигнал уста навливает через второй элемент НЕ 1 .в нулевое состояние триггер 11. Нулевой сигнсШ с. выхода шифратора чере элемент ИЛИ 21 и элемент НЕ 22 раз решает прохождение возникшего сигнала запроса на выход шифратора 20. Дальнейшая работа устройства проходит аналогично. Отсутствие запроса на входе самого старшего по приоритету канала (в данном случае канала 2.) снимает последовательную цепь блокировок, всле ствие .чего появляется возможность удовлетворения возникаюадах запросов по запросным входам каналов 1 и 3. Применение изобретения позволяет расширить функциональные возможности устройства. Формула изобретения Многоканальное устройство приоритета, содержащее шифратор, выход которого является информационным выход устройства, каналы, а в каждом канале - первый элемент И, первый эле мент НЕ, элемент ИЛИ, регистр и коммутатор, причем каждый запросный вхо устройства соединен с первыми входами первого элемента И и элемента ИЛИ соответствующего канала, выход перво го элемента НЕ кажцого канала соединен с вторым входом первого элемента И своего канала, каждый кодовый вход устройства соединен с входом регистра соответствующего канала, выход регистра канала соединен с информацион ным входом коммутатора своего канала выход коммутатора каждого канала соединен с входом первого элемента НЕ своего канала и с вт.орым входом элемента ИЛИ своего канала, выход элемента ИЛИ каждого канала соединен с соответствующими управляющими входами коммутаторов предыдущих и последующих каналов, разрешающий вход устройства соединен в каждом канале с управляющим входом KOMviyTaтора, соответствующиг номеру канала, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет возможности перемены порядка обслуживания запросов в любой момент времени, оно содержит элемент ИЛИ и элемент НЕ, а в каждом канале - триггер, второй элемент НЕ и второй элемент И, причем запросный вход устройства через второй элемент НЕ соответствующего канала соединен с нулевым входом триггера своего канала, первый вход второго элемента И каждого канала . соединен с выходом первого элементаИ своего канала, выход второго элемента И каждого канала соединен с единичным входом триггера своего канала, выход триггера каждого канала соединен с соответствующим входом шифратора, выход которого соединен с входом элемента ИЛИ, выход которого через элемент НЕ соединен с вторым входом второго элемента И каждого канала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 506854, кл. G 06 F 9/22,1974., 2.ABTOpcKqe свидетельство СССР 679982, кл. G 06 F 9/22, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1981 |

|

SU1012259A1 |

| Многоканальное устройство приоритета | 1977 |

|

SU679982A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1780087A1 |

| Многоканальное устройство для приоритетного обслуживания запросов | 1983 |

|

SU1111164A1 |

| Многоканальное устройство приоритетного обслуживания | 1986 |

|

SU1383356A1 |

| Многоканальное устройство приоритета | 1988 |

|

SU1580364A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| Многоканальное устройство динамического приоритета | 1981 |

|

SU970371A1 |

| Многоканальное устройство для обслуживания запросов со сменными кодами приоритетов | 1984 |

|

SU1180892A2 |

| Многоканальное устройство приоритета | 1985 |

|

SU1282128A1 |

Авторы

Даты

1982-09-30—Публикация

1981-01-12—Подача