(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ЩНАМИЧЕСКОГО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1780087A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1399746A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Электромузыкальный инструмент | 1984 |

|

SU1270785A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для приоритетного обслуживания запросов | 1981 |

|

SU955069A1 |

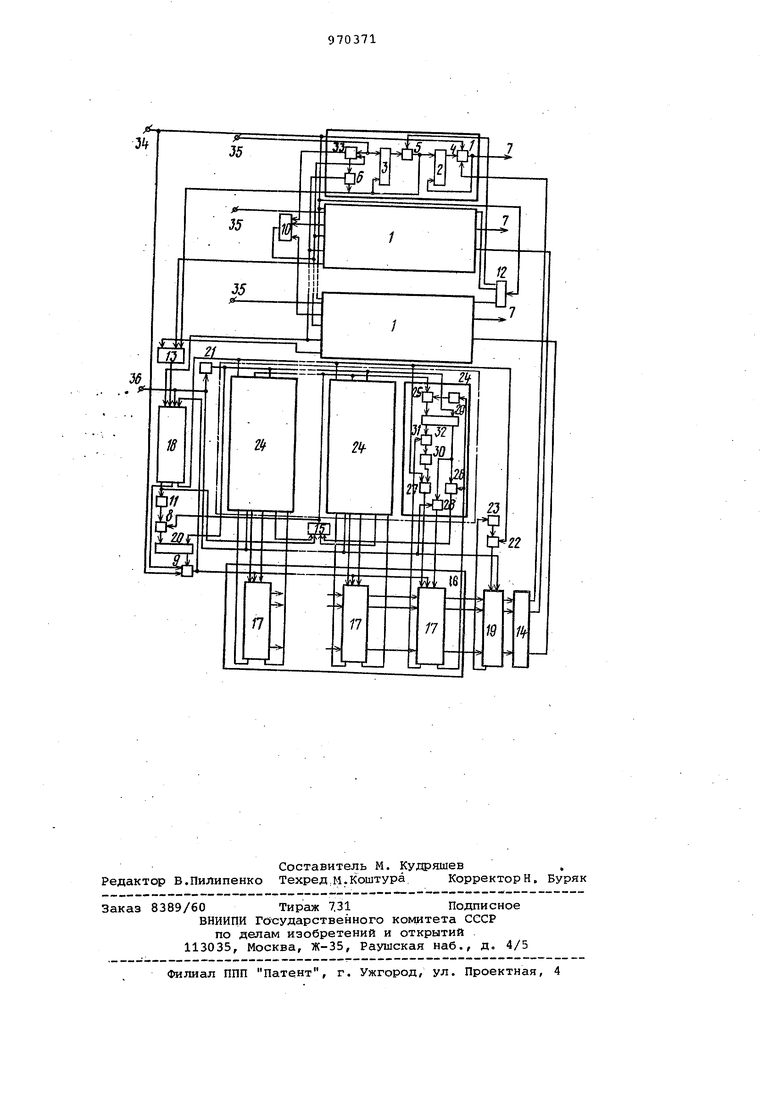

Изобретение относится к вычислительной технике, в частности к многоканальным устройствам приоритета, и может быть использовано при построении систем обработки данных. Известно многоканальное устройство приоритета, содержащее в каждом к нале первый и второй триггеры, четыр элемента И, элемент НЕ. Устройство обеспечивает запоминание и приоритет ное обслуживание запросов, поступающ независимо друг от друга от множества абонентов 1. Недостатком данного устройства яв ляется невозможность оперативного изменения приоритета номеров. Наиболее близким по технической сущности к предлагаемому является мн гоканальное устройство приоритета, содержащее в каждом канале два триггера, три элемента И, причем единичные выходы первого и второго триггеров каналов соединены с первыми входами соответственно первого и второг элементов И канала, выход второго эл мента И канала соединен с единичным входом первого триггера канала, выхо первого элемента И. канала является соответствующим разрешаннцим выходсял устройства, а также два элемента И, элемент ИЛИ и элемент НЕ 2. Недостатком известного устройства является то, что оно может работать только с абонентами, у которых приоритет задан жестко структурой устройства . При этсм структура не изменяется в процессе функционирования устройств, т.е. каналы имеют заранее обусловленный приоритет. Цель изобретения - расширение функциональных возможностей за счет адаптивной перестройки структуры устройства в зависимости от числа ранее выполненных опросов на обслуживание. Поставленная цель достигается тем, что в многоканальное устройство динс1мического приоритета, содержащее два элемента И, первый элемент ИЛИ, первый элемент НЕ и каналы, а в каждом канапе два триггера, три элемента И, причем единичные выходы первого и второго триггеров каналов соединены с первыми входами соответственно первого и второго элементов И своего канала, выход первого элемента И кгикдого канала является соответствующим разрешающим выходом устройства, выход второго элемента И каждого канала соединен с единичным входом первого триггера своего канала, введены распределитель импульсов шифратор, дешифратор, второй элемент ИЛИ, блок из п регистров (где п - чис ло каналов), два буферных регистра, триггер, элемент задержки, третий элемент И, второй элемент НЕ, пузлов управления, каждый из- которых содержит четыре элемента И, два элемента НЕ, элемент ИЛИ, триггер, а в каждом канале счетчик, причем тактовый вход устройства соединен с вторым входом первого элемента И каждого канала и С;,входом распределителя импульсов, третий вход первого элемента И каждо го канала соединен с соответствующим выходом дешифратора, выход первого элемента И каждого канала соединен fc нулевым входом первого триггера своего канала, второй вход второго элемента И каждого канала соединен с соответствукицим выходом распределителя импульсов, выход второго элемента И каждого канала соединен с первым входом третьего элемента И своего канала, с нулевым входом второго триггера своего канала и с соответствующим входом шифратора, запросные входы устройства соединег ны с единичными входами вторых триг1геров и со счетными входами счетчи.ков соответствующих каналов, выходы переполнения счетчиков всех каналов доединены с входами первого элемента ИЛИ, информационный выход счетчика каждого канала соединен со вторым входом третьего элемента И своего канала, выходы третьих элементов И всех каналов соединены с первым инфо мационным входом первого буферного регистра, вход разрешения устройства соединен с входом считывания первого буферного регистра, с первым входом первого элемента И каждого узла упра ления, с входом разрешения приема вт рого буферного регистра и через элемент задержки с единичными входами триггеров узлов управления и с нулевым входом триггера, выход первого элемента ИЛИ соединен с входом сброса счетчика каждого канала, выход шифратора соединен со вторым информа ционным входом первого буферного регистра, первый выход первого буфернрго регистра соединен с первым входом второго элемента ИЛИ и через э|1емент первый НЕ - с перВЕЛМ входом гаервого элементами, второй выход пер вого буферного регистра соединен с первым входом-первого элемента И, каждого узла управления-и с первьом входом второго элемента И, третий .выход первого буферного регистра сое динен с первым входом третьего элемента И, выход-первого элемента И соединение нулевым входом триггера, единичный выход триггера сое,цинен с вторым входом третьего элемента И, выход третьего элемента И соединен с первыми входами регистров блока регистров и с входом сброса первого буферного регистра, выход второго элемента ИЛИ соединен с первым входом второго элемента И узлов управления и со вторым входом первого элемента Hf первые выходы регистров блока регистров соединены с первыми входами третьих элементов.И и через элемент НЕ соответствующего узла управления со вторыми входами вторых элементов И соответствующих узлов управления, группа информационных выходов каждого i-ro регистра блока регистров соединена с группой информационных входов (i-«-1)-ro регистра блока регистров, информационные выходы блока регистров соединены с группой входов второго буферного регистра, выход второго буферного регистра соединен через второй элемент НЕ со вторым входом второго элемента И, выход второго элемента И соединен с входом сброса второго буферного регистра, вторые выходы регистров блока регистров соединены с первыми входами элементов ИЛИ соответствующих узлов управления, выход второго элемента И каждого узла управления соединен с нулевым входом триггера своего узла управления, единичный выход триггера каждого узла управления соединен со вторым входом третьего и первым входом четвертого элементов И своего узла управления, нулевой выход триггера каждого узла управления соединен с первым входом элемента ИЛИ блока управления, выход элемента ИЛИ каждЬго узла управления соединен через элемент НЕ своего узла управления со вторым входом первого элемента И своего узла управления, выходы вторых элементов И узлов управления соединены с входами со второго до (п+1)-го второго элемента ИЛИ, вь1ход четвертого элемента И каждого узла управления соединен со вторым входом соответствующего регистра блока регистров, выход первого элемента И каждого узла управления соединен с третьим входом соответствующего регистра блока регистров, информационные выходы второго буферного регистра соединены с входами дешифратора. На чертеже приведена структурная электрическая схема устройства. i Устройство содержит каналы 1, триггеры 2 и 3 канала, элементы И 4-6 канала, выход 7 разрешения устройства, элементы И 8, 9, элемент ИЛИ 10, элемент НЕ 11, распределитель 12 импульсов, шифратор 13, дешифратор 14, элемент ИЛИ 15, блок 16 регистров, регистры 17 блока 3,6, буферный регистр 18, буферный регистр 19, триггер 20, элемент 21 задержки, элемент И 22, элемент НЕ 23, узлы 24 управления, держащие элементы И 25-29, элемент :30, элемент ИЛИ 31, триггер 32, сче чик 33 канала 11, тактовый вход 34 устройства, запросные входы 35 устр :Ства, вход«36 разрешения устройства Устройство работает следующим об разом. Сигналы на разрешающих выходах 7 устройства появляются согласно очер ди, составленной в блоке 16 регистров. Распределитель 12 под воздейст вием тактовых импульсов с входа 34 опрашивает последовательно во време ни все каналы 1 устройства. Импульс запроса приходит на запросный вход 35 и запоминается в триггере 3. При очередном запросе канала 1 временны распределителем канал вы.г,ает информ цию о заявке в виде кода приоритета и номера канала 1, на который прише запрос, на первый буферный регистр 18. С помощью блоков 24 управления информация из буферного регистра 18 переписывается в один из регистров 17 блока 16 регистров или во второй буферный регистр 14. В зависимости . от кода приоритета формируется на счетчике 33 канала 1. Операция, простановки в очередь OC вана ла следующем алгоритме идентифи , кации максимума в наборе целых чисел Начиная слева, просматривается К-й разряд всех чисел. Если все разряды либо нули, либо единицы, то просто переходят к следующему разряду. Но если одни разряды - нули, а другие единицы, то jBce числа с нулями на данном месте вычеркиваются ив . дальнейшем это число не анализируПри переполнении счетчика 33 любо го канала 1 устройства импульс переполнения на его выходе устанавливает счетчики всех остальных каналов в ну левое состояние. Рассмотрим работу устройства более подробно. В исходном состоянии соответствую щими потенциалами с выходов триггеров 2 и 3 во всех каналах 1 устройст .ва закрыты соответственно элементы И 4 и 5, на счетчиках 33 каналов 1 находятся коды, соответствующие числ ранее выполненных заявок на обслуживание, соответствующим потенциашом с выхода триггера 32 во всех блоках управления 24 подготовлены к открытию .элементы И 26 и 28, потенциалом с выхода триггера 20 подготовлен к открытию элемент И 9, на вторых выходах тех регистров 17, в которых записана информация, единичный потенциал, потенциалом с выхода элемента НЕ 30 открыт элемент И 28 во всех блоках 24 управления, первый буферный регистр 18 обнулен, на втором буферном регистре находится информация о выполняемой заявке. Со входа 34 импульсы синхронизации по. ступают на входы элементов И 4 всех каналов 1, на вход элемента И 9 и на вход распределителя 12. При поступлении на вход 35 оди- . ночного импульса запроса он записывается в триггер 34, увеличивает содержимое счетчика 33 на единицу. Подготавливается к открытию элемент И 5. Очередной импульс от временного .распределителя через элемент И 5 записывается в триггер 2, поступает на соответствующий вход шифратора 13 и открывает элемент И б. Коды со счетчика 33 и шифратора 13 записываются в первый буферный регистр 18. По окончании записи сигналом с третьего выхода первого буферного регистра 18 открывается элемент И 9. Тактовые импульсы с выхода элемента И 9 поступают на входы регистров 17 и первого буферного регистра 18. Под воздействием этих тактовых импульсов со вторых выходов регистров 17 и с первого выхода первого буферного регистра начинают подаваться порязрядно коды приоритетов. ;С выходов регистров 17 они подаются на вход элементов И 26 и через элементы НЕ 29 на вход элементов И 25. С выхода первого буферного регистра 18 код поступает на элемент ИЛИ 15. Так в исходном состоянии все триггеры. 32 находятся в единичном состоянии и все элементы открыты.Следовательно, разряды с вторых В1т1ходов. регистров 17 проходят на элемент ИЛИ 15, на выходе которого состояние единица будет в случае, когда не все разряды нули. При состоянии единица на выходе элемента ИЛИ 15 триггер 20 и триггеры 32 установятся в нулевое состояние,, если на них поступил нулевой разряд кода, закрывая тем самым элемент И 9 или элементы И 26, 28 соответственно, После запирания элемента И 9 прекращается подача тактовых импульсов на регистры 17 и буферный регистр 18, т.е. прекращается подача кодов приоритетов на выходы регистров. В результате все элементы И 27 блоков 24 управления тех регистров 17, в которых код приоритета ниже, чем код приоритета в первом буферном регистре будут закрыты jfaK потенциалом с первого выхода регистров 17, так и потенциалом с выхода триггеров 32. Те элементы И 27 блоков 24 управления, соответствующие регистрам 17, в которых записан код приоритета выше, чем код приоритета, записанный в первом буферном регистре 18, закрыты только потенциалом с первого выхода регистров 17. Очередной импульс, поступающий на управляющий вход 36, проходит через элемент И 28 только тех блоков 24 управления, которые соответствуют регистрам 17, в которых записан код приоритета выше, чем код приоритета, находящийся на буферном регистре 18, поступ 1я на входы регистров 17 и производя после довательную передачу информации из регистра в регистр в сторону второго буферного регистра 19. В результате будет обнулен тот регистр 17, в который не была произведена передача и,з предыдущего регистра. На «jro втором выходе будет поэтому нулевой по тенциал. Схема И 27 блока 24 управле ния, соответствующая этому регистру будет открыта. Содержимое первого буферного регистра 18 перезаписывается через открытый элемент И 27 в освободившийся регистр 17.Если в первом буферном регистре 18 находится код приоритета, который выше всех приоритетов, находящихся , в регистрах 17, то информация переписывается из него через открытый элемент И 22 непосредственно но второй буферный регистр 19. После выпол нения этих операций импульс с выхода линии 21 задержки устанавливают в .единичное состояние триггеры 32 и триггер 20, подготавливая, устройство к очередному .циклу постановки заявки в очередь. При поступлении на второй буферный регистр 19 код номера канала, на который пришел запрос, подается на дешифратс р 14. Последний потенциалом на соответствующем выходе открывает схему И 4 ка нала 1, с которого пришла заявка. Очередной тактовый импульс проходит через элемент И 4 на разрешающий выход 7 устройства, а также на вход триггера 2, устанавливая его в нулевое состояние. В результате этого .канал 1 подготавливается к приему очередного запроса. Применение изобретения позволяет расширить функциональные возможности устройства за счет возможноста адаптивной перестройки структуры устройства в зависимости от числа ранее вьшолненных запросов. Формула изобретения Многоканальное устройство динамического приоритета, содержаще е два элемента И, первый элемент ИЛИ , первый элемент НЕ и каналы, в каждом канале два триггера, три элемента И причем единичные выходы первого и второго триггеров каналов соединены с первыми входами соответственно пер ,вого и второго элементов И своего (канала, выход первого элемента И каж дого канала является соответствующим разрешающим выходом устройства, выход второго элемента И каждого канала соединен с единичным входом первого триггера своего канала, отличающее ся тем, что, с целью расширения функциональных возможностей путем адаптивной перестройки структуры устройства в зависимости от числа ранее выполненных запросов на обслуживание, оно содержит распределитель импульсов, шифратор, дешифратор, второй элемент ИЛИ, блок из п регистров (где п - число каналов) , два буферных регистра, триггер, элемент задержки, третий элемент И, второй элемент НЕ, п узлов управления, каждый из которых содержит четыре элемента И, два элемента НЕ, элемент ИЛИ и триггер, а в каждом канале счетчик, причем тактовый вход устройства соединен с вторым входом первого элемента И каждого канала и с входом распределителя импульсов, третий вход первого элемента И каждого канала соединен с соответствующим выходом дешифратора, выход первого элемента И каждого канала соединен с нулевым входом первого триггера своего канала, второй вход второго элемента И кгикдого канала соединен с соответствующим выходом распределителя импульсов, выход второго элемента И каждого канала соединен с первым входом третьего элемента И своего канала, с нулевым вхЪдом второго триггера своего канала и с соответствующим входом шифратора, запросные входы устройства соединены с единичными входами вторых триггеров и с со счетными входами счетчиков соответствующих каналов, выходы переполнения счетчиков всех каналов соединены с входами первого элемента ИЛИ, информационный выход счетчика каждого канала соединен с вторым входом третьего элемента И своего канала, выходы третьих элементов И всех каналов соединены с первым информационным входом первого буферного регистра,вход разрешения устройства соединен с входом считывания первого буферного регистра, с первым входом первого элемента И каждого узла управления, с входом разрешения приема второго буфер регистра и через элемент задержки с единичными входами триггеров узлов управления и с нулевым входом триггера, выход первого элемента ИЛИ соединен с входом сброса счетчика каждого канала, выход шифратора соединен с вторым информационным входом ijtepBoro буферного регистра, первый выход первого буферного регистра соединен с первым входом второго элемента ИЛИ и через первый элемент НЕ - с первым входом первого элемента И, второй выход первого буферного регистра соединен с первым ВХОДОМ первого элемента И каждого узла управления и с первым входом вто рого элемента И, третий выход первого буферного регистра соединен с первым входом третьего элемента И, выход пер вого элемента И соединен с нулевым входом триггера, единичный выход триг гера соединен с вторым входом третьег элемента И, выход третьего элемента И соединен с. первыми входами регистров блока регистров .и с входом сброса первого буферного регистра, выход вто рого элемента ИЛИ соединен с первым входом второго элемента И узлов управ ления и с вторым входом первого элемента И, первые выходы регистров блока регистров соединены с первыми входами третьих элементов И и через элемент НЕ. соответствующего узла управления - с вторыми входами вторых элементов И соответствующих узлов управления, группа информационных выходов каждого i-ro регистра блока регастров соединена с группой информационных входов (i+1)-ro регистра блока регистров, информационные входы блока регистров соединены с группой входов второго буферного регистра, выход второго буферного регистра соединен через второй элемент НЕ с вторым входом второго элемента И, выход второго элемента И соединен с входом сброса второго буферного регистра, вторые выходы регистров блока регистров соединены с первыми входами элементов ИЛИ соответствующих узлов управления, выход второго элемента И каждого узла управления соединен с нулевым входом триггера своего узла управления, единичный выход триггера каждого узла управления соединен с вторым входом третьего и первым входом четвертого элементов И своего узла управления, нулевой выход триг;гера каждого узла управления соеди;нен с вторым входом элемента ИЛИ своего узла управления, выход элемента ИЛИ каждого узла управления .соединен через элемент НЕ своего узла управления с вторым входом первого элемента И своего узла управления, выходы вторых элементов И узлов управления соединены с входами с второго до ()-го второго элемента ИЛИ; выход четвертого элемента И каждого узла управления соединен с вторым входом соответствующего регистра блока регистров,выход первого элемента И кгикдого узла управления соединен с третьим входом соответствующего регистра блока регистров, информационные выходы второго буферного регистра соединены с входами дешифратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 363977, кл. G 06 F 9/46, 1972. 2.Авторское свидетельство СССР 652562, кл. G 06 F 9/46, 1977 (прототип).

Авторы

Даты

1982-10-30—Публикация

1981-02-03—Подача