Изобретение относится к области автоматики и вычислительной техники. Устройство может быть использовано, например, для согласования асинхронных сигналов, поступающих из ЦВМ, с тактовой частотой генератора периферийного устройства. Известно устройство для синхронизации импульсов по авт. св. № 544114, со дерокашее входной триггер, единичный выход которого соединен с первым входом первого элемента И, при этом второй вход последнего подключен к единичному входу входного триггера и к источнику управ ляющего сигнала, нулевой вход входного триггера соединен с выходом выходного элемента И, первый вход которого подклю чей к единичному входу второго триггера и к выходу первого элемента И, третий вход первого элемента И соединен с иоточником тактовых импульсов, единичный выход второго триггера соединен с вторым :входом выходного элемента И, выход дополнительного триггера соединен с нулевым входом второго триггера, а входы дополнительного триггера подключены соответственно к нулевому выходу второго триггера, к выходу первого элемента И и к третьему входу первого элемента И. Недостатками известного устройства являются искажение первого выходного синхронизированного импульса и наложение nepiBoro и второго выходных сигналов (наложение составляет 3t , где t - время задержки распространения сигнала на одном логическом элементе). Вышеизложенные недостатки явл5потся следствием того, что сброс первого выходного сигнала обусловлен появлением второго выходного сигнала. Наложение выходных сигналов сужает область применения устройства, так как оно не может быть использовано там, где требуются разнесенные во времени синхронизированные сигналы (например, в двухтактных схемах). Целью изобретения является повышение надежности устройства и расширение области его применения.

Для достижения этой цели в устройство введен инвертор, вход которого соединен с источником тактовых импульсов, а выход - с дополнительным входом выходного элемента И, выход которого подключен к третьему нулевому входу дополнительного триггера,

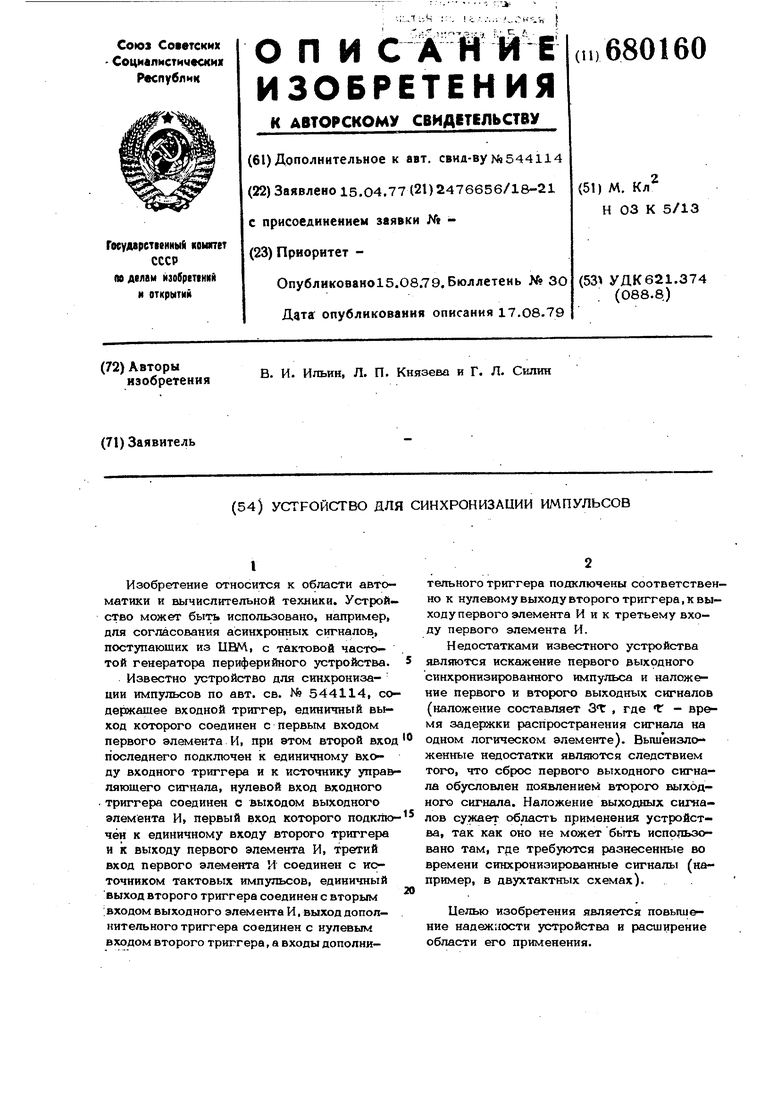

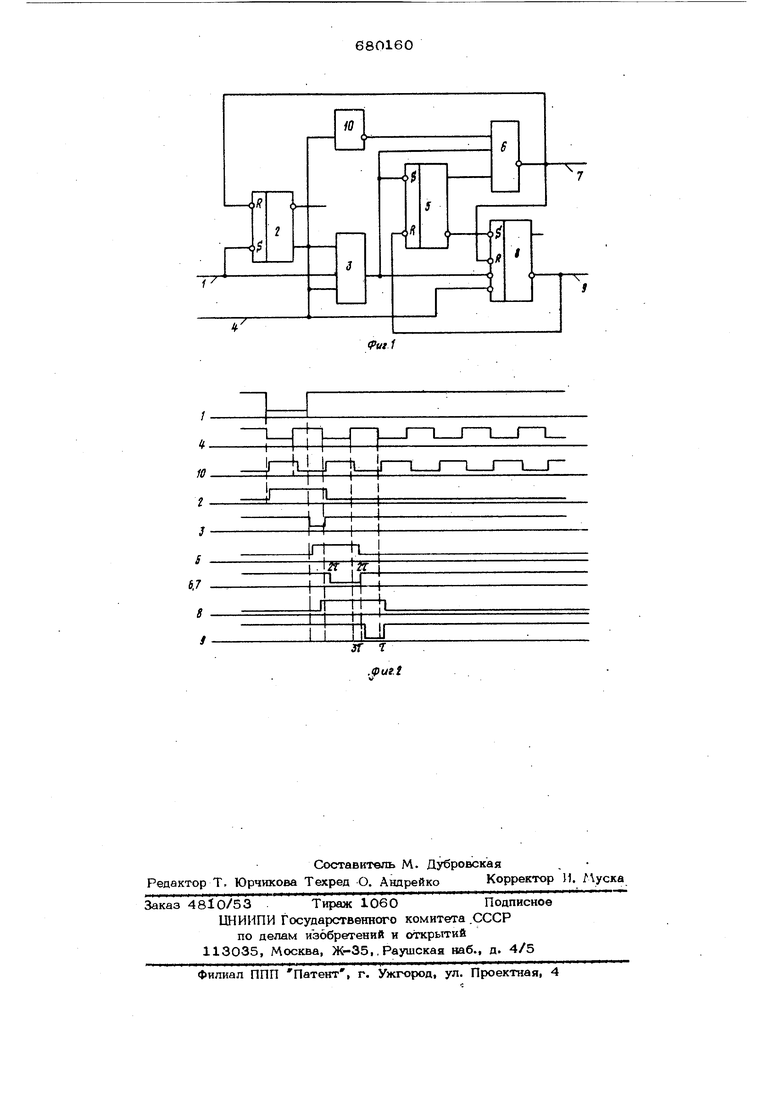

Блок-схвк а устройства представлена ца фиг. 1; временная диаграмма - на фиг. 2 (сигналы обозначены цифрами, соответствующими цифрам на фиг. 1).

Устройство реализовано на потенциальных элементах и содержит шину 1 управляющего сигнала, подключенную к едини ному входу входного триггера 2 и входу элемента И 3, другой вход которого связан с единичным выходом входного триггера 2, третий - с шиной 4 тактовых импульсов, а выход - с eдиничньnv входом триггера 5 и входом выходного элемента И 6. Выход последнего соединен с нул&вым входом триггера 2, с выходом 7 первого синхронизированного сигнала и с нулевым входом дополнительного триггера 8. Второй вход выходного элемента И под ключей к единичному выходу триггера 5, нулевой выход которого соединен с единичным входом исполнительного триггера 8. Нулевой триггера 8 подключен к выходу 9 второго синхронизированного сиг-. нала и к нулевому входу триггера- 5. Дру«гой нулевой вход дополнительного соединен с выходом элемента 1-1 3, третий ™ с шиной 4 тактовьгх импульсов и с входом инвертора 10, выход которого под- . ключей к дополнительному входу элемента И 6. .

Временная диаграмма показыва эт работу устройства в положительной логике.

При высоком уровнр входного на шине 1 триггеры 2, 5 и 8 обнулены сигналами шины 4 тактовых импульсов . через элементы И 3 и 6.

Низкий уровень источника упрб1.вляющего сигнала взводит триггер 2, но запрешает дальнеЛиее распространение сигнала с выхода этого триггера через элемент Н 3.

Появление на шине 1 высокого уровня сигнала разрешает прохождение тактового импульса через элемент И 3. Возникающий при прохождении тактового 1тмпульса низкий уровень напряжения на выходе элемента И 3 запирае элемент И 6, yjj.epживая тем самым высокий уровень сигна™ да iia выходе 7 первого синхрониз5фованного сигнала навязывает высокий уро™ вень напряжения на нулевом выходе триггера 8 (выход 9 второго синхронизированного сигнала) и взводит триггер 5. По окончании тактового импульса низкий уровень напряжения на шине 4 удерживает высокий уровень сигнала на выходе 9 и через инвертор 10 и элемента И 3 и 6 передается на выход 7 первого синхрони- эированного сигнала, обнуляя при этом триггер 2, низкий уровень сигнала на выходе которого запирает элемент И 3 и Поддерживает в дальнейшем высокий уровень напряжения на втором входе триггера 8,

Второй тактовый импульс через инвертор 10 вызывает высокий уровень напряжения на выходе элемента И 6 (на выходе 7 первого синхронизированного сигнатла). С появлением высокого уровня на выходе 7 на всех нулевых входах триггера 8 устанавливаются высокие уровни сигнала. Наличие низкого уровня напряжения на его единичном входе (нулевой выход триггера 5) вызывает на его нулевом выходе низкий уровень сигнала, т.е. второй синхронизированный импульс может nos виться только после окончания второго сш«ронизированного сиг-нала. Низкий уровень сигнала на выходе 9 сбрасывает

триггер 5.

По окончании второго тактового импульса низкий уровень на шине 4 обнуляет ттриггер 8, устанавливая на синхронизированном выходе 9 высокий уровень напряжения. Устройство приходит в исходное -состояние.

Таким образом, при изменении входного сигнала на шине 1 с низкого уровня на высокий на выходах устройства возникают последовательно два импульса, которые не накладываются друг на друга.

Предложенное устройство по сравнению с извес1ным более надежно в работе, имеет более широкую область применения за счет разнесения по времени выходных импульсов и улучшения формы первого выходного импульса.

ф мула изобретения

Устройство для синхронизации импульгсов по авт. св. № 544114, отличающееся тем, что, с цеАю повышения надежности устройства и расширения области его применения, в него введен инвертор, вход которого соеди 1ен с источником тактовых имнульсов, а выход - с дополнительным входом выходного элемента И, выход которого подключен к нулевому входу дополнительного триггера.

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1978 |

|

SU790213A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU790224A1 |

| Формирователь импульсов | 1976 |

|

SU575767A1 |

| Устройство для синхронизации импульсов | 1975 |

|

SU544114A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU924840A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1800599A1 |

| Устройство синхронизации импульсов | 1990 |

|

SU1734199A1 |

| Формирователь синхронизированных импульсов | 1977 |

|

SU624357A1 |

| Формирователь импульсов | 1979 |

|

SU855964A2 |

| Формирователь импульсов | 1973 |

|

SU503351A1 |

Авторы

Даты

1979-08-15—Публикация

1977-04-15—Подача