Изобретение относится к импульсной технике и может быть использовано в дискретной автоматике и электроизмерительной аппаратуре, в частности в устройствах синхронизации сигналов цифровых вычисли- тельных машин.

Цель изобретения - расширение области применения путем обеспечения возможности автоматического управления фазой формируемого сигнала.

Цель достигается тем, что в устройство для формирования импульсных сигналов, содержащее N синхронных D-триггеров, объединенных в счетчик Джонсона таким образом, что управляющий вход каждого последующего разрядного триггера объединен с выходом предыдущего, а тактовые и обнуляющие входы разрядных триггеров объединены соответственно с тактовой и обнуляющей шинами, элемент И-НЕ, первый вход и выход которого соединены соответственно с выходом последнего и с управляющим входом первого разрядных триггеров, первый, второй и третий синх- ронные D-триггеры, инвертор, элемент задержки и элемент И-ИЛИ-НЕ, один из элементов И которого Снабжен двумя инверсными входами, первый.из которых подключен к управляющему входу триггера последнего разряда счетчика Джонсона, а второй - к первому входу второго элемента И элемента И-ИЛИ-НЕ, выход которого соединен с вторым входом элемента И-НЕ, управляющую шину, подключенную к тактовому входу первого синхронного D- триггера, обнуляющий вход которого подключен к инверсному выходу второго синхронного D-триггера, соединенного входом обнуления с выходом триггера послед- него разряда счетчика Джонсона, а через элемент задержки и через инвертор соответственно с тактовым входом второго и управляющим входом третьего синхронных триггеров, при этом третий триггер подклю- чен своими тактовым входом и выходом соответственно к тактовой шине и второму входу второго элемента И элемента И-ИЛИ- НЕ, а третьи входы элементов И элемента И-ИЛИ-НЕ объединены с прямым выходом второго синхронного триггера, управляющий вход которого подключен к выходу первого синхронного триггера, управляющий вход которого объединен с шиной постоянной логической Т, согласно изобретения введен четвертый синхронный D-триггер, управляющий вход которого подключен к выходу последнего разрядного триггера счетчика Джонсона, а тактоаый вход и выход- соответственно - к упрэвг.яющей шине и к

первому входу второго элемента И элемента И-ИЛИ-НЕ.

Введение четвертого синхронного D- триггера является признаком существенным, поскольку для определения направления изменения фазы необходим фазовый детектор, определяющий положение сигнала на управляющей шине по отношению к сигналу на выходной шине. Этот триггер выполняет функции фазового детектора. , . .

Выше указанные существенные признаки в научно-технической и патентной литературе, в данном конструктивном выполнении и взаимосвязи не выявлены, хотя применяемые элементы а технике встречаются, но они используются для других целей.

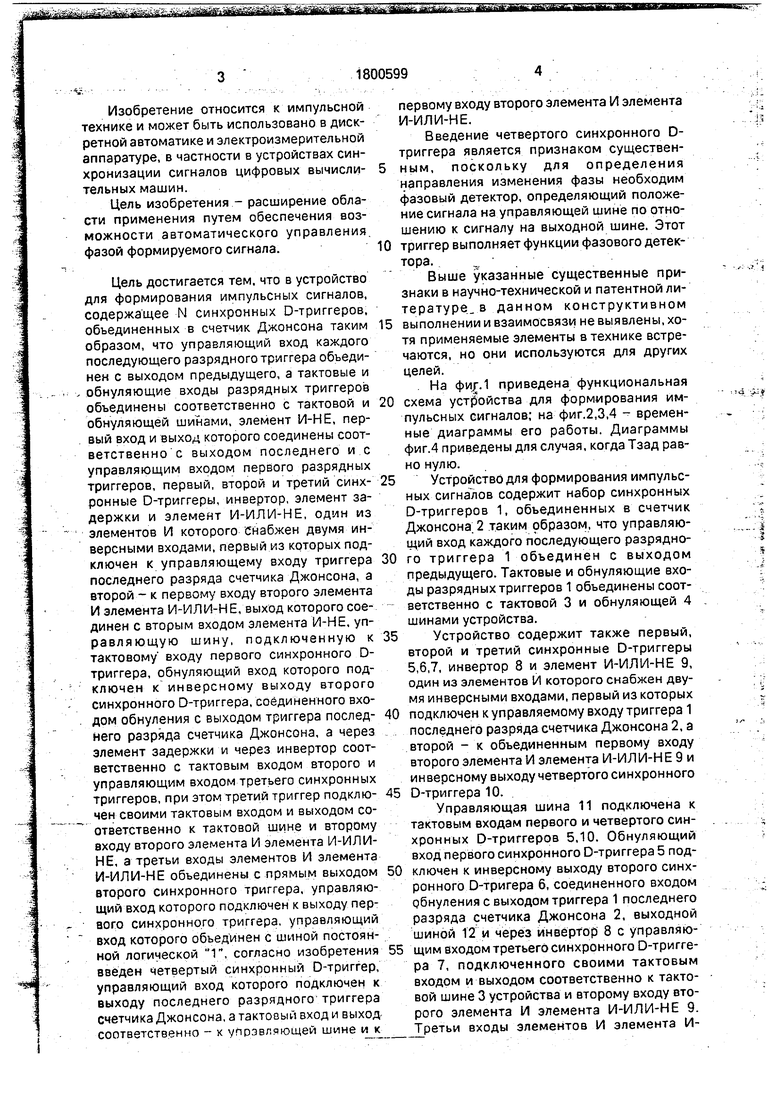

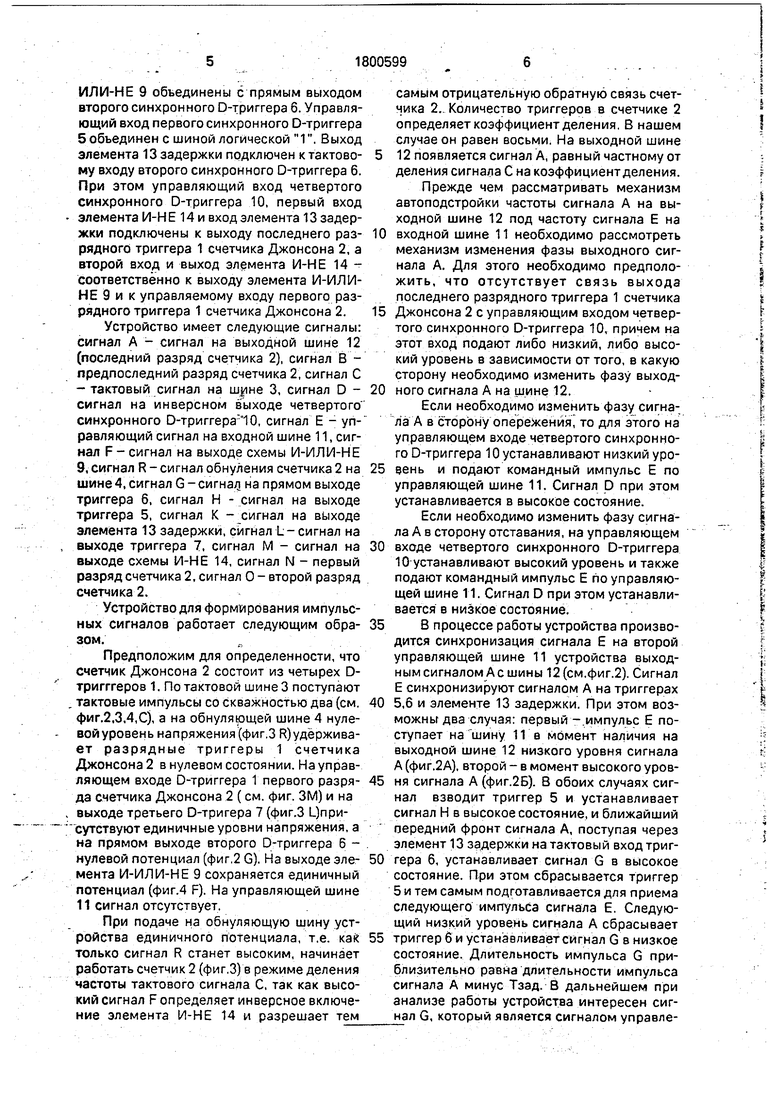

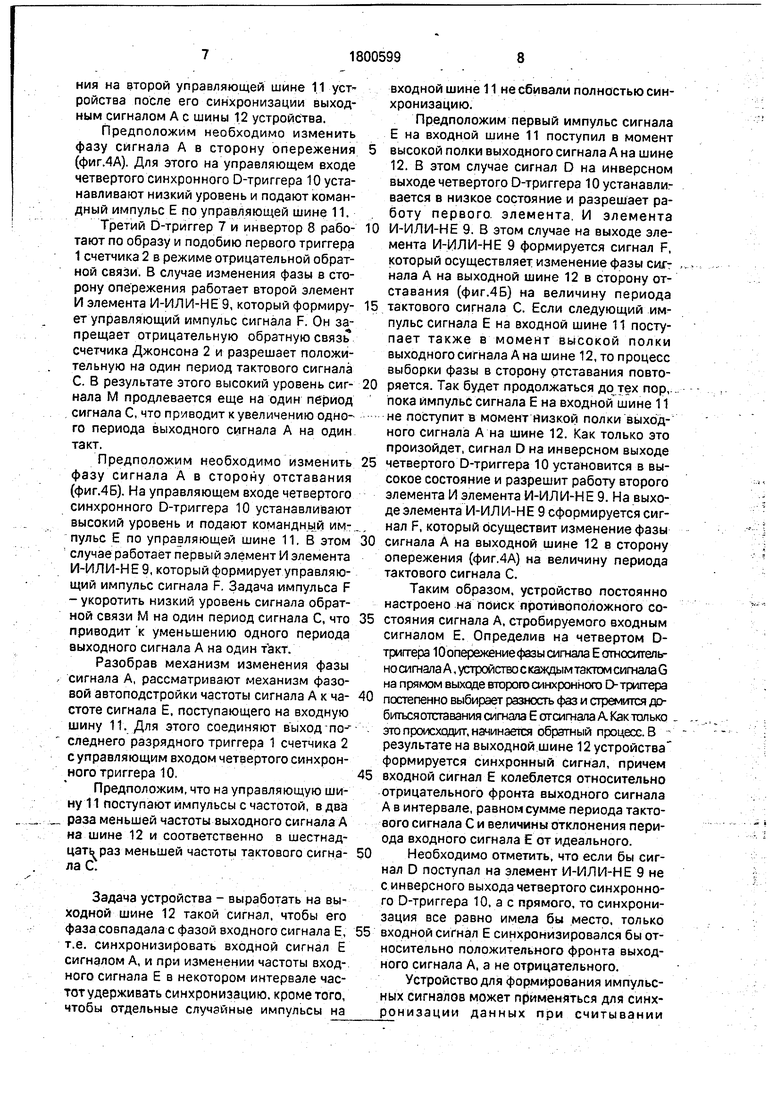

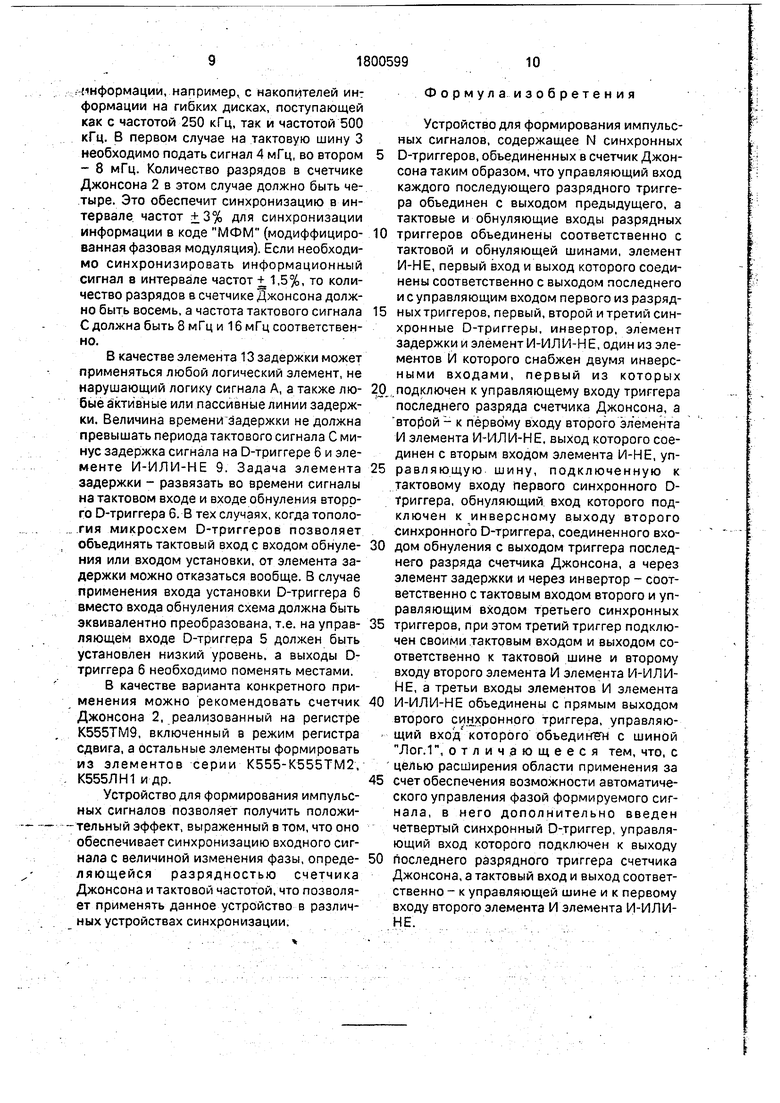

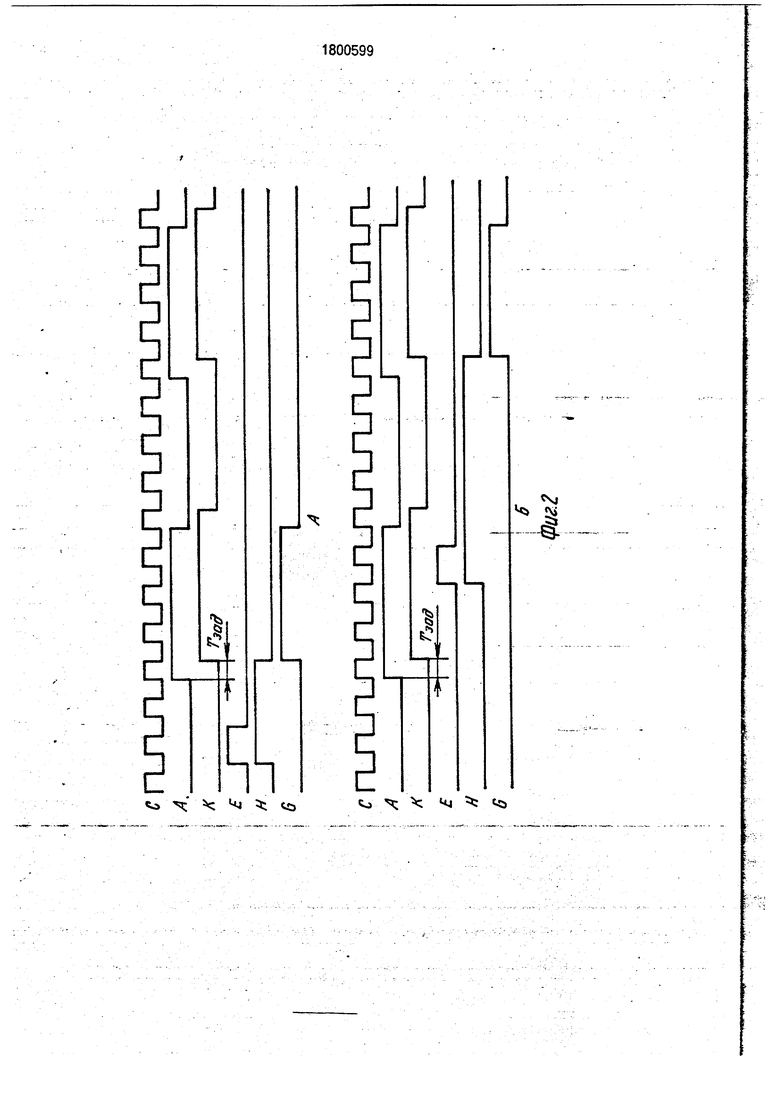

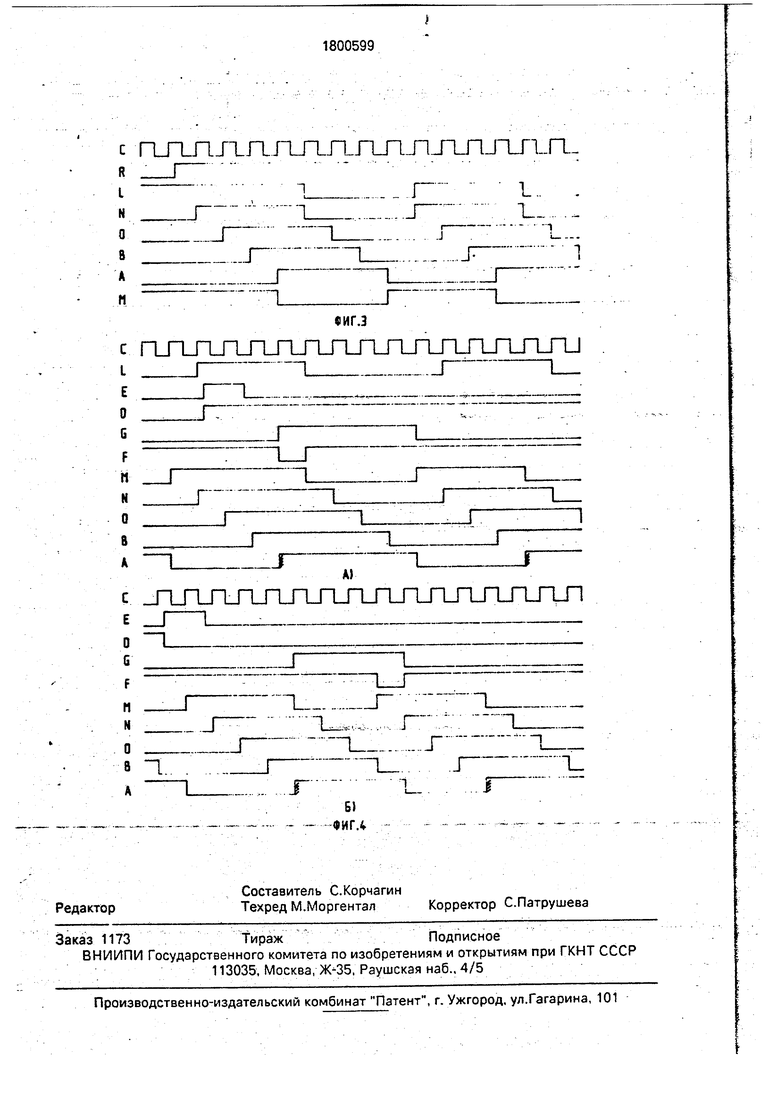

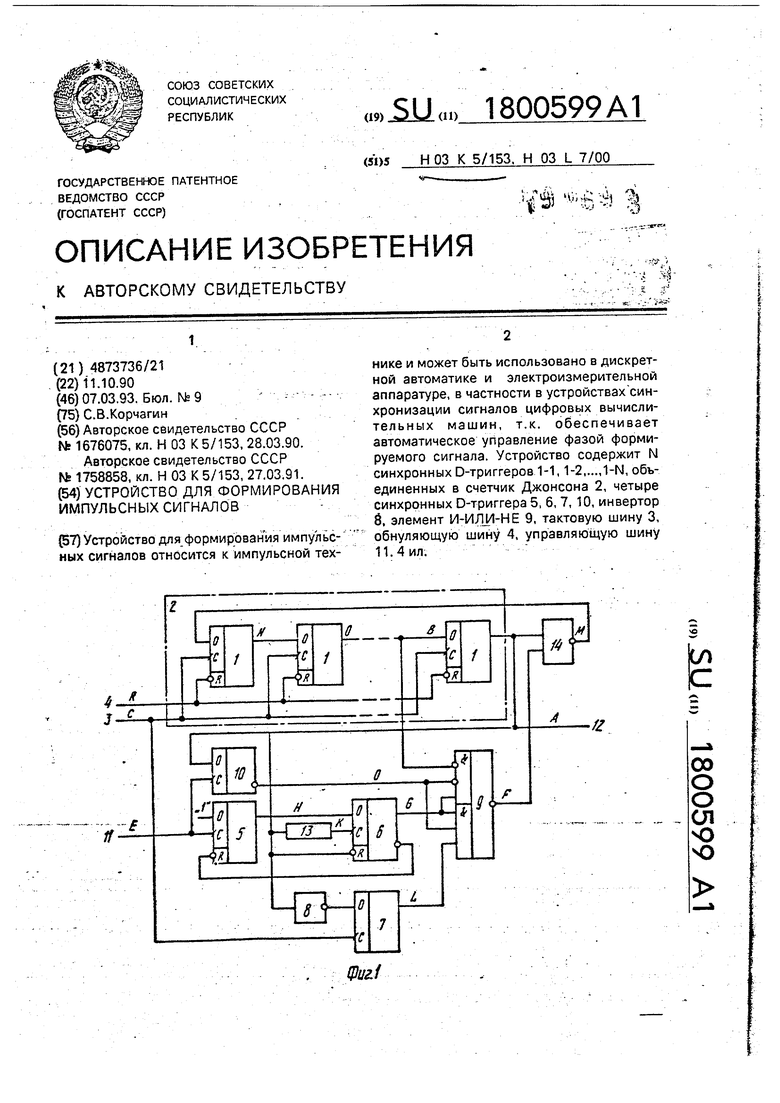

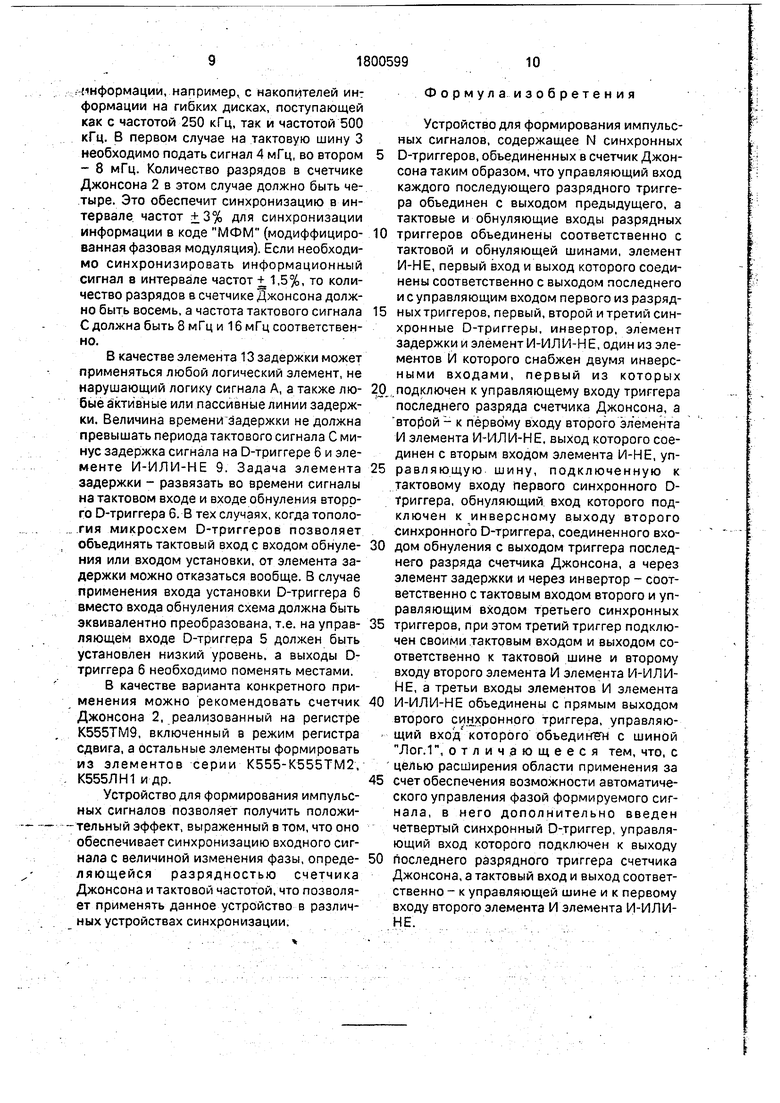

. На фиЈ.1 приведена функциональная схема устройства для формирования импульсных сигналов; на фиг.2,3,4 - временные диаграммы его работы. Диаграммы фиг.4 приведены для случая, когда Тзад равно нулю.

Устройство для формирования импульсных сигналов содержит набор синхронных D-триггеров 1, объединенных в счетчик Джонсона; 2 таким образом, что управляющий вход каждого последующего разрядного триггера 1 объединен с выходом предыдущего. Тактовые и обнуляющие входы разрядных триггеров 1 объединены соответственно с тактовой 3 и обнуляющей 4 шинами устройства.

Устройство содержит также первый, второй и третий синхронные D-триггеры 5,6,7, инвертор 8 и элемент И-ИЛИ-НЕ 9, один из элементов И которого снабжен двумя инверсными входами, первый из которых подключен к управляемому входу триггера 1 последнего разряда счетчика Джонсона 2, а второй - к объединенным первому входу второго элемента И элемента И-ИЛИ-НЕ 9 и инверсному выходу четвертого синхронного D-триггера 10.

Управляющая шина 11 подключена к тактовым входам первого и четвертого синхронных D-триггеров 5,10. Обнуляющий вход первого синхронного D-триггера 5 подключен к инверсному выходу второго синхронного D-тригера 6,соединенного входом обнуления с выходом триггера 1 последнего разряда счетчика Джонсона 2, выходной шиной 12 и через инвертор 8 с управляющим входом третьего синхронного D-триггера 7, подключенного своими тактовым входом и выходом соответственно к тактовой шине 3 устройства и второму входу второго элемента И элемента И-ИЛИ-НЕ 9. Третьи входы элементов И элемента И

ИЛИ-НЕ 9 объединены с прямым выходом второго синхронного D-триггера 6. Управляющий вход первого синхронного D-триггера 5 объединен с шиной логической 1. Выход элемента 13 задержки подключен к тактово- му входу второго синхронного D-триггера 6. При этом управляющий вход четвертого синхронного D-триггера 10, первый вход элемента И-НЕ 14 и вход элемента 13 задержки подключены к выходу последнего раз- рядного триггера 1 счетчика Джонсона 2, а второй вход и выход элемента И-НЕ 14 - соответственно к выходу элемента И-ИЛИНЕ 9 и к управляемому входу первого разрядного триггера 1 счетчика Джонсона 2.

Устройство имеет следующие сигналы: сигнал А - сигнал на выходной шине 12 (последний разряд счетчика 2), сигнал В - предпоследний разряд счетчика 2, сигнал С - тактовый сигнал на 1цине 3, сигнал D - сигнал на инверсном выходе четвертого синхронного О-триггера О, сигнал Е - управляющий сигнал на входной шине 11, сигнал F- сигнал на выходе схемы И-ИЛИ-НЕ 9, сигнал R-сигнал обнуления счетчика 2 на шине 4, сигнал G - сигнал, на прямом выходе триггера 6, сигнал Н - сигнал на выходе триггера 5, сигнал К - сигнал на выходе элемента 13 задержки, сигнал L- сигнал на выходе триггера 7. сигнал М - сигнал на выходе схемы И-НЕ 14, сигнал N - первый разряд счетчика 2, сигнал О - второй разряд счетчика 2.

Устройство для формирования импульсных сигналов работает следующим обра- зом.

Предположим для определенности, что счетчик Джонсона 2 состоит из четырех D- тригггеров 1. По тактовой шинеЗ поступают тактовые импульсы со скважностью два (см. фиг.2.3,4,С), а на обнуляющей шине 4 нулевой уровень напряжения (фиг.3 R) удерживает разрядные триггеры 1 счетчика Джонсона 2 в нулевом состоянии. На управляющем входе D-триггера 1 первого разря- да счетчика Джонсона 2 (см. фиг. ЗМ) и на выходе третьего D-тригера 7 (фиг.З присутствуют единичные уровни напряжения, а на прямом выходе второго D-триггера 6 - нулевой потенциал (фиг,2 G). На выходе эле- мента И-ИЛИ-НЕ 9 сохраняется единичный потенциал (фиг.4 F). На управляющей шине 11 сигнал отсутствует.

При подаче на обнуляющую шину устройства единичного потенциала, т.е. как только сигнал R станет высоким, начинает работать счетчик 2 (фиг.З) в режиме деления частоты тактового сигнала С, так как высокий сигнал F определяет инверсное включение элемента И-НЕ 14 и разрешает тем

самым отрицательную обратную связь счетчика 2.. Количество триггеров в счетчике 2 определяет коэффициент деления. В нашем случае он равен восьми. На выходной шине 12 появляется сигнал А, равный частному от деления сигнала С на коэффициент деления.

Прежде чем рассматривать механизм автоподстройки частоты сигнала А на выходной шине 12 под частоту сигнала Е на входной шине 11 необходимо рассмотреть механизм изменения фазы выходного сигнала А. Для этого необходимо предположить, что отсутствует связь выхода последнего разрядного триггера 1 счетчика Джонсона 2 с управляющим входом четвертого синхронного D-триггера 10, причем на этот вход подают либо низкий, либо высокий уровень в зависимости от того, в какую сторону необходимо изменить фазу выходного сигнала А на шине 12.

Если необходимо изменить фазу сигнала А в сторону опережения, то для этого на управляющем входе четвертого синхронного D-триггера 10 устанавливают низкий уровень и подают командный импульс Е по управляющей шине 11. Сигнал D при этом устанавливается в высокое состояние.

Если необходимо изменить фазу сигнала А в сторону отставания, на управляющем входе четвертого синхронного D-триггера 10 устанавливают высокий уровень и также подают командный импульс Е по управляющей шине 11. Сигнал D при этом устанавливается в низкое состояние.

В процессе работы устройства производится синхронизация сигнала Е на второй управляющей шине 11 устройства выходным сигналом А с шины 12(см.фиг.2), Сигнал Е синхронизируют сигналом А на триггерах 5,6 и элементе 13 задержки. При этом возможны два случая: первый-.импульс Е поступает на шину 11 а момент наличия на выходной шине 12 низкого уровня сигнала А (фиг.2А), второй - в момент высокого уровня сигнала А (фиг.2Б). В обоих случаях сигнал взводит триггер 5 и устанавливает сигнал Н в высокое состояние, и ближайший передний фронт сигнала А, поступая через элемент 13 задержки на тактовый вход триггера 6, устанавливает сигнал G в высокое состояние. При этом сбрасывается триггер 5 и тем самым подготавливается для приема следующего импульса сигнала Е. Следующий низкий уровень сигнала А сбрасывает триггер б и устанавливает сигнал G в низкое состояние. Длительность импульса G приблизительно равна длительности импульса сигнала А минус Тзад. В дальнейшем при анализе работы устройства интересен сигнал G, который является сигналом управления на второй управляющей шине 1.1 уст ройства после его синхронизации выходным сигналом А с шины 12 устройства.

Предположим необходимо изменить фазу сигнала А в сторону опережения (фиг.4А). Для этого на управляющем входе четвертого синхронного D-триггера 10 устанавливают низкий уровень и подают командный импульс Е по управляющей шине 11.

Третий Ь-триггер 7 и инвертор 8 рабо- тают по образу и подобию первого триггера 1 счетчика 2 в режиме отрицательной обратной связи. В случае изменения фазы в сторону опережения работает второй элемент И элемента И-ИЛИ-НЕ 9, который формиру- ет управляющий импульс сигнала F. Он запрещает отрицательную обратную связь счетчика Джонсона 2 и разрешает положительную на один период тактового сигнала С. В результате этого высокий уровень сиг- нала М продлевается еще на один период сигнала С, что приводит к увеличению одного периода выходного сигнала А на один такт.

Предположим необходимо изменить фазу сигнала А в сторону отставания (фиг.4Б). На управляющем входе четвертого синхронного D-триггера 10 устанавливают высокий уровень и подают командный импульс Е по управляющей шине 11. В этом : случае работает первый элемент И элемента И-ИЛИ-НЕ 9, который формирует управляющий импульс сигнала F. Задача импульса F - укоротить низкий уровень сигнала обратной связи М на один период сигнала С, что приводит к уменьшению одного периода выходного сигнала А на один такт.

Разобрав механизм изменения фазы сигнала А, рассматривают механизм фазовой автоподстройки частоты сигнала А к ча- стоте сигнала Е, поступающего на входную шину 11. Для этого соединяют выход по- следнего разрядного триггера 1 счетчика 2 с управляющим входом четвертого синхронного триггера 10.

Предположим, что на управляющую шину 11 поступают импульсы с частотой, едва раза меньшей частоты выходного сигнала А на шине 12 и соответственно в шестнадцать раз меньшей частоты тактового сигна- лаС.

Задача устройства - выработать на выходной шине 12 такой сигнал, чтобы его фаза совпадала с фазой входного сигнала Е, т.е. синхронизировать входной сигнал Е сигналом А, и при изменении частоты входного сигнала Е в некотором интервале частот удерживать синхронизацию, кроме того, чтобы отдельные случайные импульсы на

входной шине 11 не сбивали полностью синхронизацию.

Предположим первый импульс сигнала Е на входной шине 11 поступил в момент высокой полки выходного сигнала А на шине 12. В этом случае сигнал D на инверсном выходе четвертого D-триггера 10 устанавливается в низкое состояние и разрешает работу первого, элемента. И элемента И-ИЛИ-НЕ 9. В этом случае на выходе элемента И-ИЛИ-НЕ 9 формируется сигнал F, который осуществляет изменение фазы сигнала А на выходной шине 12 в сторону отставания (фиг.4Б) на величину периода тактового сигнала С. Если следующий импульс сигнала Е на входной шине 11 поступает также в момент высокой полки выходного сигнала А на шине 12, то процесс выборки фазы в сторону отставания повторяется. Так будет продолжаться до тех пор,. пока импульс сигнала Е на входной шине 11 не поступит в момент низкой полки выходного сигнала А на шине 12. Как только это произойдет, сигнал D на инверсном выходе четвертого D-триггера 10 установится в высокое состояние и разрешит работу второго элемента И элемента И-ИЛИ-НЕ 9. На выходе элемента И-ИЛИ-НЕ 9 сформируется сигнал F, который осуществит изменение фазы сигнала А на выходной шине 12 в сторону опережения (фиг.4А) на величину периода тактового сигнала С.

Таким образом, устройство постоянно настроено на поиск противоположного состояния сигнала А, стробируемого входным сигналом Е. Определив на четвертом D- триггера 10 опережение фазы сигнала Е относительно сигнала А, устройство с каждым тактом сигнала G на прямом выходе второго синхронного D-триггера постепенно выбирает разность фаз и стремится добиться отставания сигнала Е отсигнала А Как только это происходит, начинается обратный процесс. В - результате на выходной шине 12 устройства формируется синхронный сигнал, причем входной сигнал Е колеблется относительно отрицательного фронта выходного сигнала А в интервале, равномсумме периода тактового сигнала С и величины отклонения периода входного сигнала Е от идеального.

Необходимо отметить, что если бы сигнал D поступал на элемент И-ИЛИ-НЕ 9 не с инверсного выхода четвертого синхронного D-триггера 10, а с прямого, то синхронизация все равно имела бы место, только входной сигнал Е синхронизировался бы относительно положительного фронта выходного сигнала А. а не отрицательного.

Устройство для формирования импульсных сигналов может применяться для синхронизации данных при считывании

-мнформации, например, с накопителей ин формации на гибких дисках, поступающей как с частотой 250 кГц, так и частотой 500 кГц. В первом случае на тактовую шину 3 необходимо подать сигнал 4 мГц, во втором

- 8 мГц. Количество разрядов в счетчике Джонсона 2 в этом случае должно быть четыре. Это обеспечит синхронизацию в интервале, частот i3% для синхронизации информации в коде МФМ (модиффициро- ванная фазовая модуляция). Если необходимо синхронизировать информационаый сигнал в интервале частот 1,5%, то количество разрядов в счетчике Джонсона должно быть восемь, а частота тактового сигнала С должна быть 8 мГц и 16 мГц соответственно.

В качестве элемента 13 задержки может применяться любой логический элемент, не нарушающий логику сигнала А, а также лю- быё активные или пассивные линии задержки. Величина времени задержки не должна превышать периода тактового сигнала С минус задержка сигнала на D-триггере 6 и элементе И-ИЛИ-НЕ 9. Задача элемента задержки - развязать во времени сигналы на тактовом входе и входе обнуления второго D-триггера 6. В тех случаях, когда топология микросхем D-триггеров позволяет объединять тактовый вход с входом обнуле- ния или входом установки, от элемента задержки можно отказаться вообще. В случае применения входа установки D-триггера б вместо входа обнуления схема должна быть эквивалентно преобразована, т.е. на управ- ляющем входе D-триггера 5 должен быть установлен низкий уровень, а выходы D- триггера 6 необходимо поменять местами.

В качестве варианта конкретного применения можно рекомендовать счетчик Джонсона 2, реализованный на регистре К555ТМ9, включенный в режим регистра сдвига, а остальные элементы формировать из элементов серии К555-К555ТМ2, К555ЛН1 и др.

Устройство для формирования импульсных сигналов позволяет получить положи- тельный эффект, выраженный в том, что оно обеспечивает синхронизацию входного сигнала с величиной изменения фазы, опреде- ляющейся разрядностью счетчика Джонсона и тактовой частотой, что позволяет применять данное устройство в различных устройствах синхронизации.

. Формула., изобретения

Устройство для формирования импульсных сигналов, содержащее N синхронных D-триггеров, объединенных в счетчик Джонсона таким образом, что управляющий вход каждого последующего разрядного триггера объединен с выходом предыдущего, а тактовые и обнуляющие входы разрядных триггеров объединены соответственно с тактовой и обнуляющей шинами, элемент И-НЕ, первый вход и выход которого соединены соответственно с выходом последнего и с управляющим входом первого из разрядных триггеров, первый, второй и третий синхронные D-триггеры, инвертор, элемент задержки и элемент И-ИЛИ-НЕ, один из элементов И которого снабжен двумя инверсными входами, первый из которых подключен к управляющему входу триггера последнего разряда счетчика Джонсона, а второй - к первому входу второго элемента И элемента И-ИЛИ-НЕ, выход которого соединен с вторым входом элемента И-НЕ, управляющую шину, подключенную к тактовому входу первого синхронного D- триггера, обнуляющий вход которого подключен к инверсному выходу второго синхронного D-триггера, соединенного входом обнуления с выходом триггера последнего разряда счетчика Джонсона, а через элемент задержки и через инвертор - соответственно с тактовым входом второго и управляющим входом третьего синхронных триггеров, при этом третий триггер подключен своими тактовым входам и выходом соответственно к тактовой шине и второму входу второго элемента И элемента И-ИЛИ- НЕ, а третьи входы элементов И элемента И-ИЛИ-НЕ объединены с прямым выходом второго синхронного триггера, управляющий вход которого объединен с шиной Лог.1, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности автоматического управления фазой формируемого сигнала, в него дополнительно введен четвертый синхронный D-триггер, управляющий вход которого подключен к выходу последнего разрядного триггера счетчика Джонсона, а тактовый вход и выход соответственно - к управляющей шине и к первому входу второго элемента И элемента И-ИЛИ- НЕ.

JJ

J

j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1758858A1 |

| Устройство для формирования импульсных сигналов | 1989 |

|

SU1676075A1 |

| Устройство корректировки фазы для схем синхронизации | 1989 |

|

SU1706037A1 |

| Блок управления многофазным импульсным стабилизатором напряжения | 1987 |

|

SU1467704A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| Устройство для задержки и формирования импульсов | 1988 |

|

SU1539979A1 |

| Устройство для контроля микропроцессорных систем | 1987 |

|

SU1425679A1 |

| Устройство для синхронизации @ -последовательности | 1985 |

|

SU1311000A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| Преобразователь кода во временной интервал | 1988 |

|

SU1672567A1 |

Устройство для формирования импульсных сигналов относится к импульсной технике и может быть использовано в дискретной автоматике и электроизмерительной аппаратуре, в частности в устройствах син- хронизации сигналов цифровых вычислительных машин, т.к. обеспечивает автоматическое управление фазой формируемого сигнала. Устройство содержит N синхронных D-триггеров 1-1,1-2,...,1-М, объединенных в счетчик Джонсона 2, четыре синхронных D-триггера 5, 6,7, 10, инвертор 8, элемент И-ИЛИ-НЕ 9, тактовую шину 3, обнуляющую шину 4, управляющую шину 11. 4 ил.

-

и

С

1

«о х Ч 4i tЈ,to Ч 4i : ki

t

i о

-4

з

| Устройство для формирования импульсных сигналов | 1989 |

|

SU1676075A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1758858A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-07—Публикация

1990-10-11—Подача