(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

I

Изобретение относится к импульсной технике и может использоваться в системах обработки дискретной информации, например, в системах управления для выработки последовательности управляющих сигналов.

Известен формирователь одиночных импульсов, синхронизироЕанных тактовой частотой, содержащий два триггера и три элемента И-НЕ 1,

Недостатком этого устройства являются ограниченные функциональные возможности, так как оно формирует только один импульс, синхронизированный паузой тактовой частоты, и е обеспечивает получения дополнительных выходных импульсов, распределенных на несколько направлений и сдвинутых один относительно другого на половину периода тактовой частоты.

Известно также устройство для синхронизации импульсов, содержащее первый триггер, единичный выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого подключен к единичному входу первого триггера и к источнику управляющего сигнала, а нулевой вход первого триггера соединен с выходом

второго элемента И-КЕ, первый вход которого подключен к единичному входу второго триггера и к выходу первого элемента И-НЕ, третий вход которого соединен с источником тактовых импульсов, при этом единичный выход второго триггера соединен со вторым входом второго элемента И-НЕ, а вхо,цы третьего триггера подклкзче10 ны соответственно к нулевому выходу второго триггера, к выходу первого элемента И-НЕ и к третьему входу первого элемента И-НЕ 2.

Недостатком такого устройства

J5 также являются узкие функциональные возможности в связи с тем, что оно формирует только два импульса, синхронизированных импульсом и паузой тактовой частоты, и не позволяет получить дополнительные выходные импульсы, распределенные на несколько направлений со сдвигом друг относительно друга на половину периода : тактовой частоты.

25 Цель изобретения - расширение

функциональных возможностей устройства.

Указанная цель достигается тем, что в устройство для синхронизации

30 ммпульсов, содержащее первый тригep, выход которого соединен с первЕлм входом первого элемента , второй вход которого подключен к диничному входу первого триггера, улевой вход которого соединен с вы- ходом второго элемента И-НЕ, первый вход которого подключен к единичному входу второго триггера и к выходу ервого элемента , третий вход которого соединен с нулевым входом ретьего триггера, а инверсный выход ретьего триггера подключен к нулевому входу второго триггера, прямой ыход .которого соединен со-вторым ходом второго элемента И-НЕ,/дополительно введены N последовательно включенных инверторов и Ы последовательно соединенных триггеров, причем выход N-го инвертора соединен с нулевым входом третьего триггера, единичный вход которого под:5ключен к выходу второго элемента И-НЕ, инверсный выход третьего триггера соединен с единичным входом первого дополнительного триггера, а нулевые Входы каждого дополнител1 ного триггера подключены ко входам соответствующих инверторов в обратном порядке..

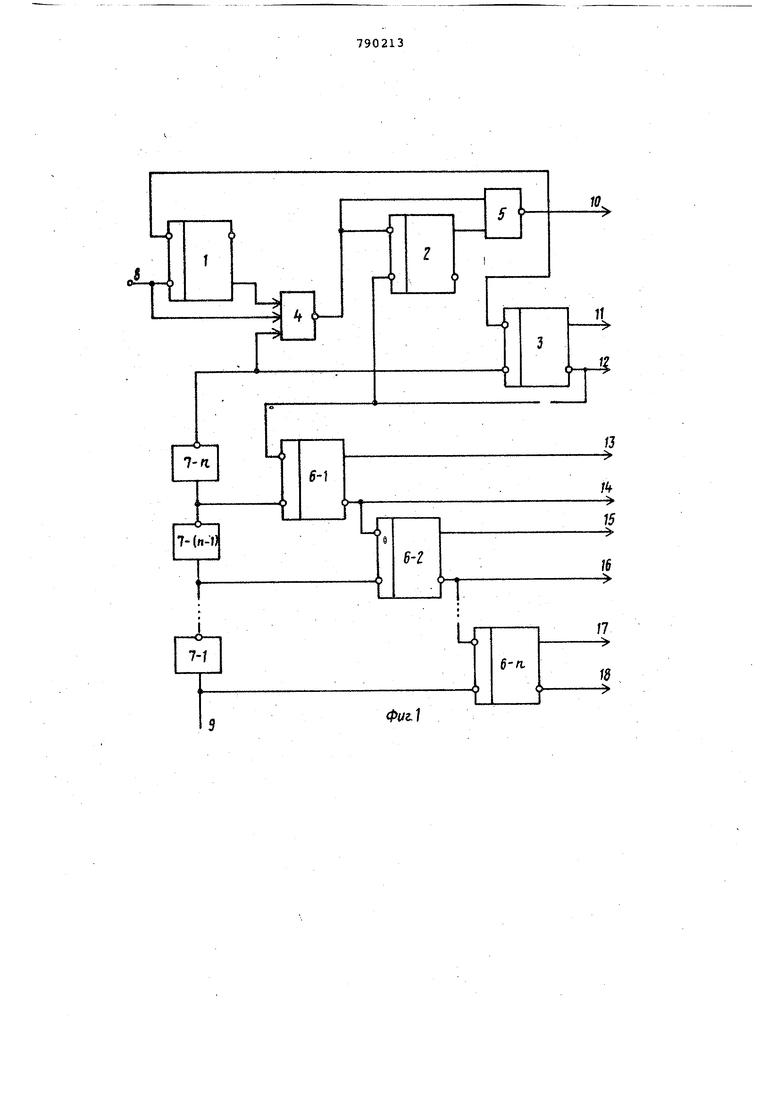

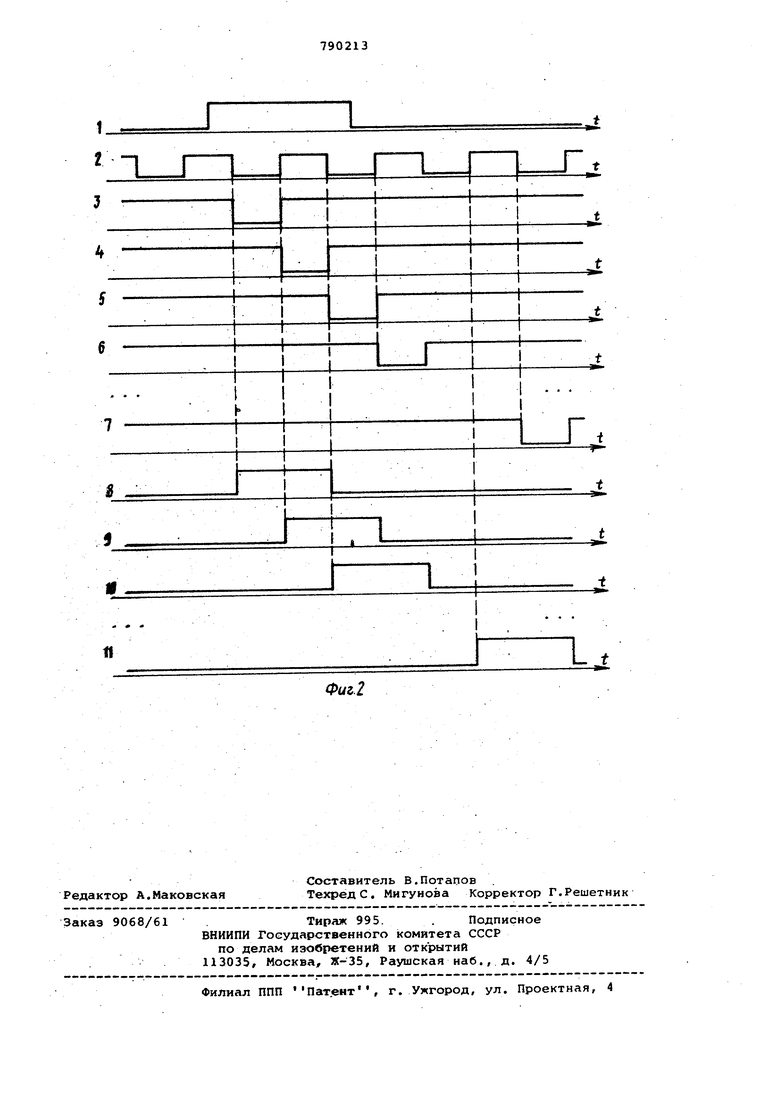

На фиг. 1 приведена электрическая схема предлагаемого устройства; на фиг. 2 - временные. диаграм1-«л, поясняющие принцип его работы.

Устройство для синхронизации импульсов содержит триггеры 1, 2 и 3, элементы совладения 4 и 5,Н дополнительных триггеров 6,14 инверторов 7, входную шину 8, шину 9 источника тактовых импульсов и выходные шины 10-18.

Входная шина 8 соединена с источником управляющего сигнала. Прямой выход первого триггера 1 соединен с первым входом первого элемента ИНЕ 4, второй вход которого подключен к единичному входу триггера 1 и ко входной шине 8.

Нулевой вход триггера 1 соединен с выходом второго элемента И-НЕ 5, первый вход которого подключен к единичному входу второго триггера 2 и к выходу элемента И-НЕ 4., Третий вход элемента И-НЕ 4 соединен с выходом Н го инвертора цепи 7 -Я и нулевым входом третьего триггера 3, единичный вход которого подключен к выходу элемента 5, Инверсный выход триггера 3 соединен с единичным входом первого дополнительного триггера 6-1 и с нулевым входом триггера 2, прямой выход которого подключен ко второму входу элемента 5. Инверторы 7 включены между собой в последовательную цепь. Вход инвертора 7 - п соединен с нулевым входом первого дополнительного триггера 6-1, инверсный ВЫХОДкоторого подключен к единичному входу следующего дополнительного триггера 6-2.

Вход инвертора 7-(f5-l) соединен с нулевым входом триггера 6-2, инверсный выход-которого подключен к единичному входу следующего триггера цепи, и т.д. Нулевой входН-го триггера 6-0, соединен со входом первого инвертора 7-1 и щиной 9.

Количество последовательно включенных инверторов и количество триггеров в цепочке выбирается в зависимости от числа выходных импульсов, которые требуется получить на выходных шинах.

Устройство для синхронизации импульсов работает следующим образом.

В исходном состоянии на входную шину 8 поступает низкий уровень напряжения, запрещающий прохождение импульсов тактовой частоты с шины 9 на выход элемента И-НЕ 4. Триггер

1находится в единичном, а триггер

2- в нулевом состоянии. На выходе элемента И-НЕ 5 присутствует высо-. кий уровень напряжения. Триггеры

3и 6 находятся в нулевом состоянии, т.е. на прямых вы.-одах этих триггеров присутствуют.низкие, а на ин5 30 версных выходах - высокие уровни напряжений. При этом на выходные щины 10, 12, 14, 16 н 18 поступают высокие уровни, а на выходные шины 11, 13, 15 и 17 - низкие уровни напряжений-.

Появление на шине 8 высокого уровня напряжения разрешает прохож9 35 дение импульса с шины 9 через цепочку инверторов (имеется в виду их четное количество) на выход элемента И-НЕ 4, в результате чего триггер 2 переключается в единичное состояние.. На выходе элемента И-НЕ 5 поддерживается высокий уровень напряжения, так как на первый вход этого элемента с выхода элемента И- НЕ 4 поступает низкий уровень напряжения.

При появлении паузы тактовой; частоты элемент И-НЕ 4 переключается

5 SO 55 в единичное, а элемент R-НЕ 5 - в нулевое состояние. На прямом выходе триггера 1 устанавливается низкий уровень напряжения, блокирующи элемент И-НЕ 4. Триггер 2 сохраня€;т своесостояние. На прямом выходе триггера 3 появляется высокий уровень напряжения, в то время каь: на его инверсном выходе поддерживается высокий уровень, так как на нулевой вход триггера 3 поступает низкий уровень с выхода инвертора 7-И„ 1 При поступлении следующего импульса тактовой Частоты на инверсном выходе триггера 3 по)вляется низкий уровень напряжения, который переключа0 65 ет триггер 2 в исходное нулевое состояние, а элемент И-НЕ 5 - в единичное состояние. Па прямом выходе триггера 3 при этом поддерживается высокий уровень напряжения.

Элемент И-НЕ 4 не пропуслЧает импульсы тактовой частоты, так как он заперт низким уровнем с выхода триггера 1, На прямом выходе триггера 6-1 устанавливается низкий уровень, в то время как на инверсном выходе этого триггера по,идерхивается высокий уровень, так как на нулевой вход триггера 6-1 поступает низкий уровень с выхода инвертора 7-(if1-l).

Появление Пр1узы тактовой частоты приводит к переключению триггеру 3 в исходное нулевое состояние. На инверсном выходе триггера 6-1 устанавливается низкий уровень напряжения, в то время как на прямом выходе триггера 6-1 поддерживается высокий уровень. На обоих выходах триггера 6-2 устанавливаются высокие уровни напряжений.

Появление на шине 8 низкого уровня переключает триггер 1 в исходное состояние.

При появлении очередного импульса тактовой частоты триггер 6-1 п реключается в исходное нулевое состояние, а на инверсномвыходе триггера 6-2 устанавливается низкий уровень напряжения. При этом на прямом выходе триггера 6-2 поддерживаеся высокий уровень напряжения.

После окончания импульса тактово частоты триггер 6-2 также переключается в исходное нулевое состояние. Далее все процессы повторяются до тех пор, пока не сформируется последний выходной импульс на выходе Н-го триггера.

Таким образом, на выходных шинах 10, 12, 14, 16 и 18 появляются импульсы с длительностью, равной половине периода следования импульсов тактовой частоты, а на выходных шинах 11, 13, 15 и 1-7 - импульсы с длительностью , равной периоду тактовой частоты, В обоих случаях выходные сигналы сдвинуты относительно друг друга на половину периода тактовой частоты.

Формула изобретения

Устройство для синхронизации импульсов, содержащее первый триггер, выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого подключен к eдиничнo v

o входу первого триггера, нулевой вход которого соединен с выходом второг/ элемента И-НЕ, первый вход которого подключен к единичному входу второго триггера и к выходу первого элемента

5 И-НЕ, третий вход которого соединен с нулевым входом третьего триггера, а выход третьего триггера под8сл10чен к нулевому входу второго триггера, прямой выход которого соединен со

0 вторым входом второго элемента И-НЕ отличающееся тем, что, с целью расширения функциональных возможностей устройс гва, в него дополнительно введены N последовательно включенных инверторов и J

5 последовательно соединенных триггеров, причем выход N-го. инвертора соединен с нулевым входом третьего трихгера, единичный вход которого подключен к выходу второго элемента

0 И-НЕ, инверсный выход третьего триггера соединен с единичным входом первого дополнительного триггера, а нулевые входы каждого дополнительного триггера подключены ко входам

5 соответствующих инверторов в обратном порядке.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР

0 552687, кл„ Н 03 К 5/13, 1976.

2,Авторское свидетельство СССР 9 544114, кл. Н 03 К 5/13, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1978 |

|

SU790224A1 |

| Устройство для синхронизации импульсов | 1987 |

|

SU1422377A2 |

| Устройство для формирования синхронизированных импульсов | 1981 |

|

SU1019610A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1982 |

|

SU1075392A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Устройство синхронизации импульсов | 1990 |

|

SU1734199A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| Устройство для формирования импульсных сигналов | 1989 |

|

SU1676075A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1800599A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU764112A1 |

Авторы

Даты

1980-12-23—Публикация

1978-10-09—Подача