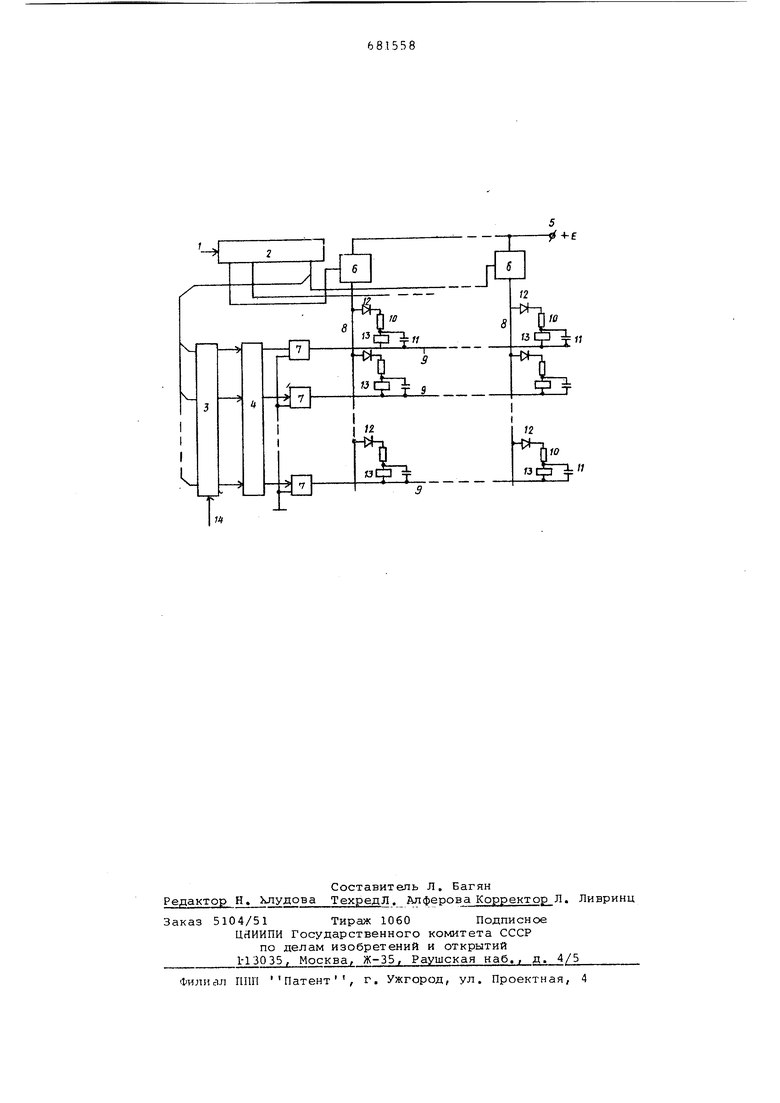

Изобретение относится к вычислительной технике и может быть исполь зовано в выходных, оконечных или ис полнительных устройствах репейного и электромагнитного типа. Известен матричный коммутатор,содержащий шины питания и управления, вертикальные и горизонтальные шины, соединенные в точках пересечения цепочкой из диода и резистора 1. Однако такое устройство не отличается быстродействием выполнения алгоритмов управления. Известен матричный-дешифратор,со держащий вертикальные и горизонталь ные шины полувыбора,подключенные к шинам питания через соответствующие переключат ели,адресные электромагниты, обмотка каждого из которых подклю чена к соответствующим вертикальным и горизонтальным шинам полувыбора че рез разделительный диод 2. Однако и это устройство не может обеспечить возмсжности одновременного управления произвольным количеством адресных электромагнитов, включаемых по произ.воЛьному закону. Это не позволяет использовать высокое аастродействие современных вычислительных и управляющих систем. Целью изобретения является повышение быстродействия выполнения алгорк-гмов управления. Для этого в матричный дешифратор содержащий вертикальные и горизонтальные шины полувыбора, подключенные к шинам питания через соответствующие переключатели, адресные электромагниты, обмотка каждого из которых подключена к соответствующим вертикальным и горизонтальным шинам полувыбора через разделительный диод, введены буферный регистр, накопитель, распределитель и конденсаторы, причем каждый из последних подключен к обмотке соответствующего адресного электромагнита, выходы распределителя подключены к соответствующим входам накопителя и управляющим входам переключателей вертикальных шин, полувыбора, а выходы накопителя через буферный регистр соединены с управлян) входс ми соответствующих переключателей горизонтальных шин полувыбора. На чертеже представлена принципиальная электрическая схема предлагаемого устройства. Устройство содержит шину 1 входных тактовых импульсов распределителя 2, накопитель 3 для записи, хранения и считывания управляющей информации, буферный регистр 4, шину 5 питания, переключатели б и 7 вертикальных и горизонтальных шин 8 и 9 попувыбора, соответственно, заряд ные резисторы 10, конденсаторы 11, разделительные диоды 12 и адресные электромагниты 13, Накопитель 3 име ет вход 14 для под&чи или смены управляющей информации. Устройство работает следующим об разом. При поступлении на шину 1 тактовых импульсов распределитель поочередно подключает шину 5 питания через переключатели 6 к вертикальным управляющим шинам 8, и при этом тот же распределитель соответствующим тактом считывает из накопителя 3 уп равляющее слово (хранится на время такта распределителя в буферном регистре 4) для управления через пере ключатели 7 соответствующим столбцом адресных электромагнитов. Таким образом, в каждом такте во буждается одна из вертикальных шин 8 палувыбора и те горизонтальные ши ны 9 полувыбора, на пересечении которых с упомянутой вертикальной шиной находятся адресные электромагни ты 13, которые в соответствии с информацией, заложенной в управляющетл слове, должны возбуждаться. Во врем такта конденсаторы 11 адресных элек ромагнитов 13, находящихся на Пересечении вертикальной шины полувыбора, возбуждаемой в рассматриваемом такте,и тех возбужденных горизонталь ных шин полувыбора, информация о возбуждении которых заложена в упра ляющем слове с адресом данного такта, заряжаются через небольшое сопр тивление резисторов 10. Далее распределитель 2 возбуждает следующую вертикальную шину полувыбора и считывает с накопителя соответствующее такту управляющее слово, возбуждая определенные горизонтальные шины. Так распределитель за время цикла Т возбуждает по очереди п вертикальных шин палувыбора , заряжая при этом емкости тех адресных электромагнитов, информация о возбуждении которых Зсшожена в соответствуюпдах каждому такту управляющих словах, В дальнейшем циклы все время повторяются, т.е. емкости адресных электро магнитов, которые должны включаться подзаряжаются один раз в каждом ци ле за время - . В паузе за время Т-- if (-1-J накопленный на емкости заряд поддерживает в сработан ном состоянии соответствующий.адресный электромагнит. При этом постоянная цепи заряда должна быть не менее, чем в-п раз меньше постоянной цепи разряда, чтобы узел из резистора 10, конденсатора 11 и адресного электромагнита 13 обеспечивал интегрирование управляющих импульсов (накопление заряда на емкости) и работоспособность устройства. Разделительные диоды 12 служат для предотвращения разряда конденсаторов 11 через низкоомные зарядные резисторы 10, Таким образом, предлагаемое устройство обеспечивает достаточно высокое быстродействие при одновременном управлении по произвольному закону произвольным количеством адресных электромагнитов. Формула изобретения Матричный дешифратор, содержащий вертикальные и горизонтальные щиныпалувыбора, подключенные к шинам питания через соответствующие переключатели, адресные электромагниты, обмотка каждого из которых подключена к соответствующим вертикальным и горизонтальным шинам полувыбора через разделительный диод, отличающий ся тем, что, с целью повышения быстродействия выполнения алгоритмов управления, введены буферный регистр, накопитель, распределитель и конденсаторы, причем каждый из последних подключен к обмотке соответствующего адресного электромагнита, выходы распределителя подключены к соответствующим входам накопителя и управляющим входам переключателей вертикальных шин полувыбора, а выходы накопителя через буферный регистр соединены с управляющими входами соответствующих переключателей горизонтальных шин полувыбора. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № 530459, кл, Н 03 К 17/74, 28,02.742, Авторское свидетельство СССР № 447834, кл, Н 03 К 13/243, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный дешифратор | 1973 |

|

SU447834A1 |

| Многоканальная телеизмерительная система | 1990 |

|

SU1783562A1 |

| Матричный дешифратор | 1980 |

|

SU875626A2 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| Релейный триггер | 1982 |

|

SU1051724A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Многоканальное устройство для последовательного управления агрегатами | 1982 |

|

SU1121648A1 |

| Релейный триггер | 1986 |

|

SU1401599A1 |

| Комплексно-комбинированный прибор для каротажа скважин | 1983 |

|

SU1087939A1 |

| Устройство для управления поляризованным дистанционным переключателем | 1973 |

|

SU668024A1 |

Авторы

Даты

1979-08-25—Публикация

1977-12-16—Подача