Изобретение относится к области вычислительной техники и может быть использовано при построении ферритовых запоминающих устройств 2,5D большой емкости.

Известны ферритовые запоминающие устройства (ЗУ), используемые в вычислительных системах в качестве оперативных запоминающих устройств и позволяющие выполнять некоторые операции с повышенным быстродействием. Эти устройства позволяют производить последовательное считывание нескольких бит, однако это достигается бла- ю годаря введению в накопитель дополнительной обмотки, с сердечниками для временного запоминания с последующей перезаписью 1.

Наиболее близким по технической сущности к предлагаемому является ферритовое запоминающее устройство 2,5D, содержащее накопитель с подключенными к нему усилителем воспроизведения и блоками адресно-разрядной и адресной выборки, од- jo норазрядный регистр числа, подключенный к усилителю воспроизведения, и блок управления. При работе этого устройства, в соответствии с кодом адреса, возбуждаются по

одному из выходов блоков адресно-разрядной и адресной выборки и организуются полутоки в соответствующих адресно-разрядной и адресной линиях накопителя. Причем полуток в адресно-разрядную линию при считыван11И необходимо подавать по сравнению с адресным полутоком с опережением тем большим, чем большее число полувыбранных сердечников вносят искажение в считываемый сигнал. Время работы устройства при выполнении операции «считывание-регенерация или «считывание-запись складывается из следующих величин (без учета фронтов токов и задержек в логических цепях).

Ти. Тр + 2Тп,

где Тр - время раздвижки между адресноразрядным и адресным током, Тп - время переключения сердечника при записи или считывании 23В современных вычислительных комплексах обмен информацией с оперативной памятью ведется в основном группами по несколько слов. При последовательном обращении за N к ЗУ соответственно в N раз возрастает время работы ЗУ:Ти, N(Tp4-2TnX

При большом объеме ЗУ непроизводительные потери времени NTp составляют значительную часть общего времени работы ЗУ. Если требуется произвести запись нескольких последовательных слов, надо последовательно считывать информацию в соответствующих сердечниках без ее распознавания.

Цель изобретения - повышение быстродействия устройства при выполнении операций с группами слов.

Поставленная целы достигается тем, что в запоминающее устройство, содержащее накопитель с подключенными к нему блоками выборки и блоком усилителей считывания, подключенным к регистру числа, блок управления и адресные шины, введены дополнительный регистр числа, счетчик и коммутатор, входы которого подключены к соответствующим выходам счетчика, блока управления и дополнительного регистра числа, один из входов которого соединен с выходом регистра числа, другие - с одними из выходов блока управления, другой выход которого соединен с выходом счетчика, выход коммутатора подключен к входу одного из блоков выборки.

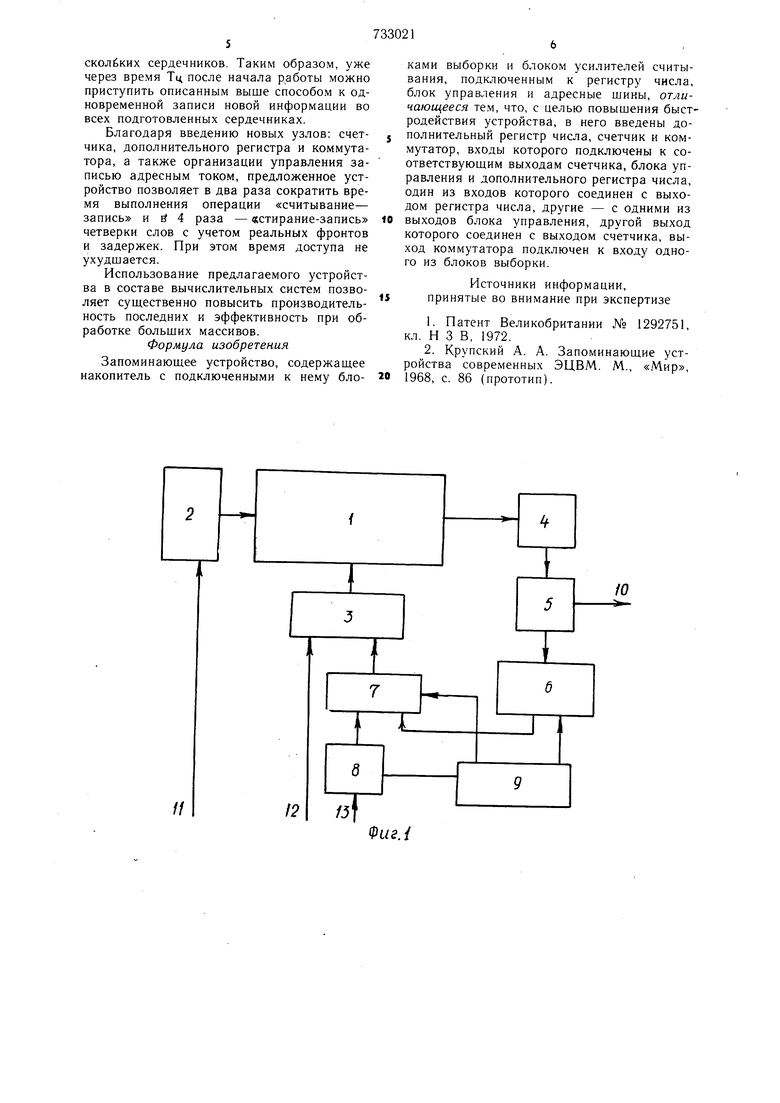

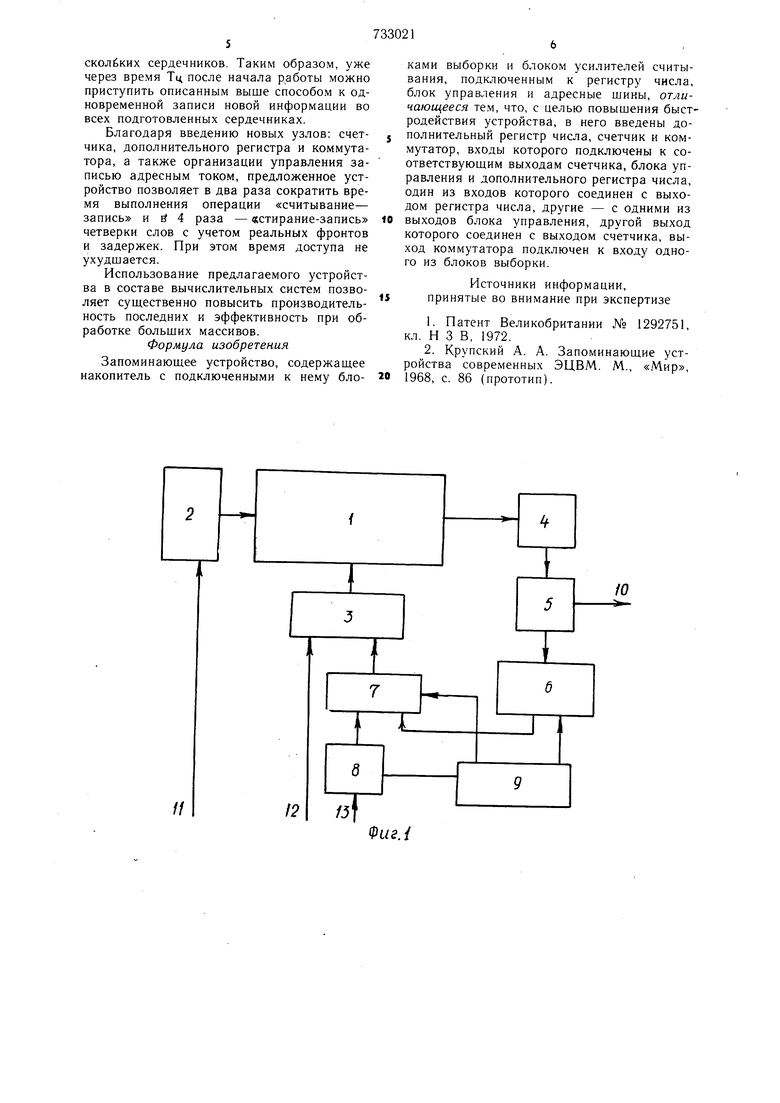

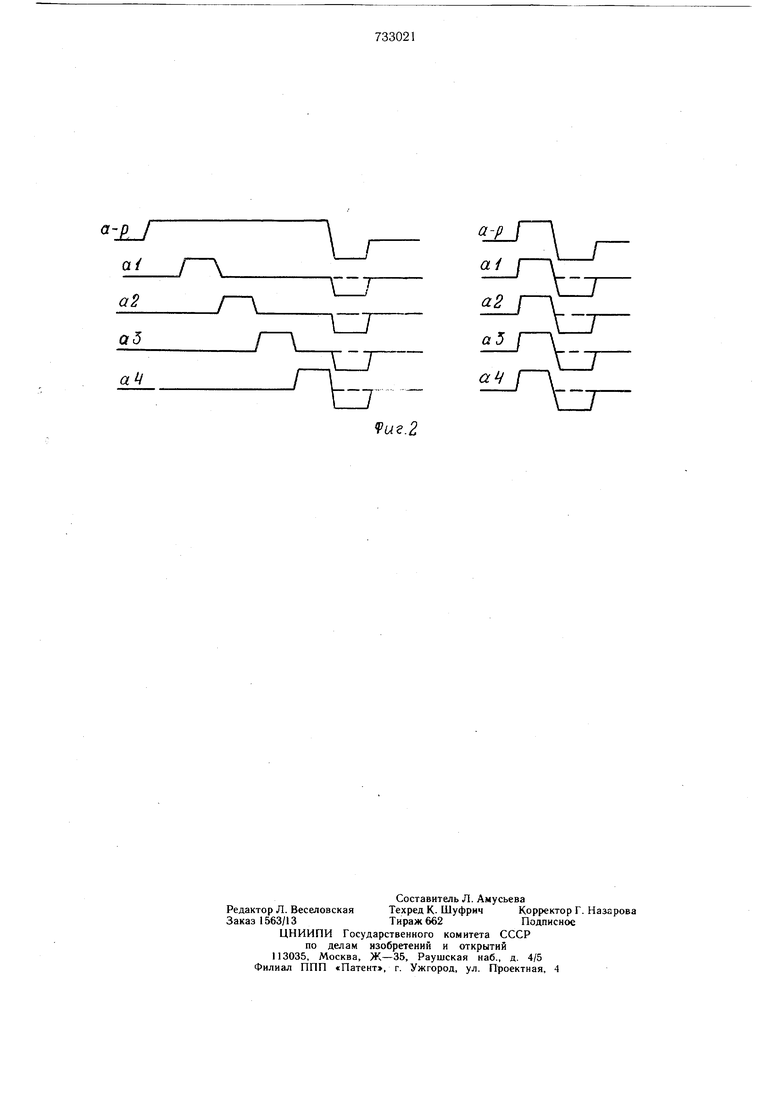

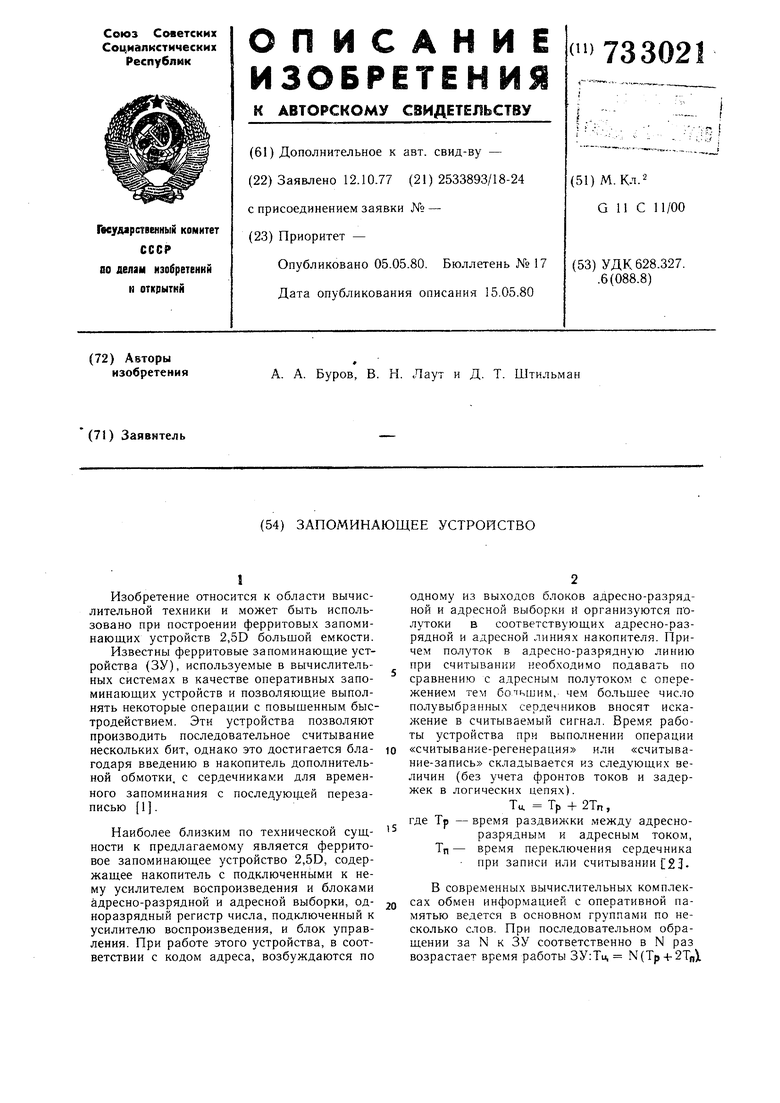

На фиг. 1 представлена блок-схема- запоминающего устройства; на фиг. 2 - временные диаграммы устройства.

Запоминающее устройство содержит накопитель 1, блок 2 адресно-разрядной выборки и блок 3 адресной выборки, усилитель 4 воспроизведения, одноразрядный регистр 5 числа, дополнительный регистр 6 числа, коммутатор 7, счетчик 8 последовательных обращений и устройство 9 управления. Считанная в устройстве информация и информация для задиси передаются по числовой щине 10 числа. По числовым шинам И, 12, 13 адреса поступает адрес обращения.

Устройство работает следующим образом. Старшие разряды адреса, поступающие по шине 11, управляют работой блока 2 адресно-разрядной выборки, обеспечивая выбор соответствующей адресно-разрядной шины накопителя 1. -Младшие разряды адреса, поступающие по щинам 12, 13, управляют работой блока 3 адресной выборки, обеспечивая выбор адресных шин накопителя 1. Считанная информация с усилителя воспроизведения 4 поступает на - одноразрядный регистр 5 числа и на выход устройства 10. Новая информация, поступивщая на регистр 5 числа с шины 10, или прежняя информация при регенерации через допол.нительный регистр 6 числа и коммутатор 7 определяют включение соответствующего ключа блока 3 адресной выборки, т. е. информационное состояние записываемого сердечника определяется адресным током. Устройство 9 управления обеспечивает необходимые временные управляющие сигналы.

При обращении к запоминающему устройству за N последовательными словами.

одновременно с командой «Пуск в устройство управления поступает признак групповой операции, а по шинам 11, 12, 13 поступает код адреса первого слова, младшими разрядами которого (щина 13) устанавливается исходное состояние счетчика 8. Это состояние счетчика 8, подключенного в это время через коммутатор 7 к блоку 3 адресной выборки, вместе с разрядами адреса, поступающими непосредственно в блок адресной выборки по шине 12, определяет выбор соответствующей адресной шины накопителя. В соответствии с принятым адресом возбуждается сначала адресно-разрядная шина накопителя, а затем через время Тр возбуждается адресная шина накопителя. С окончанием такта считывания устройством управления вык;1ючается адрес- . ный полуток в накопителе, при этом выключение адресно-разрядного полутока блокируется. Одновременно счетчик 8 переходит в следующее состояние и меняет с помощью

0 коммутатора 7 выход блока адресной выборки для возбуждения новой адресной линии накопителя, что приводит к считыванию информации со следующего сердечника, а также производится перенос информации для регенерации (или записи вновь поступившей) первого слова в первый разряд дополнительного регистра 7 числа, выполненного, например, в виде сдвигового регистра. Сразу за первым считыванием производится второе, т. е. без выжидания еще раз времени Тр, так как адресно-разрядный полуток оставался включенным. Аналогично производятся все остальные считывания: при переходе к кажддму следующему сердечнику происходит смена состояния счетчика 8 с одновременным переносом информации для за писи в соответствующие разряды дополнительного регистра 6 числа. После окончания считывания последнего слова осуществляется смена полярности полутока в адресно-разрядной щине накопителя и возбужд даются N выходов блока адресной выборки 3: при записи кода «1 соответствующий ключ открывается, а при записи кода «О - нет. Управление ключами определяется содержимым дополнительного регистра 6 числа. Таким образом, блоком адресной выборки обеспечивается одновременная запись в N сердечниках по адресным координатам накопителя. В результате время полного обращения за N словами равно

Тц, Тр + NTn -+- Тп .

При необходимости произвести запись 2- х 4-х, 8-ми или более слов в такте считывания устройство управления устанавливает нужное число разрядов дополнительного регистра 6 числа в состояние «1 и подключает его посредством коммутатора 7 к блоку 3 адресной выборки. Благодаря одновременному срабатыванию соответствующих ключей блока 3 адресной выборки происходит одновременное перемагничивание не5

скольких сердечников. Таким образом, уже через время Тч после начала работы можно приступить описанным выше способом к одновременной записи новой информации во всех подготовленных сердечниках.

Благодаря введению новых узлов: счетчика, дополнительного регистра и коммутатора, а также организации управления записью адресным током, предложенное устройство позволяет в два раза сократить время выполнения операции «считываниезапись и и 4 раза -«стирание-запись четверки слов с учетом реальных фронтов и задержек. При этом время доступа не ухудшается.

Использование предлагаемого устройства в составе вычислительных систем позволяет существенно повысить производительность последних и эффективность при обработке больших массивов.

Формула изобретения

Запоминающее устройство, содержащее накопитель с подключенными к нему блоками выборки и блоком усилителей считывания, подключенным к регистру числа, блок управления и адресные шины, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительный регистр числа, счетчик и коммутатор, входы которого подключены к соответствующим выходам счетчика, блока управления и дополнительного регистра числа, один из входов которого соединен с выходом регистра числа, другие - с одними из

выходов блока управления, другой выход которого соединен с выходом счетчика, выход коммутатора подключен к входу одного из блоков выборки.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании № 1292751, кл. Н 3 В, 1972.

2.Крупский А. А. Запоминающие устройства современных ЭЦВМ. М., «Мир,

1968, с. 86 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 :1 Т ВФОН]] Я-И;ф'РТГЩ <" t- J J^^ '^ • i .• f S .„ J i, is i* | 1972 |

|

SU433541A1 |

| Магнитное оперативное запоминаю-щЕЕ уСТРОйСТВО | 1979 |

|

SU841039A1 |

| Запоминающее устройство | 1971 |

|

SU479151A1 |

| Запоминающее устройство типа 2,5 д | 1976 |

|

SU607278A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

g-P, /

7

a/

r

Авторы

Даты

1980-05-05—Публикация

1977-10-12—Подача