ния режима двустороннего сдвига и етатичеекого хранения.

Поставленная цель достигается тем, что регистр сдвига, содержащий последовательно соединенные триггеры, каждый из которых выполнен на двух иоследовательно включенных туннельных диодах, один из которых подключены к шине нулевого потенциала, а другой к одной из управляющих щин, связанных с соответствующими выходами формирователя тактовых импульсов, щины синхроимпульсов и щины сдвига влево и вправо, содержит дополнительный триггер, выполненный на двух последовательно включенных туннельных диодах, один из которых соединен с шиной нулевого потенциала, а другой - с другой управляющей шиной, а входы формирователя тактовых импульсов соединены соответственно с шинами синхроимпульсов и сдвига влево и вправо, а также тем, что формирователь тактовых импульсов содержит два RS-триггера, входы которых соединены с выходами элементов И-ИЛИ, первые и вторые входы которых соединены с соответствующими входами формирователя тактовых импульсов, выходы RS-триггеров подключены к соответствующим выходам формирователя тактовых импульсов и третьим выходам элементов И-ИЛИ.

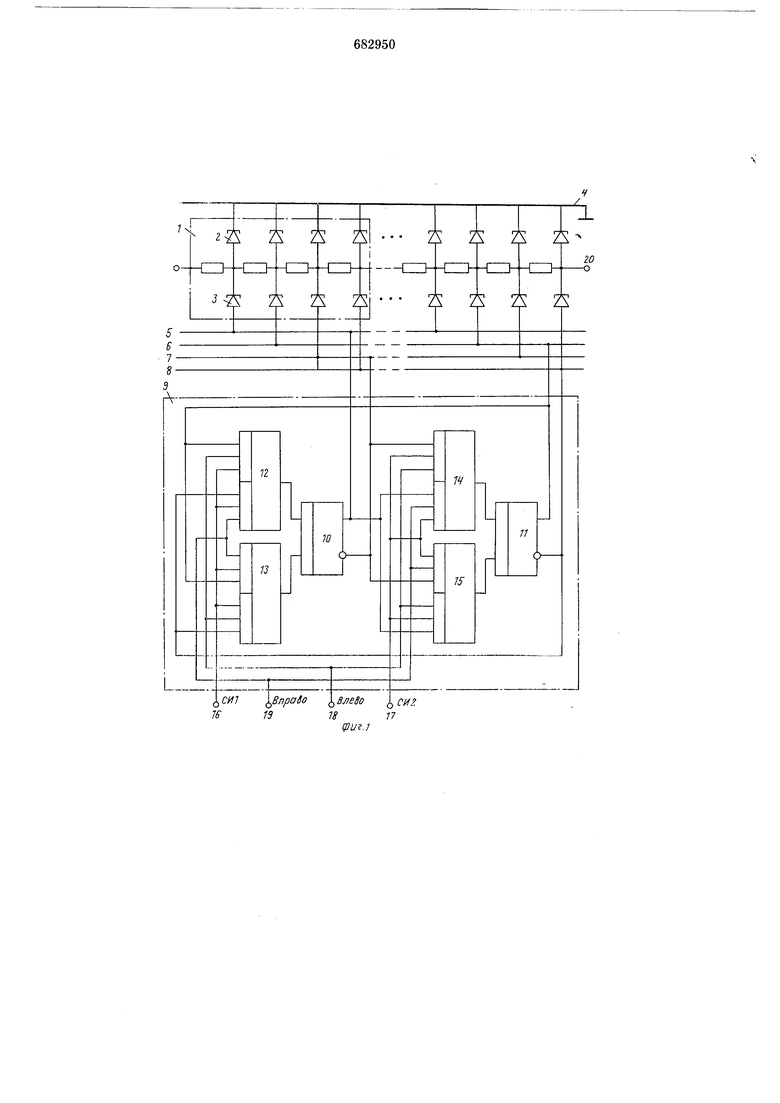

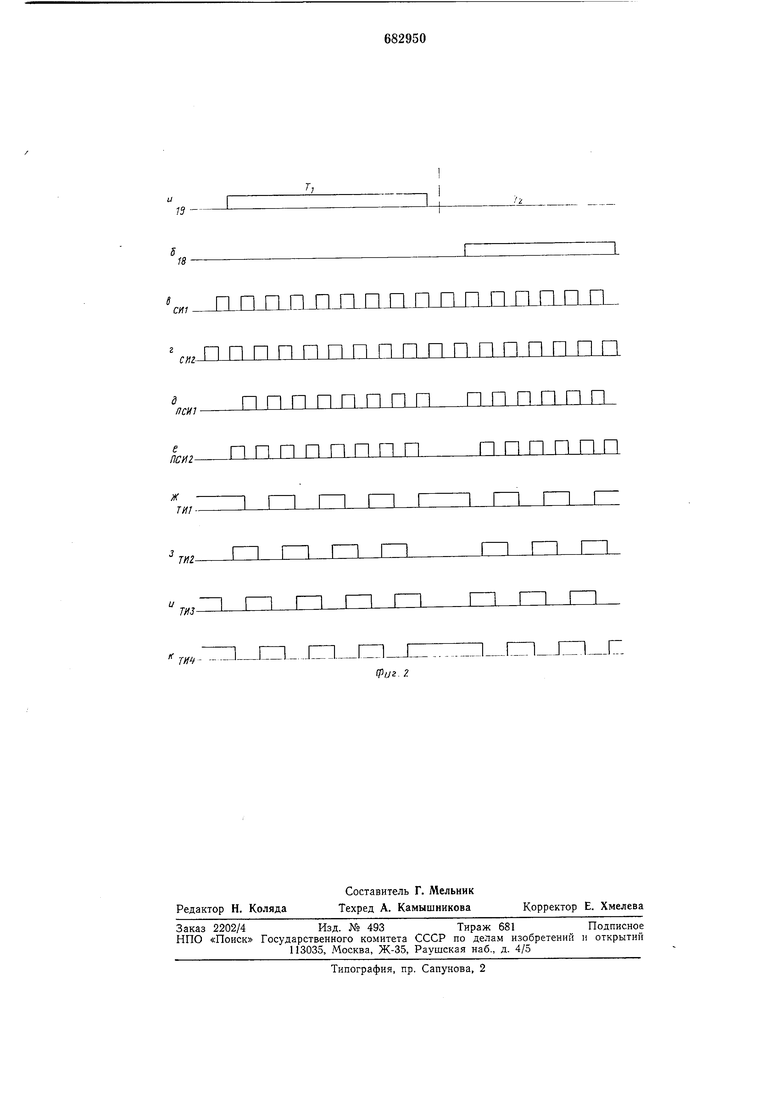

На фиг. 1 представлена схема предложенного регистра; на фиг. 2 - временная диаграмма работы формирователя.

Регистр содержит последовательно соединенные триггеры 1, выполненные на двух последовательно включенных туннельных диодах 2 и 3, причем диоды 2 подключены к шине 4 нулевого потенциала, диоды 3 - к соответствующим управляющим шипам 5-8, которые связаны с соответствующими выходами формирователя 9 тактовых импульсов, который состоит из двух RS-триггеров 10 и 11, входы которых соединены с выходами элементов И-ИЛИ 12, 13 и 14, 15. Шина синхронизации 16 и 17, и шина сдвига влево 18 и вправо 19, соединены со входами формирователя 9.

Формирователь 9 обеспечивает формирование тактовых импульсов на шинах 5-8 в требуемой последовательности при подаче одного из зправляющих сигналов «Вправо или «Влево. Формирование серий тактовых импульсов и сдвиг информации в регистре осуществляется при подаче одного из управляющих сигналов «Вправо или «Влево. Одновременная подача зказанных сигналов недопустима. При отсутствии обоих сигналов регистр обеспечивает статическое хранение ранее записанной информации. Синхронизация работы формирователя осуществляется двумя непрерывными сериями импульсов по шинам 16 и 17, сдвин тыми друг относительно друга на полпериода (фиг. 2, в, г).

При подаче сигнала «Вправо (фиг. 2, а, временной промежзток TI) на щину 19 единичный выход триггера 10 через элемент 14 подключается ко входу триггера 11, нулевой выход триггера 10 через элемент 15- ко входу триггера И, единичный выход триггера 11 через элемент 13 - ко входу / триггера 10, а нулевой выход триггера 11 через элемент 12 - ко входу 5 триггера 10.

Из непрерывных серий СИ1 и СИ2 по шинам 16 и 17 выделяются «пакеты импульсов ПСИ1 и ПСИ2 (фиг. 2, д, е), которые в течение временного интервала TI поступают на выходы триггеров 10 и 11. Поскольку формирователь 9 на триггерах 10 и 11 представляет собой триггер со счетным входом, то он осуществляет пересчет импульсов ПСИ1 и ПСИ2 по модулю два. Выходные сигналы триггеров 10 и 11, используемые для регистра как тактовые серии ТИ1-ТИ4 (фиг. 2, ж, к), обеспечивают сдвиг информации в регистре вправо. При этом длительность TI сигнала «Вправо (фиг. 2, а) определяет количество тактов сдвига, то есть число разрядов, на которое сдвигается информация в регистре вправо.

При подаче сигнала «Влево (фиг. 2, б, интервал TZ) на щину 18 единичный выход

триггера 10 через элемент 15 подключается ко входу R триггера II, нулевой выход триггера 10 через элемент 14 ко входу 5 триггера II, единичный выход триггера 11 через элемент 12 ко входу 5 триггера 10,

а нулевой выход триггера 11 через элемент 13 - ко входу R триггера 10. С помощью сигнала «Влево из серий СИ1 и СИ2 на элементах 12-15 выделяются пакеты импульсов ПСИ1 и ПСИ2, которые в течение

временного интервала Т поступают на входы триггеров 10 и 11. Выходные сигналы триггеров 10 и 11 используются как тактовые серии ТИ4-ТИ1, обеспечивают сдвиг информации в регистре влево. Длительность Т определяет количество тактов сдвига.

Рассмотрим работу регистра при сдвиге информации вправо. Для записи «1 на вход регистра должен

поступить импульс высокого зфовня, опережающий импульс серии ТИ1 на Д такта. При постзплении серии ТИ1 первый триггер первого разряда переключится в единичное состояние. Если же на входе присутствует «О, то первый триггер первого разряда окажется в нулевом состоянии. Соответственно при поступлении импульса ТИ2 второй триггер первого разряда устанавливается в то же состояние, что и первый триггер. По окончании серии ТИ1 первый триггер устанавливается в «О, а второй триггер хранит свое состояние.

Аналогично, при появлении импульса серии ТИЗ информация переписывается со

второго триггера на третий, а при появлеНИИ импульса серии ТИ4 - с третьего на четвертый триггер иервого разряда.

При подаче сигпала сдвига «Влево (фиг. 2, б) процессы записи информации влево протекают подобно предыдущему, по только в обратном направлении, т. е. с выхода - входа 20 информации записывается на четвертый триггер последнего разряда и последовательно сдвигается на третий, второй, первый триггеры последнего разряда, на триггеры предпоследнего разряда и т. д.

Предложенный регистр имеет большое быстоодействие (частота сдвига до 100 МГц), малую потребляемзю мощность (не более 1 -1,5 МВт на разряд) и характеризуется простотой и регулярностью схемы, что позволяет легко реализовать указанный регистр в виде гибридной интегральной схемы. Формирователь реверсивиого регистра достаточно прост в схемном отношении, не содержит нестандартных элементов и для его построения могут быть использованы серийные интегральные схемы ЭСЛ-типа. Один такой формирователь может обеспечить управление 20-30 разпядами регистра, а сам регистр сдвига обеспечивает сдвиг ипформации в требуедюм направлении, а также режим статического хранения записанной информации и может быть использован для построения различных устройств последовательностных машин, сверхоперативных заполшнаюших устройств магазинного и циклического типа, ассоциативных запоминающих устройств и коммутируюших регистровых матриц однородных вычислительных структур.

Формула изобретения

1. Регистр сдвига, содержащий последовательно соединенные триггеры, каждый из

которых выполнен на двух последовательно включенных туннельных диодах, один из которых подключен к щине нулевого потенциала, а другой - к одной из управляющих шин, связанных с соответствующнмп выходами формирователя тактовых ИМПУЛЬСОВ, шины синхроимпульсов и шины сдвига влево и вправо, отлпчающийся тем, что, с целью расширения области применения регистра за счет обеспечения режима двустороннего сдвига и статического хранения, он содержит дополнительный триггер, выполненный на двух последовательно включенных туннельных диодах.

один из которых соединен с шиной нулевого потенциала, а другой - с другой управляющей щиной, а входы формирователя тактовых импульсов соединены соответственно с шинами синхроимиульсов и сдвига влево

и вираво.

2. Регистр по п. 1, о т л п ч а ю HI и и с я тем, что формирователь тактовых ИМПУЛЬСОВ содержит два RS-триггера, входы котопых соединены с выходами элементов И- ИЛИ, иервые и вторые входы которых соединены с соответствующими входами формирователя тактовых импульсов, выходы RS-TpnrrepOB подключены к соответствующим выходам формирователя тактовых ИМПУЛЬСОВ и третьим выходам элемеитов И-ИЛИ.

Источники информации, принятые во внимание нри экспертизе

1.Майоров С. А. и др. Структуры цифровых вычислительных мащин. Л., «Машиностроение, 1970, с. 69.

2.Котт В. М. и др. Туннельные диоды в вычислительной технике, М., «Советское

радио, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| Однотактный регистр сдвига | 1972 |

|

SU447761A1 |

| Буферное запоминающее устройство | 1976 |

|

SU750565A1 |

| Устройство для определения локальных экстремумов | 1983 |

|

SU1164694A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Оптоэлектронный сдвигающий регистр | 1984 |

|

SU1238159A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

72

10

7J

СИ1 fnpaSo Вле8о

IS13

IpUl-J

П

п

15

СИ2

С.; ППППППППППППП ПЛ П ,,, ППППППППППППППППП ,,,, ППППППППП П П П П П

Авторы

Даты

1979-08-30—Публикация

1976-01-04—Подача