блока синхронизации и третьими входами коммутаторов шин профконтроля группы, четвертые входы которых соединены с выходом регистра положительного профконтроля и девятым входом блока синхронизации, десятый вход которого соединен с выходом регистра сдвига, инфор-мационный вход и вход синхронизации которого соединены соответственно с выходами регистра константы и первого элемента И, первый вход которого соединен с выходом элемента И-НЕ и первым входом второго элемента И, выход которого соединен с синхронизирующими входами двоичного счетчика и второго триггера, выход.которого соединен с входами управления режимом регистра сдвига и двоичного счетчика, группа выходов которого соединена с группой входов элемента И-НЕ, второй вход первого элемента И соединен с шиной синхроимпульсов процессора, синхровходом третьего триггера и вторым входом второго элемента И, третьим входом соединенного выходом третьего триггера, вторым входом соединенного с третьим выходом блока сравнения, информационным входом и входом сброса второго триггера и входом сброса двоичного счетчика, информационный вход которого соединен с четвертым выходом блока сравнения.

2. Устройство по п. 1, отличающееся тем, что каждый коммутатор шин профконтроля содержит два транзистора, два делителя напряжения, два элемента И, два ограничительных резистора, два разрядных диода и два электромагнитных реле, контакты которых образуют выход коммутатора, а первые выводы обмоток соединены с шиной нулевого потенциала и анодами разрядных диодов, катоды которых соединены с вторыми выводами обмоток электромагнитных реле и через соответствуюшие ограничительные резисторы подключены соответственно к коллекторам первого и второго транзисторов, базы которых соединены соответственно с выхода.ми первого и второго делителей напряжения, а эмиттеры - с вторым входом коммутатора и первыми входами первого и второго делителей напряжения, вторые входы которых подключены соответственно к выходам первого и второго элементов И, Е;срвые входы которых являются соответственно третьим и четвертым входами коммутатора, а вторые входы соединены с первым входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля электропитания процессора | 1983 |

|

SU1096649A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Аппарат магнитной записи | 1985 |

|

SU1297110A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| Устройство для восстановления процессора после сбоя | 1979 |

|

SU857999A1 |

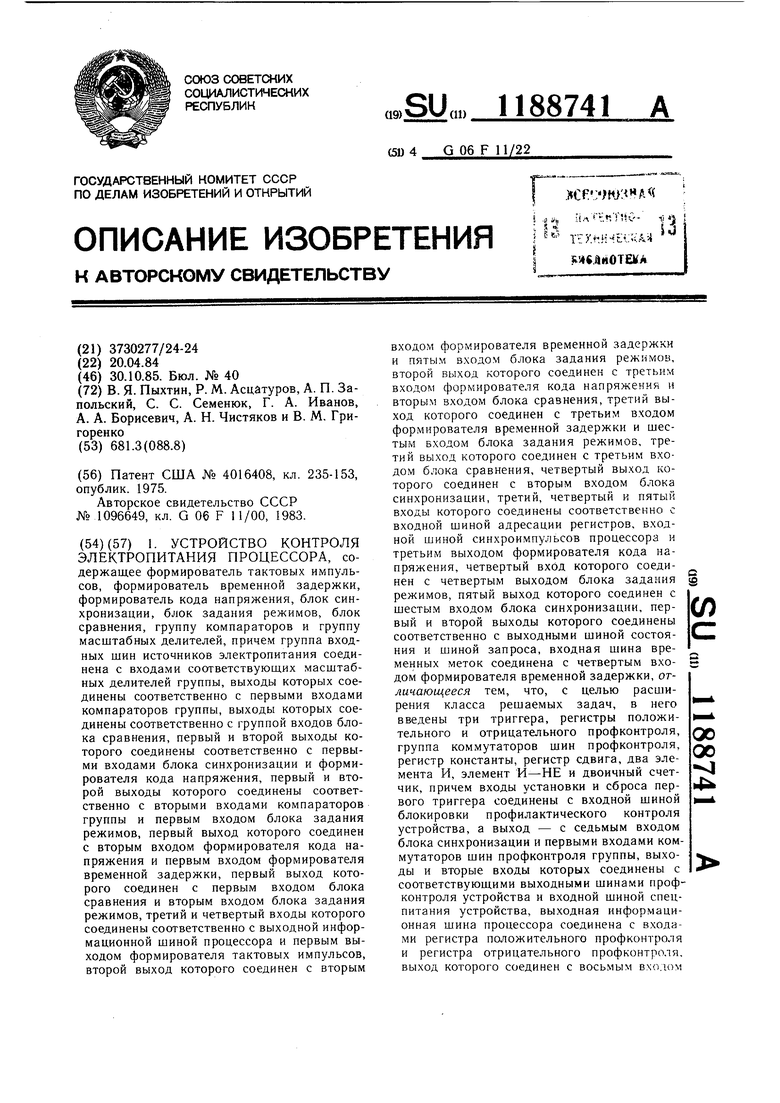

1. УСТРОЙСТВО КОНТРОЛЯ ЭЛЕКТРОПИТАНИЯ ПРОЦЕССОРА, содержащее формирователь тактовых импульсов, формирователь временной задержки, формирователь кода напряжения, блок синхронизации, блок задания режимов, блок сравнения, грунпу компараторов и группу масштабных делителей, причем группа входных шин источников электропитания соединена с входами соответствующих масштабных делителей группы, выходы которых соединены соответственно с первыми входами компараторов группы, выходы которых соединены соответственно с группой входов блока сравнения, первый и второй выходы которого соединены соответственно с первыми входами блока синхронизации и формирователя кода напряжения, первый и второй выходы которого соединены соответственно с вторыми входами компараторов группы и первым входом блока задания режимов, первый выход которого соединен с вторым входом формирователя кода напряжения и первым входом формирователя временной задержки, первый выход которого соединен с первым входом блока сравнения и вторым входом блока задания режимов, третий и четвертый входы которого соединены соответственно с выходной информационной щиной процессора и первым выходом формирователя тактовых импульсов, второй выход которого соединен с вторым входом формирователя временной задержки и пятым входом блока задания режимов, второй выход которого соединен с третьим входом формирователя кода напряжения и вторым входом блока сравнения, третий выход которого соединен с третьим входом формирователя временной задержки и шестым входом блока задания режимов, третий выход которого соединен с третьим входом блока сравнения, четвертый выход которого соединен с вторым входом блока синхронизации, третий, четвертый и пятый входы которого соединены соответственно с входной шиной адресации регистров, входной шиной синхроимпульсов процессора и третьим выходом формирователя кода напряжения, четвертый вхОд которого соединен с четвертым выходом блока задания режимов, пятый выход которого соединен с (Л шестым входом блока синхронизации, первый и второй выходы которого соединены соответственно с выходными шиной состояния и шиной запроса, входная шина временных меток соединена с четвертым входом формирователя временной задержки, огличающееся тем, что, с целью расширения класса решаемых задач, в него введены три триггера, регистры положительного и отрицательного профконтроля, сх группа коммутаторов шин профконтроля, 00 регистр константы, регистр сдвига, два мента И, элемент И-НЕ и двоичный счетчик, причем входы установки и сброса первого триггера соединены с входной шиной блокировки профилактического контроля устройства, а выход - с седьмым входом блока синхронизации и первыми входами коммутаторов шин профконтроля группы, выходы и вторые входы которых соединены с соответствующими выходными шинами профконтроля устройства и входной шиной спецпитания устройства, выходная информационная шина процессора соединена с входами регистра положительного профконтроля и регистра отрицательного профконтроля. выход которого соединен с восьмым входом

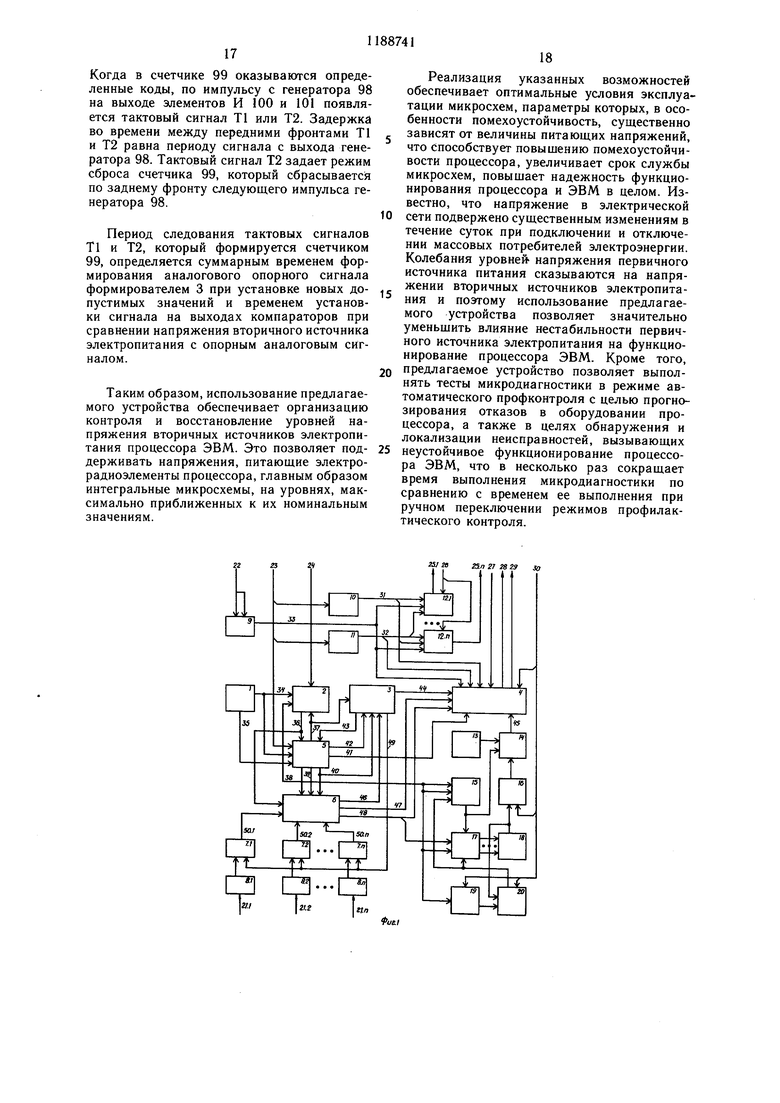

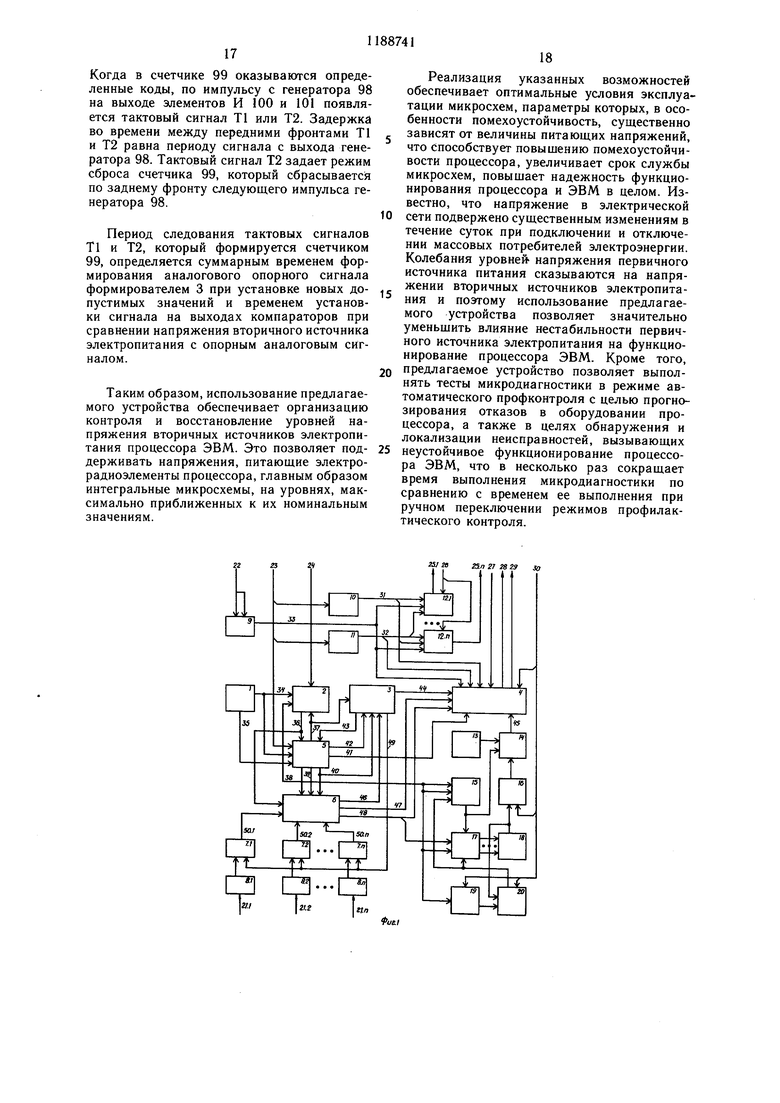

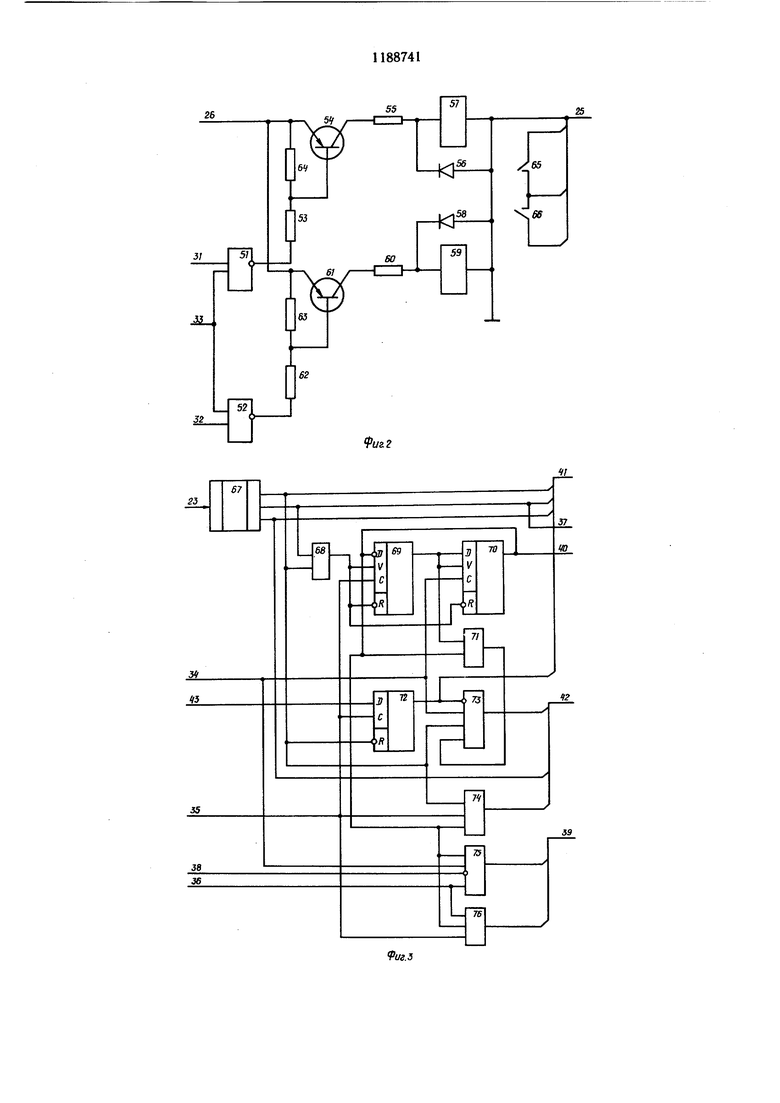

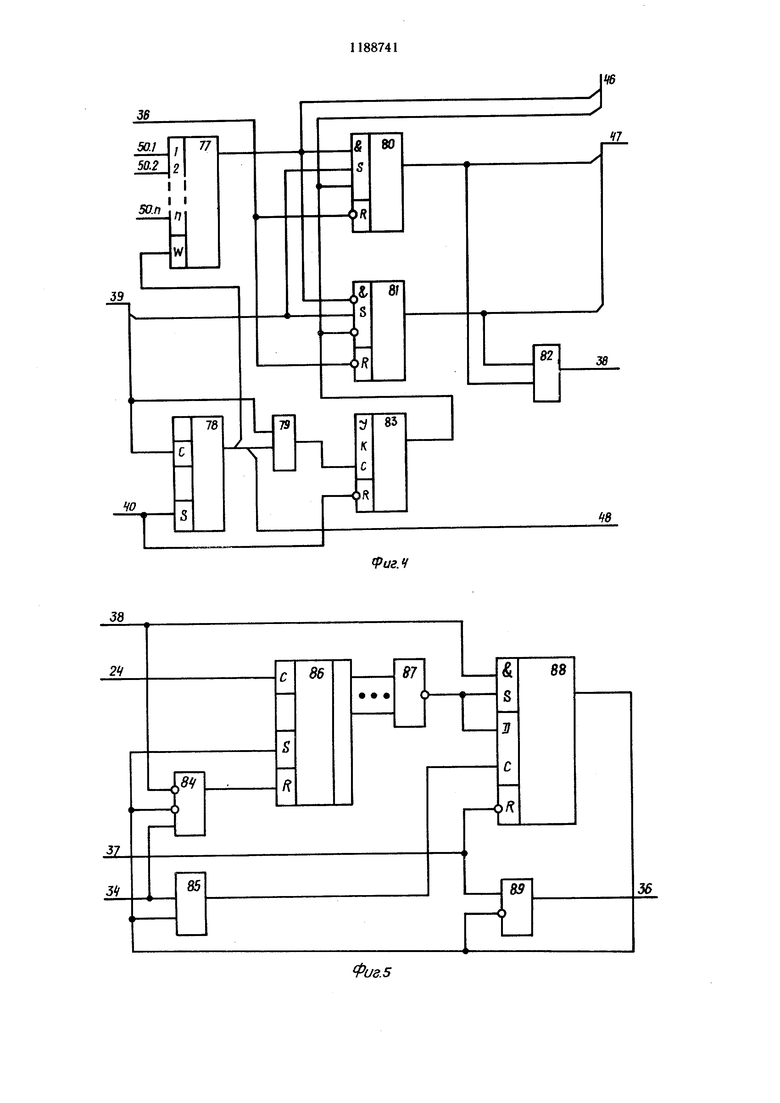

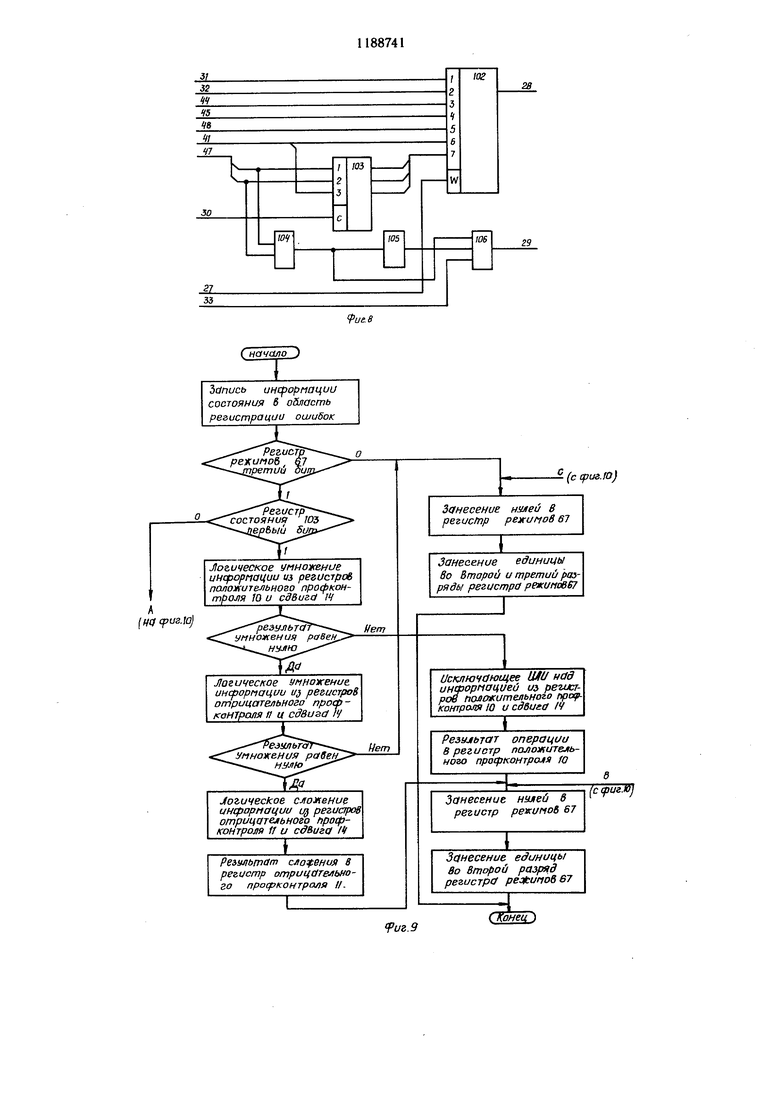

Изобретение относится к вычислительной технике и может быть использовано для контроля, восстановления и измерения напряжения вторичных источников системы электропитания процессора ЭВМ. Цель изобретения - расширение класса решаемых задач путем обеспечения автоматической ступенчатой регулировки уровней напряжения вторичных источников электропитания, вышедших за пределы допустимых граничных значений. На фиг. 1 изображена блок-схема устройства; на фиг. 2 - функциональная схема коммутатора шин профконтроля; на фиг. 3 - функциональная схема блока задания режимов; на фиг. 4 - функциональная схема блока сравнения; на фиг. 5 - функциональная схема формирователя временной задержки; на фиг. 6 - функциональная схема формирователя кода напряжения; на фиг. 7 - функциональная схема формирователя тактовых сигналов; на фиг. 8 - функциональная схема блока синхронизации; на фиг. 9 и 10 - алгоритм обработки запроса на микропрограммное прерывание; на фиг. 11 - алгоритм измерения напряжения вторичных источников электропитания. Устройство контроля и восстановления электропитания процессора (фиг. 1) содержит формирователь 1 тактовых импульсов, формирователь 2 временной задержки, формирователь 3 кода напряжения, блок 4 синхронизации, блок 5 задания режимов, блок 6 сравнения, компараторы 7, масштабные делители 8, первый триггер 9, регистр 10положительного профконтроля, регистр 11отрицательного профконтроля, коммутаторы 12 шин профконтроля, регистр 13 константы, регистр 14 сдвига, второй триггер 15, первый элемент И 16, двоичный счетчик 17, элемент И-НЕ 18, третий триггер 19, второй элемент И 20, шины 21 источников электропитания, шину 22 блокировки профконтроля, выходную информационную шину 23 процессора, шину 24 временных меток, шину 25 профконтроля, шину 26 спецпитания, шину 27 адресации регистров, шину 28 состояния, шину 29 запроса, шину 30 синхроимпульсов процессора, линии 31-50, связывающие блоки и узлы устройства. Коммутатор 12 шин профконтроля (фиг. 2) имеет элементы И 51 и 52, резисторы 53, первые транзистор 54, ограничительный резистор 55, разрядный диод 56 и электромагнитное реле 57, вторые разрядный диод

58, электромагнитное реле 59, ограничительный резистор 60 и транзистор 61, резисторы 62 и 63 второго делителя напряжения, резисторы 64 и 53 образуют первый делитель напряжения. Контакты 65 и 66 электромагнитных реле 57 и 59 образуют выход коммутатора 12.

Блок 5 задания режимов (фиг. 3) состоит из регистра 47 режимов 7, элемента ИЛИ 68, триггеров 69 и 70, элемента ИЛИ 71, триггера 72 и элементов И 73-76.

Блок 6 сравнения (фиг. 4) содержит мультиплексор 77, двоичный счетчик 78, элемент И 79, триггеры 80 и 81, элемент ИЛИ 82 и триггер 83.

Формирователь 2 временной задержки (фиг. 5) состоит из элементов И 84 и 85, счетчика 86, элемента И 87, триггера 88 и элемента И 89.

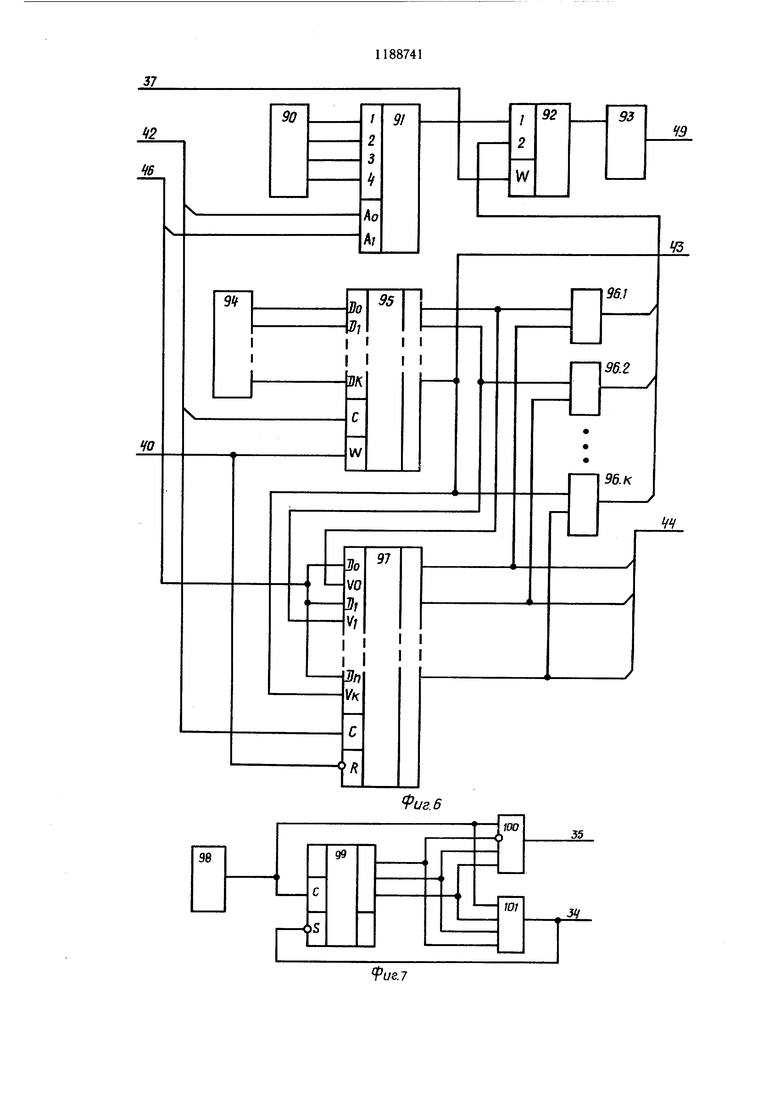

Формирователь 3 кода напряжения (фиг. 6) содержит регистр 90, мультиплексоры 91 и 92, цифроаналоговый преобразователь 93, регистр 94 константы, регистр 95 сдвига, элементы ИЛИ 96 и регистр 97 результата.

Формирователь 1 тактовых сигналов (фиг. 7) состоит из генератора 98 импульсов, счетчика 99 и элементов И 100 и 101.

Блок 4 синхронизации (фиг. 8) содержит мультиплексор 102, регистр 103 состояния, элемент ИЛИ 104, элемент (линию) 105 задержки и элемент И 106.

Формирователь 1 тактовых сигналов предназначен для формирования двух тактовых сигналов, синхронизирующих работу устройства.

Формирователь 2 временной задержки служит для приостановки контроля напряжений вторичных источников электропитания в течение заданного интервала времени.

Формирователь 3 кода напряжения формирует цифровой код измеряемого напряжения вторичного источника электропитания и аналоговый опорный сигнал в соответствии с цифровыми кодами значений допустимых напряжений, а также в соответствии с кодами, формируемыми в режиме измерения.

Блок 4 предназначен для синхронизации процесса передачи информации состояния, формируемой предлагаемым устройством, с работой процессора.

Блок 5 служит для задания режимов функционирования и управления работой устройства.

Блок 6 используется для обработки результатов сравнения напряжения вторичных источников электропитания с опорным напряжением и для модификации адресов контролируемых вторичных источников электропитания.

Компараторы 7 предназначены для сравнения напряжения вторичных источников электропитания с напряжением опорного аналогового сигнала. Компараторы вырабатывают сигнал единичного уровня при превышении напряжения контролируемого источника напряжения опорного аналогового сигнала.

Масштабные делители 8 используются для приведения напряжений вторичных источников электропитания, имеющих различные номинальные значения, к единому нормированному значению напряжения.

Первый триггер 9 блокирует условия проф0 контроля и запроса на микропрограммное прерывание при отключении режима автоматического профконтроля с пульта инженера ЭВМ.

Регистр 10 положительного профконтроля задает условия, например, пятипроцентного увеличения напряжения вторичных источников электропитания, регистр 11 отрицательного профконтроля - условия, например, пятипроцентного уменьшения, напряжения вторичных источников электропитания. 0 Коммутаторы 12 щин профконтроля предназначены для установки вторичных источников электропитания в определенный режим профконтроля посредством управления шинами 25.

5 Регистр 13 константы служит для хранения двоичного кода, заносимого в регистр 14. В качестве регистра 13 могут быть использованы логические уровни нуля и единицы.

Регистр 14 сдвига формирует двоичный позиционный код, в котором в единичное состояние установлен только один разряд, соответствующий адресу вторичного источника электропитания. Цифровой код используется для анализа и установки в режим профконтроля определенного вторичного источника электропитания.

Второй триггер 15 предназначен для управления режимами работы регистра 14 и двоичного счетчика 17. В качестве второго триггера используют двухтактный триггер.

Первый элемент И 16 формирует синхросигналы, поступающие на вход синхронизации регистра 14.

Двоичный счетчик 17 служит для определения числа сдвигов в регистре 14.

Элемент И-НЕ 18 предназначен для формирования сигнала блокировки синхроимпульсов регистра 14 и двоичного счетчика 17. Сигнал формируется при достижении счетчиком 17 двоичного кода, равного адресу последнего контролируемого вторичного источника электропитания.

Третий триггер 19 используется для устранения влияния асинхронной установки сигнала на линии 38 по отношению к сигналам на шине 30 синхроимпульсов процессора на начальную установку второго триггера 5 15, регистра 14 сдвига и двоичного счетчика 17.

Второй элемент И 20 формирует синхросигналы, поступающие на входь синхронизации второго триггера и двоичного счетчика. Шины 21 источников электропитания предназначены для подключения выходов источников электропитания к масштабным делителям 8. Шина 22 блокировки профконтроля служит для управления состоянием первого триггера 9 при включении и отключении режима профконтроля. Выходная информационная шина 23 процессора- предназначена для передачи управляющей информации в блок 5 задания режимов и для занесения информации в регистры 10 и 11. Занесение информации с выходной информационной шины 23 производится микропрограммно. По шине 24 временных меток осуществляется передача в формирователь 2 временной задержки времязадающих импульсов. В качестве источника воеменных меток может быть использован разряд часов суточного времени процессора. Шины 25 профконтроля предназначены для связи вторичных источников электропитания с коммутаторами 12 щин профконтроля. Через шину 26 спецпитания питающее напряжение подводится на эмиттеры транзисторов в коммутаторах 12 шин профконтроля. Шина 27 адресации регистров предназначена для управления процессом выдачи информации состояния на шину 28 состояния. По шине 28 состояния осуществляется передача в процессор информации о состоянии системы электропитания процессора. Выдача в процессор запроса на микропрограммное прерывание производитс.я по щине 29. Шина 30 синхроимпульсов процессора предназначена для синхронизированной установки информации в регистре 103 состояния блока 4 синхронизации для избежания изменений информации на шине 28 во время опроса ее процессором, а также для синхронизации ускоренного формирования константы в регистре 14. Устройство работает в режимах оперативного контроля и измерения. В режиме оперативного контроля устройство обеспечивает контроль уровней напряжения источников электропитания. При превышении контролируемым напряжением верхней границы или если это напряжение оказывается ниже нижней границы, устройство контроля включает формирователь 2, который приостанавливает работу устройства контроля в течение заданного интервала времени. При этом сохраняется адрес контролируемого вторичного источника электропитания. По истечении заданного интервала времени устройство повторяет цикл сравнения, в процессе которого было обнаружено нарушение заданных границ. Если при этом повторно обнаруживается нарушение границ, устройство вырабатывает сигнал прерывания. Микропрограмма обработки прерывания определяет, при каких допустимых значениях напряжения произошло нарущение. Если нарущение произошло при сравнении со средним уровнем допустимых значений, то в регистре 67 блока 5 устанавливается бит, задающий режим контроля на соответствие предельным допустимым значениям, а на системный пульт процессора выдается сообщение о прерывании от схем контроля. При превышении верхнего или нижнего граничных значений напряжения микропрограммно устанавливается соответствующий бит в регистрах 10 и 11, приближая напряжение вторичного источника электропитания к номинальному значению. Предлагаемое устройство в режиме оперативного контроля работает следующим образом. При отсутствии признаков режима оперативного контроля и измерения в регистре 67 (фиг. 3) потенциалы нулевого уровня с выходов регистра режимов через элемент ИЛИ 68 поступают на сбросовые входы триггеров 69 и 70, устанавливая их в нулевое состояние. Сигналы нулевого уровня с выходов триггера 70 и элемента ИЛИ 71 блокируют формирование синхросигналов элементами И 73-76. Нулевой уровень сигнала с выхода регистра 67 сбрасывает триггер 72. Сигнал нулевого уровня с выхода регистра 67 по линии 37 поступает в формирователь 2 (фиг. 5) сбрасывая триггер 88, и через элемент И 89 поступает на сбросовые входы триггеров 80 и 81 (фиг. 4), устанавливая их в нулевое состояние. Двоичный счетчик 78 находится в режиме хранения, а триггер 83 сброшен по нулевому уровню сигнала, поступающему по линии 40 с второго выхода блока 5. Нулевой уровень сигнала с выходов триггеров 80 и 81 через элемент ИЛИ 82 по линии 38 поступает на информационный и сбросовые входы триггера 15 (фиг. 1) и двоичного счетчика 17, устанавливая их в нулевое состояние, и на информационный вход третьего триггера 19, который по первому синхросигналу с щины 30 установится в нулевое состояние. При сброшенном триггере 15 в двоичном счетчике 17 и в регистре 14 установлен режим занесения и константа из регистра 13 непрерывно заносится в регистр 14, пока не будет заблокирован синхросигнал с выхода элемента И 16 или не установится триггер 15, по единичному состоянию которого в регистре 14 устанавливается режим сдвига. Нулевой уровень сигнала с выхода триггера 88 (фиг. 5) запрещает прохождение синхросигнала через элемент И 85 на вход синхронизации триггера 88, устанавливает режим хранения счетчика 86 и разрешает сброс счетчика по тактовому сигналу, поступающему на вход элемента И 84 по линии 34 с второго выхода формирователя 1 тактовых сигналов (фиг. 7). По нулевому уровню сигнала с выхода триггера 70 сбрасывается регистр 97 результата (фиг. 6). Таким образом, устройство переходит в исходное состояние при снятии режимов функционирования с сохранением адреса вторичного источника в двоичном счетчике 78 блока 6 сравнения (фиг. 4). Для установки режима оперативного контроля в регистр 67 (фиг. 3) с выходной информационной шины 23 микропрограммно заносится признак режима оперативного контроля. При этом на выходе регистра режимов 67 появляется сигнал единичного уровня, который через элемент ИЛИ 68 поступает на первый синхровход триггера 69, разрешая его установку в единичное состояние. Так как в это время триггер 70 сброшен, по первому тактовому сигналу Т1, поступающему с первого выхода формирователя 1 по линии 35, устанавливается триггер 69, единичный уровень сигнала на выходе которого разрешает установку триггера 70 по заднему фронту второго тактового сигнала Т2, поступаюш,его по линии 34 от формирователя 1 (фиг. 7). По следуюш,ему тактовому сигналу Т1 триггер 69 (фиг. 3) сбрасывается и нулевой уровень сигнала, поступаюш,ий с его выхода на первый синхровход триггера 70, запрещает изменение его в состояния по следующим тактовым сигналам Т2. Сигнал единичного уровня с выхода триггера 70 по линии 40 поступает в блок 6 (фиг. 4) на вход управления режимами двоичного счетчика 78, устанавливая режим счета. Контроль напряжений вторичных источников электропитаиия начинается с адреса, который сохраняется в двоичном счетчике 78. Сигнал нулевого уровня с выхода триггера 83 (это соответствует контролю на соответствие нижним допустимым значениям напряжения) поступает по линии 46 на первый вход управления мультиплексора 91 (фиг. 6). На выход мультиплексора 91 из поля регистра 90 передается двоичный код, соответствующий среднему или граничному нижним значениям напряжения в зависимости от сигнала на втором входе управления мультиплексора 91, поступающего по линии 42 с третьего выхода регистра 67 (фиг. 3). Сигнал единичного уровня с выхода регистра 67, соответствующий режиму оперативного контроля, по линии 37 поступает на вход управления мультиплексора 92 (фиг. 6), разрешая прохождение двоичного кода с выхода мультиплексора 91 на вход цифроаналогового преобразователя 93, который формирует в соответствии с двоичным кодом опорное напряжение, поступающее на вторые входы компараторов 7. Навыходах компараторов 7 устанавливаются сигналы единичного уровня при превышении контролируемым напряжением опорного напряжения и сигналы нулевого уровня, если контролируемое напряжение меньше опорного. Сигналы с выходов компараторов 7 поступают на информационные входы мультиплексора 77 (фиг. 4). На выход мультиплексора 77 передается результат хравнения с информационного входа, определяемого адресом втхэричного источника электропитания в двоичном счетчике 78. При установленном триггере 70 (фиг. 3) первый тактовый сигнал Т1 с линии 35 проходит на выход элемента И 76 и поступает в блок 6 (фиг. 4), стробируя установку триггеров 80 и 81. Если на выходе мультиплексора 77 присутствует сигнал единичного уровня и триггер 83 сброщен, то триггеры 80 и 81 не устанавливаются в единичное состояние, что свидетельствует о соответствии напряжения вторичного источника электропитания нижним допустимым значениям напряжения. На выходах триггеров 80 и 81 и на выходе элемента ИЛИ 82 сохраняется сигнал нулевого уровня, который по линии 38 поступает в блок 5 (фиг. 3) на вход элемента И 75 и разрешает прохождение второго тактового сигнала Т2 через элемент И 75 на вход синхронизации двоичного счетчика 78 (фиг. 4), увеличивая состояние двоичного счетчика 78 на единицу. При этом мультиплексор 77 передает на выход сигнал со следующего информационного входа и циклы контроля повторяются до тех пор, пока не зафиксируется нарушение допустимых значений напряжения. Когда в двоичном счетчике 78 зафиксируется адрес последнего контролируемого вторичного источника, очередной синхросигнал двоичного счетчика 78 проходит через элемент И 79 на синхровход триггера 83 и переводит его из нулевого состояния в единичное, что соответствует контролю на соответствие верхним допустимым значениям. В качестве триггера 83 используется триггер со счетным входом. По очередному синхросигналу он меняет свое состояние на противоположное. Контроль начинается с проверки соответствия напряжения всех вторичных источников электропитания нижним допустимым значениям, после чего триггер 83 переключается в единичное состояние и выполняется контроль напряжения всех вторичных источников на соответствие верхним допустимым значениям. При этом единичный уровень сигнала с выхода триггера 83 поступает на первый вход управления мультиплексора 92 (фиг. 6) и на выход мультиплексора 91 из поля регистра 90 передаются коды, соответствующие верхним допустимым значениям. Вместо регистра 90 могут быть использованы потенциалы нуля и единицы, заве9денные в определенных сочетаниях на входы мультиплексора 91, с шин логического нуля и единицы. При условии нарушения верхних допустимых значений напряжения, т. е. при единичном уровне сигнала на выходе мультиплексора 77 (фиг. 4) и при единичном состоянии триггера 83, по синхросигналу устанавливается триггер 80, единичный уровень сигнала с выхода которого через элемент ИЛИ 82 по линии 38 поступает в формирователь 2 (фиг. 5), устанавливая триггер 88 в единичное состояние, так как счетчик 86 сброшен и на выходе элемента И 87 имеется единичный уровень сигнала. Единичный уровень сигнала с выхода триггера 88 поступает на вход управления счетчика 8Ь, устанавливая режим счета, и на второй вход элемента И 89, блокируя прохождение сигнала с первого выхода блока 5 по линии 37 на выход элемента И 89, нулевой уровень сигнала с выхода которого по линии 36 поступает в блок б сравнения (фиг. 4), сбрасывая триггеры 80 и 81, и в блок 5 (фиг. 3), блокируя синхросигналы, формируемые элементами И 75 и 76. Таким образом, на определенное время блокируются синхросигналы установки триггеров 80 и 81 (фиг. 4) и двоичного счетчика 78, в котором сохраняется адрес вторичного источника, превысившего допустимые значения изменения напряжения. По синхросигналам с шины 24 счетчик 86 (фиг. 5) отсчитывает временной интервал, определяемый кодом, согласно которому выходы счетчика 86 соединены с входами элемента И 87, на выходе которого присутствует единичный уровень сигнала до истечения временного интервала. Элемент И 85 разрешает прохождение тактового сигнала Т2 с линии 34 на вход синхронизации I триггера 88, подтверждая его единичное состояние до истечения временного интервала и устанавливая его в нулевое состояние по заднему фронту синхросигнала, поступаюшего по истечении временного интервала. Нулевой уровень сигнала с выхода триггера 88 устанавливает режим хранения счетчика 86, запрещает синхросигналы с выхода элемента И 85 и разрешает прохождение сигнала с линии 37 на выход элемента И 89. Единичный уровень сигнала с выхода элемента И 89 по линии 36 поступает в блок 5 (фиг. 3) и разрешает прохождение тактового сигнала Т1 через элемент И 76 в блок 6 (фиг. 4). Если по истечении заданного временного интервала условия нарушения допус тимых значений исчезли, что свидетельствует о кратковременном отклонении напряжения вторичного источника от номинала, то триггеры 80 и 81 не устанавливаются, а по синхросигналу состояние двоичного счетчика 78 увеличивается на единицу и устройство контролирует очередной вторичный источник элек тропитания.

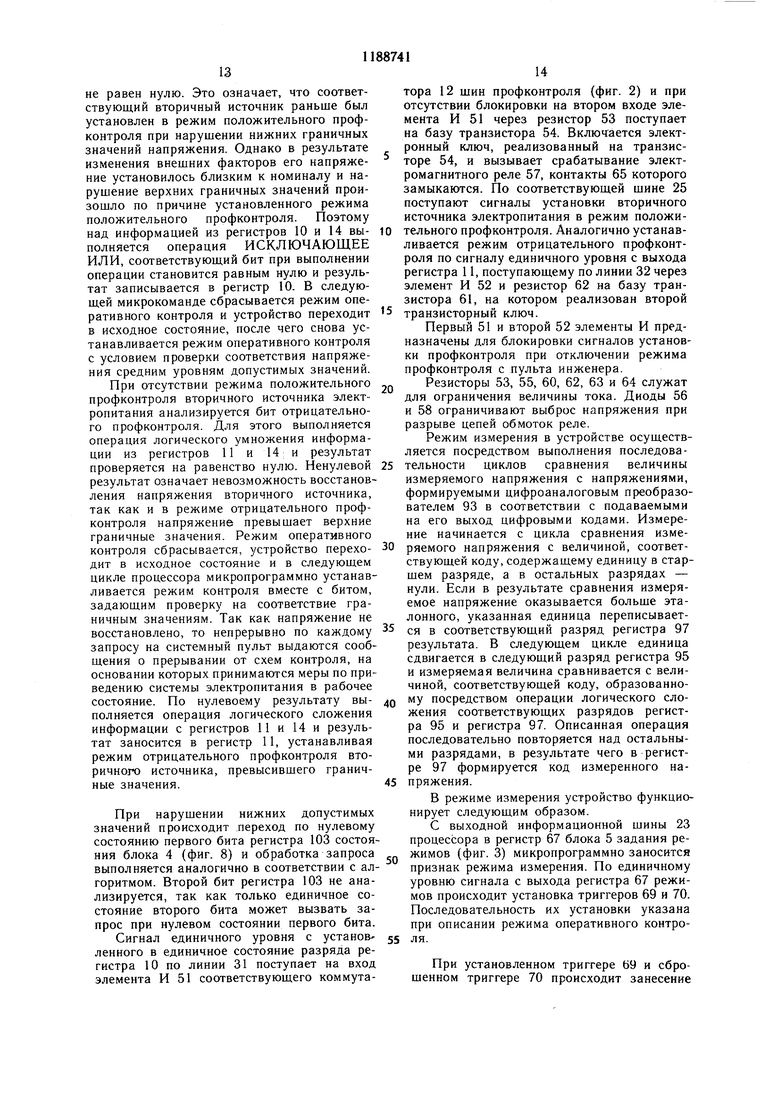

10 При этом сигнал нулевого уровня с выхода элемента ИЛИ 82 по линии 38 поступает в формирователь 2 (фиг. 5) и разрешает прохождение тактовых сигналов Т2 с линии 34 через элемент И 84 на сбросовый вход счетчика 86. По первому сигналу счетчик 86 сбрасывается и нулевые уровни сигналов с его выходов устанавливают сигнал единичного уровня на выходе элемента И 87, разрешая установку триггера 88 при контроле напряжения очередного вторичного источника. Если по истечении заданного интервала времени условия нарушения верхних допустимых значений сохранились, то устанавливается триггер 80 (фиг. 4) и единичный уровень сигнала с его выхода через элемент ИЛИ 82 по линии 38 поступает в блок 5 (фиг. -3), запрешая синхросигнал с выхода элемента И 75, по которому модифицируется адрес вторичного источника, и в формирователь 2 (фиг. 5) на входы триггера 88 и элемента И 84. Триггер 88 в этом случае не устанавливается, так как счетчик 86 сбрасывается по тактовому сигналу Т2, но не может быть сброшен из-за блокировки элемента И 84 единичным уровнем сигнала на линии 38. Нулевой уровень сигнала с выхода элемента И 87 запрещает повторную установку триггера 88. В качестве шины 24 временных меток может быть использован выход определенного разряда часов суточного времени процессора с целью получения необходимой временной задержки при малой разрядности счетчика 86. Минимальный период следования сигналов на шине 24 должен быть не менее двух периодов следования тактовых сигналов Т1 и Т2 для гарантированного сброса триггера 88 по истечении заданного временного интервала. Сигнал единичного уровня с выхода триггера 80 блока 6 (фиг. 4) поступает в блок 4 на входы регистра 103 и элемента ИЛИ 104. По синхросигналу с шины 30 устанавливается в единичное состояние первый разряд регистра 103, означающий нарушение верхних допустимых значений напряжения. Второй разряд регистра 103 устанавливается при нарушении нижних допустимых значений напряжения. Сигнал единичного уровня с выхода элемента ИЛИ 104 поступает на вход элемента И 106 и через линию 105 задержки на другой вход элемента И 106, вызывая запрос на микропрограммное прерывание единичным уровнем сигнала на шине 29. Блокировка запроса на микропрограммное прерывание осуществляется посредством сброса триггера 9 (фиг. 1) парафазным сигналом, поступающим по шине 22 блокировки профконтроля с пульта инженера при отключении режима профконтроля. Линия 105 задержки в блок 4 (фиг. 8) предназначена для устранения помехи на шине 29 запроса при включении формирователя 2 временной задержки при первом нарушении допустимых значений напряжения конкретным вторичным источником электропитания и должна перекрывать время от установки триггеров 80 и 81 (фиг. 4) до их сброса при установке триггера 88 формирователя 2 временной задержки (фиг. 5). При фиксировании нарушения допустимых значений напряжения по истечении временного интервала сигнал единичного уровня по линии 38 из блока 6 (фиг. 1) поступает на информационный вход триггера 19, который по первому синхросигналу с шины 30 устанавливается в единичное состояние. Так как двоичный счетчик 17 сброшен, то на первые входы первого 16 и второго 20 элементов И с выхода элемента И-НЕ 18 поступает сигнал единичного уровня. По третьему синхросигналу с шины 30 на выход первого элемента И 16 проходят синхросигналы, по которым в регистр 14 заносится константа или выполняется сдвиг влево в зависимости от состояния триггера 15. В качестве регистра 13 могут быть использованы потенциалы нуля и единицы. Потенциал единицы заводится на самый младший информационный вход регистра 14, а потенциал нуля - на остальные информационные входы. Разрядность регистра 14 равна числу контролируемых источников электропитания. Второй синхросигнал с шины 30 через элемент И 20 поступает на синхровходы двоичного счетчика 17 и триггера 15. В качестве триггера 15 используется двухтактный триггер, который устанавливается по заднему фронту синхросигнала. Поэтому по первому синхросигналу в счетчик 17 по линии 48 заносится адрес вторичного источника электропитания с выхода блока 6. Установленный в единичное состояние триггер 15, так как на его информационный вход поступил по линии 38 сигнал единичного уровня с выхода блока 6, задает режим сдвига влево регистра 14 и режим счета двоичного счетчика 17, которые выполняют функции по синхросигналам, поступаюшим соответственно с выходов первого 16 и второго 20 элементов И. При фиксировании в двоичном счетчике 17адреса последнего вторичного источника электропитания, на выходе элемента И-НЕ 18появляется нулевой уровень сигнала, который запрещает синхросигналы с выходов первого 16 и второго 20 элементов И. В регистре 14 сдвига хранится сформированная константа.: Первый, второй и третий синхросигналы с шины 30 должны иметь между собой задержку во времени, обусловленную задержками элементов. Между вторым и третьим синхросигналом должна быть пауза, которая перекрывала бы время установки нулевого уровня сигнала на выходе элемента И-НЕ 18, когда в двоичном счетчике 17 зафиксируется адрес последнего вторичного источника электропитания. В противном случае может произойти лишний сдвиг в регистре 14. При нарушении нижних допустимых у значений устройство выполняет действия, аналогичные описанным выше при нарушении верхних допустимых значений. Запрос на микропрограммное прерывные обрабатывается процессором в соответствии с алгоритмом, приведенным на фиг. 9 и 10. Микропрограмма обработки прерывания осуществляет чтение информации о состоянии системы электропитания процессора. Через мультиплексор 102 блока 4 (фиг. 8) и шину 28 состояния в процессор передается состояние регистров 10, И, 67 и 103, а также адрес вторичного источника электропитания из двоичного счетчика 78 блока 6 (фиг. 4). Эта информация записывается в область регистрации ошибок процессора, откуда операционная система переписывает ее в файл регистрации ошибок при обработке прерывания от схем контроля. Выдача информации на шину 28 состояния происходит под управлением сигналов с шины 27 адресации регистров, которая соединена с управляющими входами мультиплексора 102 блока 4 (фиг. 8) и разрешает прохождение на шину 28 двоичного кода с адресуемого регистра. Микропрограмма анализирует состояние третьего бита регистра 67 блока 5 (фиг. 3). Нулевое состояние этого бита означает, что выполняется контроль на соответствие напряжения средним уровням допускаемых значений. При этом микропрограммно сбрасывается регистр 67 устройство переходит в исходное состояние в описанной выше последовательности. В следующей микрокоманде в регистре 67 устанавливается второй бит, задаюший режим оперативного контроля, и третий бит, устанавливающий признак контроля на соответствие граничным значениям и на этом обработка запроса завершается. При единичном состоянии третьего бита регистра 67 анализируется первый бит регистра 103. Нулевое его состояние означает, что произошло нарушение нижних граничных значений напряжения, а единичное состояние - нарушение верхних граничных значений. Во втором случае считывается информация из регистров 10 и 14, выполняется операция логического умножения над считанными операндами и результат анализируется на нулевое состояние. Если в регистре 10 был установлен бит, соответствующий установленному в единичное состояние биту в регистре 14, то результат

13

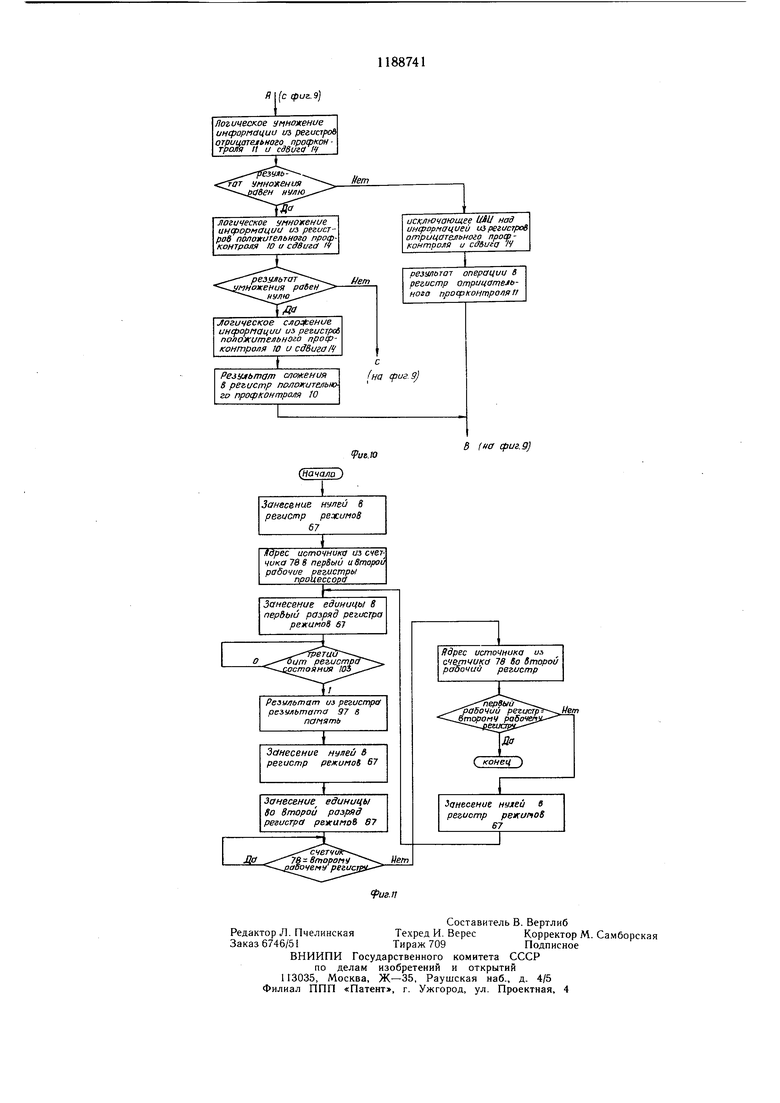

не равен нулю. Это означает, что соответствующий вторичный источник раньше был установлен в режим положительного профконтроля при нарушении нижних граничных значений напряжения. Однако в результате изменения внешних факторов его напряжение установилось близким к номиналу и нарушение верхних граничных значений произошло по причине установленного режима положительного профконтроля. Поэтому над информацией из регистров 10 и 14 выполняется операция ИСКЛЮЧАЮЩЕЕ ИЛИ, соответствующий бит при выполнении операции становится равным нулю и результат записывается в регистр 10. В следующей микрокоманде сбрасывается режим оперативного контроля и устройство переходит в исходное состояние, после чего снова устанавливается режим оперативного контроля с условием проверки соответствия напряжения средним уровням допустимых значений. При отсутствии режима положительного профконтроля вторичного источника электропитания анализируется бит отрицательного профконтроля. Для этого выполняется операция логического умножения информации из регистров 11 и 14; и результат проверяется на равенство нулю. Ненулевой результат означает невозможность восстановления напряжения вторичного источника, так как и в режиме отрицательного профконтроля напряжение превышает верхние граничные значения. Режим оперативного контроля сбрасывается, устройство переходит в исходное состояние и в следуюшем цикле процессора микропрограммно устанавливается режим контроля вместе с битом, задающим проверку на соответствие граничным значениям. Так как напряжение не восстановлено, то непрерывно по каждому запросу на системный пульт выдаются сообщения о прерывании от схем контроля, на основании которых принимаются меры по приведению системы электропитания в рабочее состояние. По нулевоему результату выполняется операция логического сложения информации с регистров 11 и 14 и результат заносится в регистр 11, устанавливая режим отрицательного профконтроля вторичного источника, превысившего граничные значения.

При нарушении нижних допустимых значений происходит переход по нулевому состоянию первого бита регистра 103 состояния блока 4 (фиг. 8) и обработка запроса выполняется аналогично в соответствии с алгоритмом. Второй бит регистра 103 не анализируется, так как только единичное состояние второго бита может вызвать запрос при нулевом состоянии первого бита.

Сигнал единичного уровня с установленного в единичное состояние разряда регистра 10 по линии 31 поступает на вход элемента И 51 соответствующего коммута14

тора 12 щин профконтроля {фиг. 2) и при отсутствии блокировки на втором входе элемента И 51 через резистор 53 поступает на базу транзистора 54. Включается электронный ключ, реализованный на транзисторе 54, и вызывает срабатывание электромагнитного реле 57, контакты 65 которого замыкаются. По соответствующей шине 25 поступают сигналы установки вторичного источника электропитания в режим положительного профконтроля. Аналогично устанавливается режим отрицательного профконтроля по сигналу единичного уровня с выхода регистра 11, поступающему по линии 32 через элемент И 52 и резистор 62 на базу транзистора 61, на котором реализован второй

5 транзисторный ключ.

Первый 51 и второй 52 элементы И предназначены для блокировки сигналов установки профконтроля при отключении режима профконтроля с пульта инженера.

Резисторы 53, 55, 60, 62, 63 и 64 служат для ограничения величины тока. Диоды 56 и 58 ограничивают выброс напряжения при разрыве цепей обмоток реле.

Режим измерения в устройстве осуществляется посредством выполнения последовательности циклов сравнения величины измеряемого напряжения с напряжениями, формируемыми цифроаналоговым преобразователем 93 в соответствии с подаваемыми на его выход цифровыми кодами. Измерение начинается с цикла сравнения измеряемого напряжения с величиной, соответствующей коду, содержащему единицу в старшем разряде, а в остальных разрядах - нули. Если в результате сравнения измеряемое напряжение оказывается больше эталонного, указанная единица переписывается в соответствующий разряд регистра 97 результата. В следующем цикле единица сдвигается в следующий разряд регистра 95 и измеряемая величина сравнивается с величиной, соответствующей коду, образованнод му посредством операции логического сложения соответствующих разрядов регистра 95 и регистра 97. Описанная операция последовательно повторяется над остальными разрядами, в результате чего в регистре 97 формируется код измеренного на5 пряжения.

В режиме измерения устройство функционирует следующим образом.

С выходной информационной шины 23 процессора в регистр 67 блока 5 задания режимов (фиг. 3) микропрограммно заносится признак режима измерения. По единичному уровню сигнала с выхода регистра 67 режимов происходит установка триггеров 69 и 70. Последовательность их установки указана при описании режима оперативного контро5 ля.

При установленном триггере Ь9 и сброшенном триггере 70 происходит занесение

15 константы из регистра 94 формирователя 3 (фиг. 6) в регистр 95 сдвига, так как в регистре 95 установлен режим занесения высоким уровнем сигнала, поступающим по линии 40 с выхода триггера 70 (фиг. 3). Единичный уровень сигнала с выхода триггера 69 через элемент ИЛИ 71 поступает на элемент И 73, разрешая прохождение на его выход тактового сигнала Т2, поступающего на синхровход регистра 95 (фиг. 6), по которому происходит занесение константы. Двоичный код с выхода регистра 95 поступает на первые входы соответствующих элементов ИЛИ 96, на вторые входы которых поступает информация из регистра 97 результата и с выходов элементов ИЛИ 96 и на второй вход мультиплексора 92. Мультиплексор 92 передает на цифроаналоговый преобразователь 93 информацию с второго входа, так как на управляющий его вход в режиме изменения поступает потенциал нулевого уровня с второго выхода регистра 67 режимов блока 5 задания режимов. Установленный по заднему фронту тактового сигнала Т2 триггер 70 разрешает прохождение с линии 35 через элемент И 74 тактового сигнала Т1, который поступает в формирователь 3 (фиг. 6) на общий синхровход регистра 97 результата, на информационные входы которого заводится сигнал результата сравнения опорного аналогового сигнала с напряжением вторичного источника электропитания с выхода мультиплексора 77 (фиг. 4). Запись информации в регистр 97 по каждому общему синхросигналу разрешается только в один к-й разряд единичным уровнем сигнала с к-го выхода регистра 95 сдвига. По следующему синхросигналу, поступающему на синхровход регистра 95, происходит сдвиг единицы на один разряд вправо и повторяется цикл сравнения опорного сигнала с измеряемым напряжением. Единица, записанная в к-й разряд регистра 97 свидетельствует о том, что с учетом к-го разряда регистра 95 и разрядов с первого по (к-1)-й регистр 97 аналоговый опорный сигнал меньше измеряемого напряжения. Разрядность регистра 97, как и регистра 95, определяется точностью, которую могут обеспечить цифроаналоговый преобразователь 93 и комрараторы 7. В последнем цикле измерения единица сдвинута в младший разряд регистра 95 и сигнал единичного уровня по линии 43 поступает в блок 5 (фиг. 3) на информационный вход триггера 72, который по тактовому сигналу Т1 устанавливается в единичное состояние и блокирует синхросигналы сдвига на выходе элемента И 73т а также по линии 41 поступает в блок 4 (фиг. 8) на вход регистра 103 состояния.

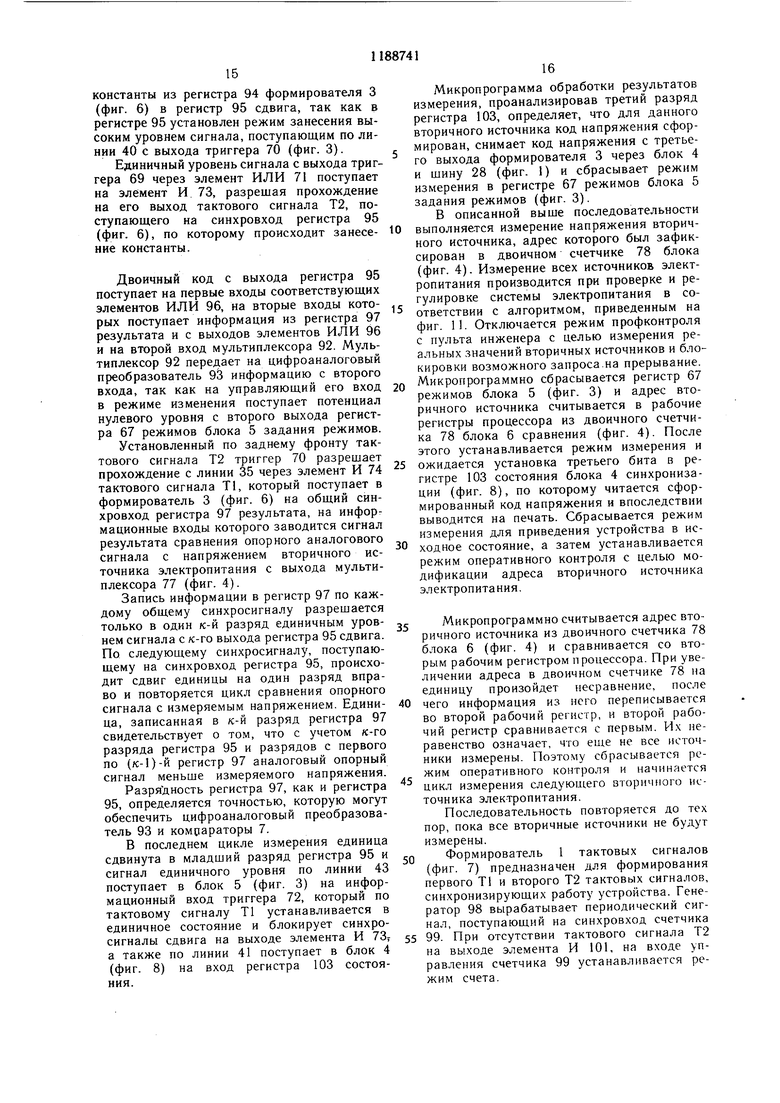

16 Микропрограмма обработки результатов измерения, проанализировав третий разряд регистра 103, определяет, что для данного вторичного источника код напряжения сформирован, снимает код напряжения с третьего выхода формирователя 3 через блок 4 и шину 28 (фиг. 1) и сбрасывает режим измерения в регистре 67 режимов блока 5 задания режимов (фиг. 3). В описанной выше последовательности выполняется измерение напряжения вторичного источника, адрес которого был зафиксирован в двоичном счетчике 78 блока (фиг. 4). Измерение всех источников электропитания производится при проверке и регулировке системы электропитания в соответствии с алгоритмом, приведенным на фиг. 11. Отключается режим профконтроля с пульта инженера с целью измерения реальных значений вторичных источников и блокировки возможного запроса.на прерывание. Микропрограммно сбрасывается регистр 67 режимов блока 5 (фиг. 3) и адрес вторичного источника считывается в рабочие регистры процессора из двоичного счетчика 78 блока 6 сравнения (фиг. 4). После этого устанавливается режим измерения и ожидается установка третьего бита в регистре 103 состояния блока 4 синхронизации (фиг. 8), по которому читается сформированный код напряжения и впоследствии выводится на печать. Сбрасывается режим измерения для приведения устройства в исходное состояние, а затем устанавливается режим оперативного контроля с целью модификации адреса вторичного источника электропитания. Микропрограммно считывается адрес вторичного источника из двоичного счетчика 78 блока 6 (фиг. 4) и сравнивается со вторым рабочим регистром процессора. При увеличении адреса в двоичном счетчике 78 па единицу произойдет несравнепие, после чего информация из него переписывается во второй рабочий регистр, и второй рабочий регистр сравнивается с первым. Их неравенство означает, что еще не все источники измерены. Поэтому сбрасывается режим оперативного контроля и начпнается цикл измерения следующего вторичного источника электропитания. Последовательность повторяется до тех пор, пока все вторичные источники не будут измерены. Формирователь 1 тактовых сигналов (фиг. 7) предназначен для формирования первого Т1 и второго Т2 тактовых сигналов, синхронизирующих работу устройства. Генератор 98 вырабатывает периодический сигнал, поступающий на синхровход счетчика 99. При отсутствии тактового сигнала Т2 на выходе элемента И 101, на входе управления счетчика 99 устанавливается режим счета. Когда в счетчике 99 оказываются определенные коды, по импульсу с генератора 98 на выходе элементов И 100 и 101 появляется тактовый сигнал Т1 или Т2. Задержка во времени между передними фронтами Т1 и Т2 равна периоду сигнала с выхода генератора 98. Тактовый сигнал Т2 задает режим сброса счетчика 99, который сбрасываетс:я по заднему фронту следующего импульса генератора 98. Период следования тактовых сигналов Т1 и Т2, который формируется счетчиком 99, определяется суммарным временем формирования аналогового опорного сигнала формирователем 3 при установке новых допустимых значений и временем установки сигнала на выходах компараторов при сравнении напряжения вторичного источника электропитания с опорным аналоговым сигналом. Таким образом, использование предлагаемого устройства обеспечивает организацию контроля и восстановление уровней напряжения вторичных источников электропитания процессора ЭВМ. Это позволяет поддерживать напряжения, питающие электрорадиоэлементы процессора, главным образом интегральные микросхемы, на уровнях, максимально приближенных к их номинальным значениям.

30 Реализация указанных возможностей обеспечивает оптимальные условия эксплуатации микросхем, параметры которых, в особенности помехоустойчивость, существенно зависят от величины питающих напряжений, что способствует повыщению помехоустойчивости процессора, увеличивает срок службы микросхем, повыщает надежность функционирования процессора и ЭВМ в целом. Известно, что напряжение в электрической сети подвержено существенным изменениям в течение суток при подключении и отключении массовых потребителей электроэнергии. Колебания уровней- напряжения первичного источника питания сказываются на напряжении вторичных источников электропитания и поэтому использование предлагаемого устройства позволяет значительно уменьщить влияние нестабильности первичного источника электропитания на функционирование процессора ЭВМ. Кроме того, предлагаемое устройство позволяет выполнять тесты микродиагностики в режиме автоматического профконтроля с целью прогнозирования отказов в оборудовании процессора, а также в целях обнаружения и локализации неисправностей, вызывающих неустойчивое функционирование процессора ЭВМ, что в несколько раз сокращает время выполнения микродиагностики по сравнению с временем ее выполнения при ручном переключении режимов профилактического контроля.

26

зг

гз

25

Р

X

fui2

С начало J

Ъапись инсро/зпации состояния в оКласть регистрации ошибок

. (с сриг.10)

Занесение HJUBU 8 регис/пр режиг ов 67

Занесение единицы Во Bmapoi и третий разряды регистра режипове IffC/ сриг.ю) результат унножения равен НУЛЮ Логическое умножение. uHcfiopnanuu uj pesucrpoS отрицательного просрконграля я и сдвива /У Jlozu4eckoe сложение инсрарпации uj регистро отрицательного прос/зконгрояя 11 и сдвига III Резальтчт сложения в pe&ucmp отрицательного просрконтрапя If. исключающее IUU над инФорпацией ил регистров положительного праронтроля 10 и сдвига 14 Результат операции в регистр положительного профконтроля 10 (с сригх; Занесение налей в регистр режимоб 67 Занесение единицы Во Второй разряд регистра реЖипоВ67

| Патент США № 4016408, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство контроля электропитания процессора | 1983 |

|

SU1096649A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1984-04-20—Подача