соответственно с входами элементов ИЛИ первой группы, отличаю щееся тем, что, с целью повышения быстродействиями точности вычисления в него введены элемент ШМ, И а.в каждый вычислительньй блок введены третий и четвертый элементы И, третья, четвертая, пятая, шестая и седьмая группы элементов И, второй и третий элементы ИЛИ, вторая группа элементов ИЛИ, первый и второй элемен ты ИСКЛЮЧАЮ1ЧЕЕ ИЛИ, причем входы элемента ИЛИ соединены соответственно с входами знаковых разрядов первого и второго регистров первого вычислительного блока, а iero выход - с первым входом элемента И, второй вход которого соединен с ванной управления операцией деления устройства, а,выход - с информационным входом триггера первсио вычислительного блока, вход, запуска устройства соединен с управляющими входами триггера, первого, второго и третьего регистров j-ro («t-n) вычислительного блока, шина управления операцией умножения устрой ства соединена с первыми входами элементов И четвертой и седьмой группы, с первыми ВХОДШ4И третьего элемента ШШ и четвертого элемента И,шина .управления операцией деления устройст за соединена с первыни входами элемен TQB И шестой группы, с вторым входом Т1 етьегр элемента ИЛИ и с первым входом третьего элемента И, шина управления операцией извлечения квадратного корня устройства соединена с пер тят входами элементов И третьей и пятой групп, BHxojEpa элементов ИЛИ вто рой группы элементов /-го вычислитель ного блока ( - (h-1)) соединены с входами разрядов первого регистра ()-ro вычислительного блока, выход второго элемента ИЛИ .j-ro вычислитель ного блока соединен с входом первого разряда третьего регистра (j-t-l)-ro вычислительного блока, выходы элементсив ШШ второй группы п-го вычислительного блока являются третьим ин)рмационным выходом устройства, причем в каждом вычислительном- блоке 1 77 третьего и четвертого элементов И соединены соответственно с входами второго элемента ШШ, выходы элементов И с третьей по седьмую группы .соединены соответственно с входами элементов ИЛИ второй группы, (п+1)-й выход которой соединен с вторым входом четвертого элемента И, второй вход третьего элемента И соединен с инверсным выходом первого элемента ИСКЛЮЧАЮЩЕЕ ШШ пр.ямой выход которого соединен с BTopibw входом второго , элемента И, выхода) разрядов первого регистра соединены со сдвигом на один разряд влево с вторыми входами элементов И третьей группы и со сдвигом на один разряд вправо - с вторыми входами элементов И четвертой группы,, знаковый разряд второго регистра соединен с первьм входом первого элемента ИСКЛЮЧАКШЩЕ ШШ, второй вход которого соединен с прямьм выходом знакового разряда сумматораг вычитателя и третьими входами элементов И третьей группы, инверсный выход знакового разряда сумматора-, вычитателя соединен с вторым входами элементов И пятой группы, выходы разрядов сумматора-вычитателя соединены со сдвигом на один разряд влево с третьими входами элемента- ми И пятой группы и со сдвигом на один разряд вправо - с вторьми входами элементов И седьмой группы, ВЫХОД п-гО разряда третьего регистра соединен с первым входом второго элемента ИСКЛЮЧАКЩЕЕ ИЛИ, с третьими входами элементов И пятой группы, с вторыми входами элементов И третьей и шестой групп, выход (п+О-го разряда третьего регистра с6ё;п;инен с вторым входом второго элемента ИСКЛЮЧАЩЕЕ ШШ, прямой выход которого соединен с третьими входами элементов И седьмой группы, инверсный выход второго элемента ИСЮЮЧАЮОШЕ 1}ДИ соединен с третьими входами элементов И четвертой группы, выход Tpieтьего элемента ШШ соединен с вторыми входами элементов И второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Арифметическое устройство | 1985 |

|

SU1290299A1 |

| Конвейерное арифметическое устройство | 1984 |

|

SU1203511A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Арифметическое устройство | 1981 |

|

SU993252A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

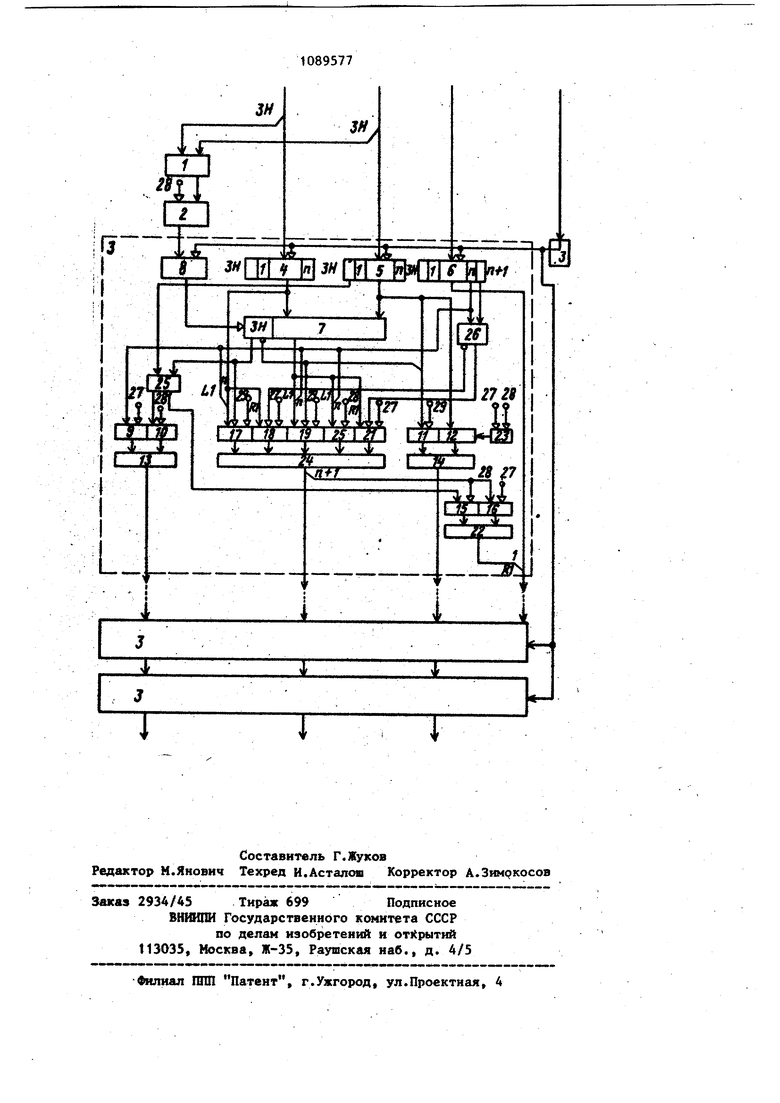

АРИФМЕТ№ЕСКОЕ УСТРОЙСТВО, содержащее п( h- число разрядов) вычислительных блоков, каждый из которых содержит три регистра, сумматор-вычитатель, триггер, первый и второй элементы И, первую и вторую группы элементов И, первый элемент ШШ, первую группу элементов ИЛИ, причем входы разрядов первого, второго и третьего регистров первого вычислительного блока соединены соответственно с первым, вторьм и третьим информационньми входами устройства, выходы разрядов со знакового по (п-1)-й третьего регистра j-ro вычислительного блока (, , (п-1)) соединены со сдвигом на один разряд вправо с входами разрядов третьего регистра (j+1)-ro вычислительного блока, выход первого элемента ШШ f-ro вычислительного блока соединен с единичным входом триггера (j+1)-ro вычислительного блока, выходы элементов ИЛИ первой группы j-ro вычислительного блока соединены ответственно с входами разрядов второго регистра (j+1)-ro вычислительного блока, выходу разрядов третьего регистра п-го вычислительного блока являются первьвм информационным вьгхо-. дом устройства, выходы элементов ИЛИ первой группы h-го вычислительного блока являются вторым информационным выходом устройства, шина управления операцией умножения устройства соединена с первив входом элемента И каждого вычиСлительняго блока, шина управлении операцией деления устрой|ства соединена с первым входом второго элемента И каждого вычислительного блока, шина управления ъпер ацией извлечения квадратного корня соеди нена с первьм входом элементов И первой группы каждого вычислительного .блока, причем в каждом вычислительном блоке единичный выход триггера (Л соединен с управляющим входом сумма,тора-вычислителя, выходы информационных разрядов первого регистра соединены соответственно с первой группой информационных входов сумматора-вычитателя, выходы разрядов с первого по п-й второго регистра соединены соответственно с второй группой иноо со ел формационных входов сумматора-вычитателя, с вторьми входами элементов И с второго по п-й первой группы элементов И и с первыми входами элементов И с первого по п-й второй группы элементов И, второй вход первого эле1 юнта И первой группы соединен с инверсным выходом знакового разряда сумматора-вычитателя, выход п-го разряда третьего регистра соединен с вто тцгым входом первого элемента И, выходы первого и второго элементов И соединены соответственно с входами первого элемента ИЛИ, выходы элементов И первой и второй групп соединены

1

Изобретение относится к вычисли1тельной технике ,и может быть использовано при построении вычислительных устройств для выполнения операций

умножения, деления, извлечения квадpiaTHoro корня при обработке больших массивов многоразрядных чисел.

Известно арифметическое устройство, содержащееп последовательно соединенных однотипных блоков, каждый из которых содержит два регистра, формирователь п+1 старших разрядов, два триггера и элемент И ГО.

Однако это устройство предназначено для обработки массива чиселодновременно, а не массива из пар чисел, и не может выполнять операции деления и извлечения квадратного корня.

Наиболее близким к предлагаемому является устройство, содержащее п последовательно соединенных вычислительных блоков, каждый из которых содержит три регистра, сумматор, блок анализа, триггер, первый коммутатор, второй коммутатор, содержащий первый и второй элементы И-ИЛИ, причем в каждом из последовательно соединенных блоков группа разрядных выходов первого регистра соединена с первой группой соответствующих разрядных входов сумматора, первый вход первого коммутатора соединен с первой и второй управляющими шинами устройства, второй вход первого коммутатора соединен с третьей управляющей шиной устройства, а третий вход первого коммутатора - с выходом блока анализа, вход которого соединен с выходом знакового разряда сумматора, выход первого коммутатора соединен с К-м разрядным входом второго регистра (где К«1, ...,п ), i-e прямые выходы второго регистра К-го блока соединены с 1-й входами второго регистра (К+О-й ячейки, а (К+1)-й выход второго регистра К-го блока соединен с четвертым входом первого коммутатора (К+О-го блока, К-й инверсный выход второго регистра К-й ячейки соединен с первым входом первого элемента И-ИЛИ второго коммутатора К-го блока, второй вход первого элемента И-ШМ второго коммутатора соединен с первой и второй управлякодими шинами, а третий и четвертый входы - с третьей управляющей шиной и (К+1)-м , прямым выходом второго регистра, соответственно выход первого элемента И-ШШ второго коммутатора соединен с вторым входом сумматора, выход i-ro разряда сумматора К-го блока соединен с ()-M разрядным входом, первого

регистра (к+О-го блокаj i-ый разрядный выход третьего регистра К-го блока соединен c(i-t)-M входом, третьего регистра (К+1)-го блоки, разряд третьего регистра соединен с выходом триггера и с первым входом второго элемента И-ИЖ второго коммутатора, второй и третий входы которого соединены с первой управлянлцей шиной и второй и третьей управляющими шинами соответственно, а вход триггера соединен с выходом блока анализа. Устройство содержит также п трупп элементов ИЛИ и И, а второй коммутатор каждой из последовательно соединенных блоков дополнительно содержит (п-1) элементов И, причем каждая группа элементов ШШ и И содержит первый и второй элемент И и элемент ИЛИ, причем в каждой группе элементов ИЛИ и И первые входы первого и второго элементов И соединены с первой управляющей шиной устройства, вторые входы первого н второго элементов И соединены с второй я третьей управляющими шина1 1и устройства соответственно, выходы первого и второго элементов И соединены соответственно с первым и вторым Ш|1ходами элемента ЩШ, выход элемента ШШ соединен с соответствующим входом второго регистра первого блока устройства и с четвертым входом первого коммутатора первого блока устройства, причем в каждом втором коммутаторе калд&й из последовательно соединенных блоков пятый я шестой входы первого элемента И-ШШ соединены с первыми входами (h-1) элементов И и с выходом второго элемента И-Шда, четвертый вход второго элемента соединен с выходом первого разряда третьего регистра, вторые входы (rt-1) элементов И соединены с соответствующими инверсными выходами разрядов второго регистра, а выходы (n-t) элементов И соединены с вторыми входами соответствукйдих разрядов сумматора.

Результат операции умножения получается с точностью до п-го разряда, а операция деления и извлечения квадратного корня выполняются над п-разрядными числами .21.

Недостатками устройства являются относительно невысокое быстродействие при выполнении операций деления и извлечения квадратного корня, а также низкая точность вычисления при выполнении операции умножения, деления, извлечения корня. .Цель изобретения - повьппение быст родействия устройства и точности вычисления. Поставленная цель достигается тем что в арифметическое устройство, содержащее h(h- число разрядов) вычислительных блоков, каждый из ко торых содержит три ре гистра, сумматор-вычитатель, триггер, первый и. второй элементы И, первую и вторую группу элементов И, перв элемвнтЯЛИ первую группу элементов ИЛ причем входы разрядов первого, второго и третьего регистров первого вы числительного блока соединены соответственно с первым, вторым и третьи информационньми входами устройства, выходы разрядов со знакового по (п-1)-й третьего регистра j-го вычис лительного .блока (, ..., (n-i)) соединены со сдвигом на один разряд вправо с входами разрядов третьего регистра (j+1)-ro вычислительного блокаf выход первого элемента ИЛИ -го вычислительного блока соединен с единичным входом триггера (/+1)-го вычислительного блока, выходы элемен тов ИЛИ первой группы j-ro вычислительного блока соединейы соответственно с выходами разрядов второго ре гистра (j - 1) -го вычислительного блока., выходы разрялоъ третьего регистра п-го вычислительного блоха являются первым информационным выходами устройства, выходы элементов ИЛИ перас группы п-го вычислительного блока являются вторым информационным выходом устройства, шина управления операцией умножения устройства: соеди нена с первым входом первого элемента И каждого числительного блока, шина управления операцией деления устцюйства соединена с первым входом второго элемента И каждого вычислительного блока, шина управления операцией извлечения квадратного корня соединена с первыми входами элементов И первой группы каждого вычисли.тельного блока, причем в каждом вычислительном блоке единичный выход триггера соединен с управляющим входом сумматорЗ-вычитателя, выходы информационных разрядов первого регист ра соединены соответственно с первой группой информационных входов суиматора-вычитателя, выходы разрядов с первого по п-й второго регистра соединены соответственно с второй группой информационных входов сумматоравычитателя, с вторыми входами элементов И с второго по Ь-й первой группы Элементов И и с первь1ми входами эле|ментов Ис первого по п-й второй группы элементов И, второй вход первого элемента И первой группы соединен с инверсным выходом знакового разряда сумматора-вычитателя, выход h-ro разряда третьего регистра соединен с вторым входом первого элемента И, выходы первого и второго элементов И соединены соответственно с входами первого элемента ИЛИ, выходы элементов И первой и второй групп соединены соответственно с входами элементов ИЛИ первой группы, введены элементы ШШ, элементы И, а в каждый вычислительный блок введены третий и четвертый элементы И, третья, четвертая, пятая, шестая и седьмая группы элементов И, второй и третий элементы ИЛИ, вторая группа элементов ИЛИ, цервый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем входы элеьюнта ИЛИ соединены соответственно с входакш знаковых разрядов первого и второго регистров первого вычислительного блока, а его выход - с первым входом эле мента И, второй вход j которого соединен с шиной управления операцией деления устройства, а выход - с информационным входом триггера первого вспомогательного блока, вход начальной установки устройства соединен с управляющими входами триггера, первого, второго и третьего регистров j-rO (j«t-n) вычислительного блока, шина управления-операцией умноженияустройства соединена с первьвш входами элементов И четвертой и седьмой груптш, с первыми входами третьего элемента ИЛИ и четвертого элемента И, шина управления операцией деления устройства соёдинена с первьми входами элементов И естой групгш, с вторьм входом третьего элемента ИЛИ и с первым входом третьего элемента И, шина управления операцией извлечения квадратного корня устройства соединена с первыми входами элементов И третьей и пятой групп, выход элементов ИЛИ второй группы j-ro вычислительного блока ( - (п-1)) соединен с входами разядов первого регистра (j + 1)-ro. вычис7.108 лительного блока, выход второго элемента ИЛИ j-ro вычислительного блока соединен с входом первого разряда третьего регистра (j+1)-ro вычислительного блока:, выходы элементов ИЛИ второй группы вычислительного блока являются третьим информационным выходом устройства, причем в каждом вычислите л brtoNf блоке выходы третьего и четвертого элементов И соединены соответственно с входами второго элемента ИЛИ, выходы эле)ментов И е треть ей по седьмую группы соединены соответственно с входами элементов ИЛИ .второй группы, (1У+1)-й выход которой соединен с вторым входом четвертого элемента И, второй вход третьего элемента И соединен с четвертым выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пря мой выход которого соединен с вторым входом второго элемента И, выходы раз рядов первого регистра соединены со сдвигом на один разряд влево с вторыми входами И третьей группы и со сдви гой на один разряд вправо - с вторыми входами элементов И четвертой группы, знаковый разряд второго регистра соединен с первым вхсздом первого элемента ИСКЛЮЧАЮВ1ЕЕ ИЛИ, второй вход которого соединен с выходом знакового разряда су1О4атора-вычитателя и с третьими входами элементов И третьей группы, четвертый выход, знакового разряда сумматора-вычитателя соединен с вторыми входами элементов И пятой груптш, к 1ходы разрядов сумматоравычитателя соединены со сдвигом на один разряд влево с третьими входами элементов И пятой группы и со сдвигом на один разряд вправо - с вторыми входами элементов И седьмой груп-т пы, выход, h-го разряда третьего регистра соединен с первьш входом второ го элемента ИСКЛЮЧ ЩЕЕ ИЛИ, с третьими входами элементов И пятой группы,45 с вторыми входами элементов И третьей и шестой групп, выход (п+1)-го разряда третьего реги1стра соединен с вторым входом второго элемента ИСЮЖЬ ЧАКИЩЕ ИЛИ, прямой выход которого 50 соединен с третьими входами элемен- ; тов И седьмой группы, инверсный выход второго элемента ИСКШ)ЧАЩЕЕ 1ЛЩ сое динен с третьими входами элементов И четвертой группы, выход третьего j элемента ИЛИ соединен с вторыми вxoдa ш элементов И второй группы. 7 На чертеже дана структурная схема арифметического устройства. Арифметическое устройство содержит элемент ИЛИ 1, элемент И 2 и п вычислительных блоков 3, каждый вычислительный блок 3 содержит первый 4, второй 5, третий 6 регистры, сумматорвычитатель 7, триггер 8, первый 9 и второй 10 элементы И, первая 11 и вторая 12 группы элементов И, первь1й 13 элемент ИЛИ, первая группа 14 элементов И1Н, третий 15 и четвертый 16 элементы И, третья 17, четвертая 18, пятая 19, шестая 20 и седьмая 21 группы элементов И, второй 22 и третий 23 элементы ИЛИ, вторая группа 24 элементов ИЛИ, первый 25 и второй 26 элементы ИСКГВОЧАИЩЕЕ ИЛИ, шины 27, 28 и 29 управления операциями соответственно умножения,.деления и извлечения квадратного корця устройства. Устройство работает следующим образом. Умножение производится с мпадших разрядов множителя со сдвигом частного произведения вправо при неподвижном множимом. Частное произведение в зависимости от значения/t H.h+1 разряда множителя получается или путем сложения содержимого перрого регистра 4 с содержимым второго регистра 5 ( ()1), или путем вычитания содержимого второго регистра 5 из содержимого первого регистра 4 (ti-1; ), или в качестве частного произведения берется содержимое первого регистра 4 (). Деление сводится к выполненшо последовательности вычитаний (знак делителя равен знаку (-1)-го частного остатка) или суммирований (знак делителя не раве знаку (i-l)-ro частного остатка) делителя сначала с делимым. а затем с образовавшимся в процессе деления частных остатков и сдвигу частных остатков на один разряд влево. После каждого вычитания или су о4ИрЬв1ания определяется значение f-го разрядного частного: -1 (знак делителя равен знаку f-ro частного остатка) или О (знак делителя не равен знаку i-ro частного остатка) Извлечение квадратного корня саодится к выполнению последовательности вычитанийчисел, полученных в процессе вычисления сначала иэ подкоренного выражения, а затем из частных подкоренных выражений, за которые берутся или результат вычитания (результат вычитания положительный) или предыдущее подкоренное выражение (ре зультат вычитания отрицательный), сдвинутое нд один разряд влево. Первое число, которое вычитается, равно 0,01. Знак результата этого вычитания определяет старший разряд результата извлечения квадратного корня (результат положительный - старший разряд , отрицательный ), остальные разряды (В, ..., Bj.) определяются аналогично. Последукнцне числа вычитания получаются путем записи кода 01 в два разряда после разрядов результата извлечения корня. В исходном состоянии все информационные и управляющие входы находятся в нуле. При операции умножения на шину 27 управления операцией умножения подается единичный сигнал, а на тины 28 и 29 управления операциями деления и извлечения квадратного, кор ня - нулевой. Работа устройства начинается по приходу тактовых импульсов на вход запуска устройства. По первому тактовому импульсу в триггер 8 и первый регистр 4 первого вычислительного блока 3 записывается нуль, а во второй 5 и третий 6 регистры - соответственно множимое и множитель. Информация на выходе триггера 8 первого вычитательного блока 3 задает сумматору-вычитателю 7 этого же вычитательного блока 3 операцию вычитания (нуль на выходе триггера 8). Значение и-го разряда множителя, проходя через элемент И 1 и элемейт ИЛИ 20, поступает на информационньй вход триггера 8 второго вычислительного блока 3. Значение h-ro и (ti + O-ro разрядов множителя поступают на второй элемент ИСКЛЮЧАЮ ЩЕЕ ИЛИ 26 и в случае, если в п-м и ()-M разрядах записана одна и те же информация, то на прямом выходе -ЭТОГО элемента будет нулевой сигнал, а на инверсном - единичный сигнал, а в случае, когда в п-м и (п+1)-м разрядах записана информация, наоборот. При единичном сигнале на прямом выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 разрешается прохождение информации с выходов сумматора-вычитателя 7, сдвинутой на один разряд вправо, через седьмую группу 21 элементов И и вторую группу 24 элементов ИЛИ на информационный вход первого регистра 4 второго вычислительного блока 3, а в случае единичного сигнала на инверсном выходе второго элемента ИС|ашЧАВДЕЕ ИЛИ 26 разрешается прохождение информации с выходов первого регистра 4, сдвинутой вправо на один разряд, через четвертую группу элементов И и вторую группу 24 элементов ИЛИ на информационный вход первого регистра 4 второго вычитательиого блока 3. Информа1шя (n-i-l)-ro разряда с выхода второй группы 24 элементов ИЛИ проходя через четвертый элемент И 16 и второй элемент ИЛИ 22 поступает на первый разряд информационного входа .третьего регистра 6 второго вычислительного блока 3, а на остальные входы этого регистра поступает инфор1 1ация с третьего регистра 6 первого вычислительного блока 3, сдвинутая вправо на один разряд. Множимое с выходов второго регистра 5 первого вычислительного блока, проходя через вторую группу 12 элементов И, первую группу 14 элементов ИЛИ, поступает на вход второго регистра 5 второго вычислительного блока 3. По второму тактовому импульсу информация с выходов первого вычислительного блока 3 поступает в триггер 8, в первый 4, второй 5 и третий 6 регистры второго вычислительного блока 3. Одновременно в первый вьптслительный блок 3 записывается новая информация для выполнения операции умножения. В каждом вычислительном блоке 3 выполняется одна итерация алгоритма умножения. Результат умножения с удвоенной точностью получается на выходах второй группы 24 элементов ИШ, второго элемента ИЛИ 22 и третьего регистра 6 с п-го вычислительного блока 3 после прохождения данных через все вычислительные блоки 3, т.е. после И-го тактового импульса. При операции деления на шину 28 управления операцией деления подается единичный сигнал, а на шины 27 и 29 управления операциями умножения и извлечения квадратного корня - нулевой. Делимое с первого информационного Входа устройства поступает на входы первого регистра 4 (старшие разряды полуслова) и с третьего информационного входа устройства на входы третьего регистра 6 (младшие раэрядь полуслова, причем в знаковый разряд записывается младший разряд этого полуслова) первого вычислительного блока 3. Делитель с второго информационного входа устройства поступает на информационный вход второго регистра 5 первого вычислительного блока 3. Знаковые разряды делимого и делителя поступают на элемент ИЛИ 1 и через элемент И 2 на информационный вход триггера 8 первого вычислительного блока 3. Запись йн.формации в триггер 8 и регистры 4 - 6 вычислительных блоков 3 происходит по первому тактовому Го4пульсу. Знак ре.зуль- ата, псшученный на сумматоре-вычитателе 7;первого вычислительного блока 3, после выполнения операции суммирования (единица на выходе триггера 8) или вычитания (нуль на выходе триггера 8) поступает на первый элемент ИСКЛЮЧАЮЩЕЕ ЙЖ 25. В случае его равенства со знаком делителя на прямом выходе этого элемента будет нулевой сигнал, а в случае неравенства - единичный. Информация с прямого выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25,. проходя через Ьторой элемент И 10 и первый элемент ИЛИ 13, прступает на информационнь вход триггера 8 второго вычислительного блока 3, а информация с инверсного выхода этого элемента, проходя через третий э.лемент И 15 и второй элемент ИЛИ 22, поступает на вход тактового разряда третьего регистра 6 вычислительного блока 3. На остальные входы этого регистра поступает информация с треть-его регистра 6 первого/вычислительного блока 3, сдвинутая вправо на один разряд. Информация из сумматора-вычитателя 7 первого вычислительного блока 3, сдвинутая влево на один разряд, проходя через шестую группу элементов И и вторую группу 24 элементов ШЩ, поступает на вход первого регистра 4 второго вычислительного

:блока 3. Делитель с выхода второго . регистра 5 первого вычислительного блока 3, проходя через вторую группу 12 элементов И и первую труппу 14 элементов ИЛИ, поступает на вход второго регистра 5 второго вычислительного блока 3. По второму тактовому импульсу информация с выходов первого вычислительного блока 3 поступает в

триггер 8, в первый 4, второй 5 и третий 6 регистры второго вычислительного .блока 3. Одновременно в первый вычислительный блок 3 поступает новая информация Для выполнения операции деления. В каждом вычислительном блоке выполняется одна итерация алгоритма деления. Результат деления снимается с выходов второго элемента ИЛИ 22 и третьего регистра 6 П-го вычислительного блока 3 после прохождения данных через все вычислительные блоки 3, т.е. после h-ro тактового импульса. Причем информация на выходе второго 22 элемента ИЛИ является младшим разрядом результата.

При извлечении квадратного корня на шину 29 управления операцией извлечения квадратного корня.подается единичный сигнал, а на шины 27 и 28 управления операциями умножения и деления - нулевой. Подкоренное число с первого информационного Bxoji a устройства поступает на входы первого регистра 4 (старшие разряда полуслова) и с третьего информационного входа устройства на входа третьего регистра 6 (младшие разряды полуслова) первого вычислительного блока 3. С второго информационного входа устройства на ВХОФ1 регистра 5 первого вычислительного блока поступают нули, кроме второго разряда, на вход которого постуйает единица. По переднему фронту первого тактового импульса происходит запись информации в триггер 8 и регистры 4-6 вычислительных блоков 3. На сумматоре-вычислителе 7 вычислительных блоков 3 происходит вычитание (нуль на выходе триггера 8) содержимого второго регистра 5 из содержимого первого регистра 4. В случае положительного результата вычитания в первом вычислительном блоке 3 этот результат, содержащийся влево на один разряд, проходя через пятую группу 19 элементов И и вторую группу 24 элеменjTOB ИЛИ, поступает на вход первого регистра 4 второго вычислительного блока 3, а в случае отрицательного результата на вход первого регистра .поступает информация с выходов первого регистра 4 первого вычислительного блока 3, проходящая через третью груп пу t7 элементов И и первую группу 14 элементов ИЛИ, сдвинутая влево на одии разряд. Информация на входы второго регистра 5 второго вычислительного блока поступает через первую группу 11 Элементов И и первую группу 14 элементов ИЛИ. Старшие разряды этой информации (от 1-го до (i-l)-ro разряда) для 1-го вычислительного блока соответствуют информации на этих же разрядах регистра 5 i-го вычислительного блока 3, а младшие (от (i+1)-ro до п-го) - информации младших разрядов этого же регистра, сдвинутой вправо на один разряд, т.е. информация на 1-м разряде регистра 5 i-ro вычислительного блока 3 соответствует информации на выходе ()-ro разряда регистра 5 (+.1)-го вычислительного блока 3. Информация на выходе т-го разряда регистра 5 второго вычислительного блока 3 соответствует инверсному значению знака результата вычитания в первом вычислительном блоке 3. По переднему фронту второго тактового импульса информация с выходов первого вычислительного блока 3 переписывается в триггер 8 и регистры 4 6 второго вычислительного блока 3. Одновременно в первый вычислительный блок 3 записывается новая информация для выполнения операции извлечения квадратного корня. В каждом вычислительном блоке 3 выполняется одна ите™ рация алгоритма извлечения квадратного корня. Результат извлечения квадратного корня получают на выходе первой группы 14 элементов ИЛИ п-го решающего блока 3 после прохождения через все вычислительные блоки 3, т.е. после -го тактового импульса. Кредлагаемое арифметическое устройство работает по конвейерному принцилу. Его быстродействие при обработке массивов чисел определяется временем выполнения одной итерации в вычислительном блоке 3 + 1 гдвЬсд)- слежения на сумматоревычитателе 7; tn - время задержки информации элементом И; йлм время задержки информации элементом ИЛИ. Быстродействие прототипа при выслении операций деления и извлечея квадратного корня., которые выполются за два полутакта, определяетпо формуле (t,,.), е - время сложения на сумматоре;время анализа знака сумматора в блоке анализа переполнения;время срабатывания триггера переполнения; время, затраченное на сдвиг информации в первом регистре. По сравнению с прототипом при вылнении операции деления и извлечея квадратного корня бь стродействие едлагаемого арифметического устройва выше.в 2(t t +t +-t +i +i . с CM- VZtnA, При построении арифметического тройства на микросхемах серии 155 разрядности регистров и сумматоЛП ив 16 i 20 НС. Тогда 150 НС, НС, при этом увеливается быстродействие в Т 380 . ,5 Т 150 за.. Операция умножения в предлагаемом арифметическом устройстве выполняется с удвоенной точностью, т.е. результат получается 2п-разрядный. При выполнении операции деления производится деление 2п-разрядного делимого на п-разрядный делитель, а при выполнении операции извлечения квадратного корня он извлекается из 2п-раэряд |ого числа. Таким образом, точность выполнения рассматриваемых операций по сравнению с прототипом значительно вьш1е.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для одновременного выполнения арифметических операций над множеством чисел | 1973 |

|

SU479111A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметическое устройство | 1979 |

|

SU798825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-30—Публикация

1982-10-20—Подача