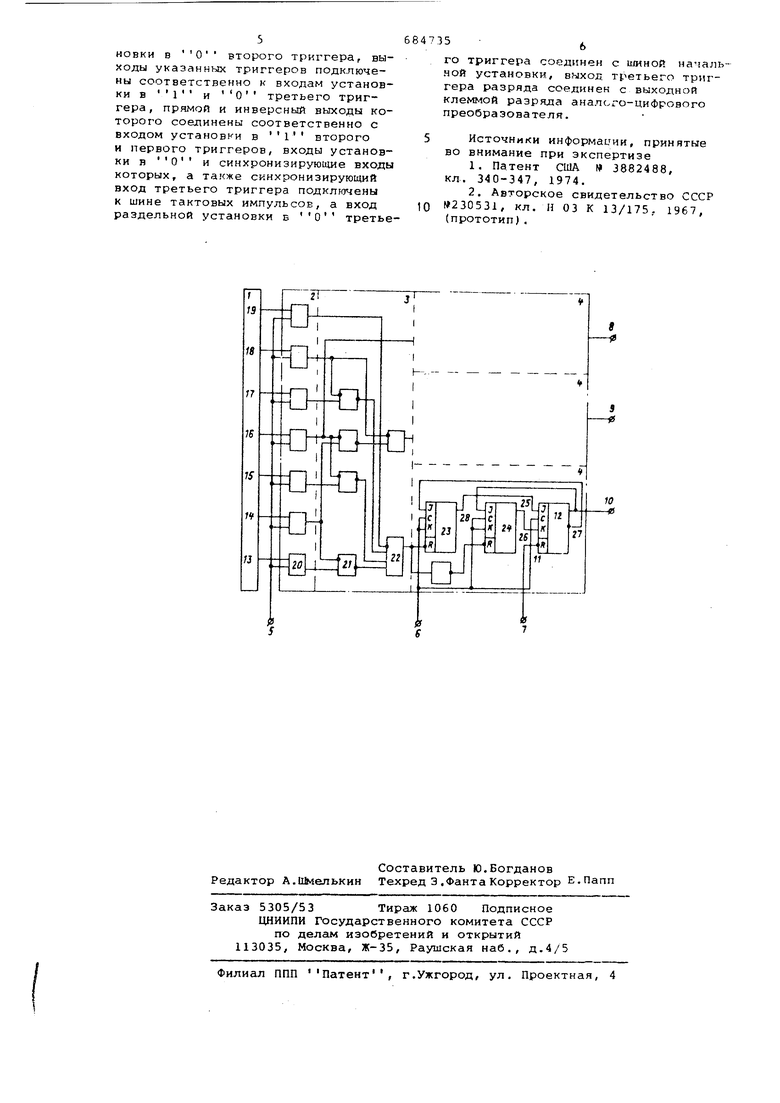

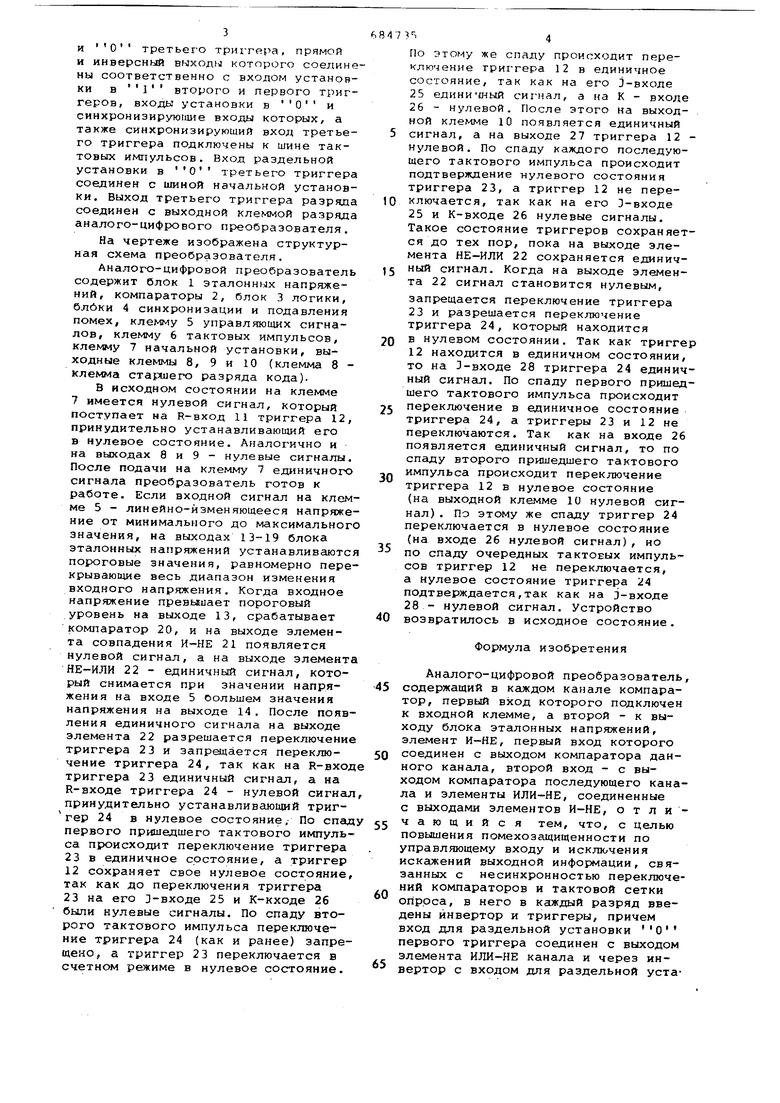

(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И О третьегО трштвра, прямой и инверсный выходы которого соедине ны соответственно с входом установ второго и первого триггеров, входы установки в синхрониэируюгале входы которых, а также синхронизирующий вход третьего триггера подключены к шине тактовых импульсов. Вход раздельной установки в О третьего триггера соединен с шиной начальной установки. Выход третьего триггера разряда соединен с выходной клеммой разряда аналого-цифрового преобразователя. На чертеже изображена структурная схема преобразователя. Аналого-цифровой преобразователь содержит блок 1 эталонных напряжений, компараторы 2, блок 3 логики, блбки 4 синхронизации и подавления помех, клемму 5 управляющих сигналов, клемму 6 тактовых импульсов, клемму 7 начальной установки, выходные клеммы 8, 9 и 10 (клемма 8 клемма старшего разряда кода). В исходном состоянии на клемме 7 имеется нулевой сигнал, который поступает на R-вход 11 триггера 12, принудительно устанавливающий его в нулевое состояние. Аналогично и на вьлходах 8 и 9 - нулевые сигналы. После подачи на клемму 7 единичного сигнала преобразователь готов к работе. Если входной сигнал на клем ме 5 - линейно-изменяющееся напряже ние от минимального до максимальног значения, на выходах 13-19 блока эталонных напряжений устанавливаютс пороговые значения, равномерно пере крывающие весь диапазон изменения входного напряжения. Когда входное напряжение превыиает пороговый уровень на выходе 13, срабатывает компаратор 20, и на выходе элемента совпадения И-НЕ 21 появляется нулевой сигнал, а на выходе элемент НЕ-ИЛИ 22 - единичный сигнал, который снимается при значении напряжения на входе 5 оольшем значения напряжения на выходе 14. После появ ления единичного сигнала на выходе элемента 22 разрешается переключени триггера 23 и запрещается переключение триггера 24, так как на R-вхо триггера 23 единичный сигнал, а на R-ЕХОде триггера 24 - нулевой сигнеи принудительно устанавливающий триггер 24 в нулевое состояние,- По спа первого пришедшего тактового импуль са происходит переключение триггера 23 в единичное состояние, а триггер 12 сохраняет свое нулевое состояние так как до переключения триггера 23 на его D-входе 25 и К-кходе 26 были нулевые сигналы. По спаду второго тактового импульса переключение триггера 24 {как и ранее) запре щеио, а триггер 23 переключается в счетноти режиме в нулевое состояние. По этому же спаду происходит переключение триггера 12 в единичное состояние, так как на его 3-входе 25единичный сиг-нал, а на К - входе 26- нулевой. После этого на выходной клемме 10 появляется единичный сигнал, а на выходе 27 триггера 12 нулевой. По спаду каждого последующего тактового импульса происходит подтверждение нулевого состояния триггера 23, а триггер 12 не переключается, так как на его D-входе 25 и К-входе 26 нулевые сигналы. Такое состояние триггеров сохраняется до тех пор, пока на выходе элемента НЕ-ИЛИ 22 сохраняется единичный сигнал. Когда на выходе элемента 22 сигнал становится нулевым, запрещается переключение триггера 23 и разрешается переключение триггера 24, который находится в нулевом состоянии. Так как триггер 12 находится в единичном состоянии, то на D-входе 28 триггера 24 единичный сигнс1Л. По спаду первого пришедшего тактового импульса происходит переключение в единичное состояние триггера 24, а триггеры 23 и 12 не переключаются. Так как на входе 26 появляется единичный сигнал, то по спаду второго пришедшего тактового импульса происходит переключение триггера 12 в нулевое состояние (на выходной клемме 10 нулевой сигнал) . По этому же спаду триггер 24 переключается в нулевое состояние (на входе 26 нулевой сигнал), но по спаду очередных тактовых импульсов триггер 12 не переключается, а нулевое состояние триггера 24 подтверждается,так как на D-входе 28 - нулевой сигнал. Устройство возвратилось в исходное состояние. Формула изобретения Аналого-цифровой преобразователь, содержащий в каждом канале компаратор, первый вход которого подключен к входной клемме, а второй - к выходу блока эталонных напряжений, элемент И-НЕ, первый вход которого соединен с выходом компаратора данного канала, второй вход - с выходом компаратора последующего канала и элементы ИЛИ-НЕ, соединенные с выходами элементов И-НЕ, о т л и чающийс я тем, что, с целью повышения помехозащищенности по управляющему входу и исключения искажений выходной информации, связанных с несинхронностью переключений компараторов и тактовой сетки опроса, в него в каркдый разряд введены инвертор и триггеры, причем вход для раздельной установки О первого триггера соединен с выходом элемента ИЛИ-НЕ канала и через инвертор с входом для раздельной установки в О второго триггера, выходы указанных триггеров подключены соответственно к входам установки в 1 и О третьего триггера , прямой и инверсный выходы которого соединены соответственно с входом установки в второго и первого триггеров, входы установки в О и синхронизируюише входы которых, а также синхронизируюгдий вход третьего триггера подклк чены к шине тактовых импульсов, а вход раздельной установки Б О третьего триггера соединен с шиной начальной установки, выход третьего триггера разряда соединен с выходной клеммой разряда аналого-цифрового преобразователя.

Источники информации, принятые во внимание при экспертизе

1.Патент США W 3882488, кл, 340-347, 1974.

2.Авторское свидетельство СССР №230531, кл. Н 03 К 13/175, 1967, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подавления помехпРи цифРОВОй пЕРЕдАчЕ иМпульСНОйпОСлЕдОВАТЕльНОСТи | 1977 |

|

SU840745A1 |

| Аналого-цифровой преобразователь | 1975 |

|

SU530449A1 |

| Селектор интервалов между импульсами | 1979 |

|

SU822341A1 |

| Формирователь импульсов по фронту и спаду | 1977 |

|

SU711671A1 |

| Формирователь импульсов | 1975 |

|

SU541279A1 |

| Формирователь импульсов | 1978 |

|

SU744943A1 |

| Расширитель импульсов | 1976 |

|

SU603109A1 |

| Цифровой фильтр | 1978 |

|

SU748803A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1316089A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

Авторы

Даты

1979-09-05—Публикация

1977-06-20—Подача