Изобретение относится к импульсно технике и предназначено для селекции импульсной последовательности в условиях воздействия кратковременных помех, например, в измерительных условиях . Известно устройство допускового контроля временных интервалов между импульсами, содержащее блок управления, счетчик, схекш, формирующие начало и конец строба, инвертор, триггер строба и выходную схему совпадения, определенньи образом соединенны между собой 1. Недостаток такого устройства состоит в том, что короткий единичный импульс помехи воспринимается как на чало или конец контролируемого временного интервала , а короткий нулево импульс помехи во время действия рабочего импульса воспринимается как интервал импульсами. Известно также устройство для подавления помех при цифровой передаче импульсной последовательности, содержащее времязадающий каскад, соединенный с первым входом логического элемента ИЛИ, выход которого через инвертор подключен к первому входу выходного логического элемента И р . Однако KpaTKOBpeMeHttiie помехи по управляющему входу нарушают правильное функционирование устройства, а наличие звена задержки и дифференциального звена ограничивают возможности егр применения. Кроме того, устройство не контролирует интервал между импульсами. Цель изобретения - повышение помехозащищенности и расширение функциональных возможностей устройства. Поставленная цель достигается тем, что в устройство подавления помех при цифровой передаче импульсной последовательиости, содержащее времязадаюощй каскад, соединенный с первым входом логического элемента ИЛИ, выход которого через инвертор подключен к

первому входу выходного логического элемента И, введены четыре триггера, инвертор и п времязадающих логических элементов И, входами подключенных к первому выходу времязадающего каскада, выходы времязадающих логических элементов И соединены с -ми входами логического элемента ИЛИ, выход которого подключен к 3 , С и К - входам первого триггера,

выход первого триггера подключен к входу времязадающего каскада, R - входы первого и второго триггеров соединены между собой, а S -вход первого триггера подключен к выходу логического элемента И, один из входов которого подключен к выходу третьего триггера и к 3 -входу второго триггера, а второй вход логического элемента И соединен с клеммой тактовых импульсов, с С-входами второго, третьего и четвертого триггеров и с К-входами третьего и четвертого триггеров, у которых через инвертор соединеньг R-входы, выход четвертого триггера

подключен к К-входу второго триггера, прямой выход которого пoдклю leн, к (+1)-ым входам второго (l-З) и (l-n)-ro времязадаюищх элементов И и к П-входу четвертого триггера,

а инверсный выход второго триггера подключен к второму входу выходного логического элемента И, к Л -входу третьего триггера и к первым входам 1-2, (1-п) -1 и (1-п)-2 времязадающих логических элементов И,

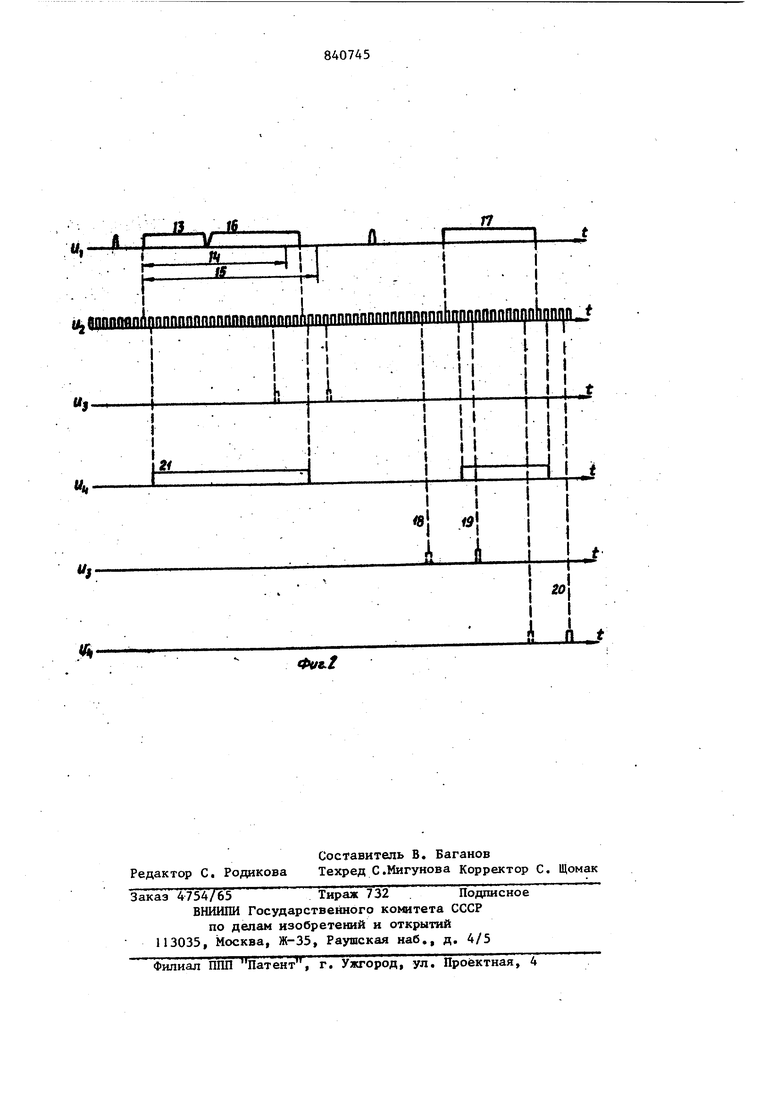

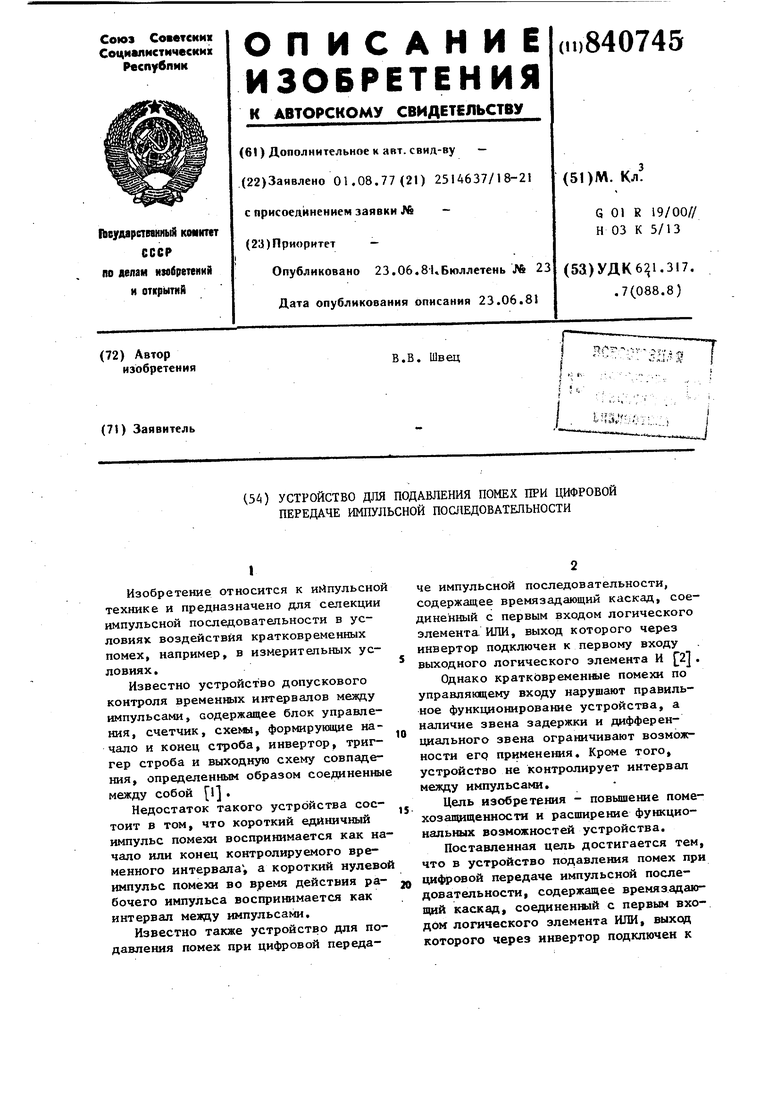

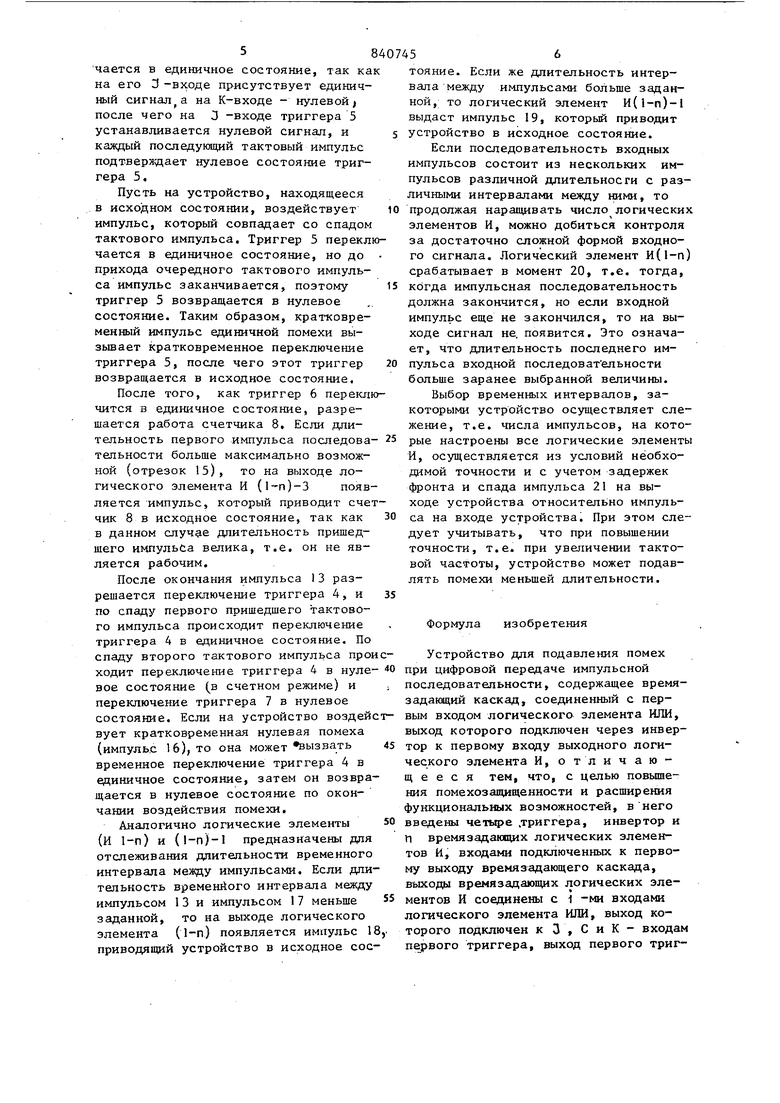

На фиг. 1 приведена принципиальная схема устройства; на фиг. 2 - временная диаграмма.

Устройство содержит выходные логические элементы И 1-1, 1-2,,.., (1-п) (1-п)2, (1-п)-3 и (1-п)-4 , инверторы 2 и 3, триггеры 4времязадающий каскад 8, логический элемент tLTM 9.

В исходном состоянии на входной клемме 10 присутствует нулевой сигнал, прицудительно устанавливающий триггеры 6 и 7 в нулевое состояние. Нулевой сигнал на выходе триггера 6 устанавливает счетчик 8 в нулевое состояние и запрещает его переключение. Логические элементы 1-1, 1-2, 1-3,..., (l-n)-l, (1-п)-2, (1-п)-3 и (1-п)-4 закрыты, причем на их

выходах присутствуют единичные сигналы, на выходе логического элемента ИЛИ 9 - нулевой сигнал и на выходе

инвертора 3 - нулевой сигнал, запрещающий работу выходного логического элемента И 1-1, на выходе устройства присутствует единичный сигнал. Входной сигнал на шине 11 принудительно устанавливает триггер 5 в нулевое состояние, логический элемент И (1-п)-3 закрыт, на выходе его - единичный сигнал.

Так как на выходе инвертора 2 присутствует единичный сигнал, разрешено переключение триггера 4, у которого на выходе - нулевой сигнал. По сигналу очередного тактового импульса на клемме 12 триггер 4 переключается в нулевое состояние (если до этого оп бьш в нулевом, то это состояние подтверждается), а по спаду каждого последующего-тактового импульса подтверждается его нулевое состояние. Триггер 7 не переключается даже после снятия сигнала начальной установки, так как на его 3 и К-входе - нулевые сигналы. После снятия сигнала начальной установки на входах триггеров 6 и 7 присутствует единичный сигнал, разрешающий переключение этих триггеров, но они не переключаются, так как нет соответствующих управлякмцих сигналов.

Пусть на устройство, находящееся в исходном состоянии, воздействует импульс входной последовательности, имеющий некоторую длительность, значение которой может изменяться от минимального до максимального. Минимальная длительность рабочего импульса 13 (фиг. 2) равна длительности отрезка 14, а максимальная - длительности отрезка 15. Единичный сигнал на входе устройства принудительно удерживает, триггер 4 в нулевом состоянии и разрешает переключение триггера 5.

Так как на 3 - входе триггера 5 присутствует единичный сигнал, топо спаду первого пришедшего тактового импульса происходит переключение триггера 5 в единичное состояние. Второй тактовый импульс проходит через логический элемент И (1-п)-3 , на выходе которого присутствует нулевой сигнал который поступает на S-БХОД триггера 6, переключая его в единичное состояние. По спаду второго тактового импульса происходит также переключение триггера 5 в счетном режиме в нуле,вое состояние, а триггер 7 переключается в единичное состояние, так ка на его 3 -входе присутствует единичный сигнал а на К-входе - нулевой| после чего на J -входе триггера 5 устанавливается нулевой сигнал, и каждый последуклций тактовый импульс подтверждает нулевое состояние триггера 5. Пусть на устройство, находящееся в исходном состоянии, воздействует импульс, который совпадает со спадом тактового импульса. Триггер 5 перекл чается в единичное состояние, но до прихода очередного тактового импульса импульс заканчивается, поэтому триггер 5 возвращается в нулевое состояние. Таким образом, кратковременный импульс единичной помехи вызьшает кратковременное переключение триггера 5, после чего этот триггер возврап1ается в исходное состояние. После того, как триггер 6 перекл чится в единичное состояние, разрешается работа счетчика 8, Если длительность первого импульса последова- 25 рые

тепьности больше максимально возможной (отрезок 15), то на выходе логического элемента И (l-n)-3 появляется импульс, который приводит счетчик 8 в исходное состояние, так как 30 в данном случае длительность пришедшего импульса велика, т.е. он не является рабочим.

После окончания импульса 13 разрешается переключение триггера 4, и 35 по спаду первого пришедшего тактового импульса происходит переключение триггера 4 в единичное состояние. По спаду второго тактового импульса происходит переключение триггера 4 в нулевое состояние (в счетном режиме) и переключение триггера 7 в нулевое состояние. Если на устройство воздейс вует кратковременная нулевая помеха (импульс 16), то она может вызвать временное переключение триггера 4 в единичное состояние, затем он возвращается в нулевое состояние по окончании воздействия помехи. Аналогично логические элементы (и 1-п) и (l-n)-l предназначены для отслеживания длительности временного интервала между импульсами. Если длительность временйого интервала между импульсом 13 и импульсом 17 меньше заданной, то на выходе логического элемента (l-n) появляется импульс 18 приводящий устройство в исходное сосИ, осуществляется из условий необходимой точности и с учетом задержек фронта и спада импульса 21 на выходе устройства относительно импульса на входе устройства. При этом следует учитывать, что при повышении точности, т.е. при увеличении тактовой частоты, устройство может подавлять помехи меньшей длительности.

Формула изобретения

Устройство для подавления помех тояние. Если же длительность интервала между импульсами больше заданной, то логический элемент И(1-п)-1 выдаст импульс 19, который приводит устройство в исходное состояние. Если последовательность входных импульсов состоит из нескольких импульсов различной длительности с различными интервалами между ними, то продолжая наращивать число логических элементов И, можно добиться контроля за достаточно сложной формой входного сигнала. Логический элемент И(1-п) срабатывает в момент 20, т.е. тогда, когда импульсная последовательность должна закончится, но если входной импульс еще не закончился, то на выходе сигнал не. появится. Это означает, что длительность последнего импульса входной последовательности больше заранее выбранной величины. Выбор временных интервалов, закоторыми устройство осуществляет слежение, т.е. числа импульсов, на котонастроены все логические элементы при цифровой передаче импульсной последовательности, содержащее времязадакщий каскад, соединенный с первым входом логического элемента ИЛИ, выход которого подключен через инвертор к первому входу выходного логического элемента И, отличающее с я тем, что, с целью повышения помехозащищенности и расширения функциональных возможност-ей, в него введены четьфе .триггера, инвертор и П времязадающих логических элементов И, входами подключенных к первому выходу времязадающего каскада, выходы времязадающих логических элементов И соединены с 1 -ми входами логического элемента ИЖ, выход которого подключен к 3 , С и К - входам первого триггера, выход первого триггера подключен к входу времязадающег каскада, R-входы первого и второго триггеров соединены между собой, а S-вход первого триггера подключен к выходу логического элемента И, один из входов которого подключен к выходу третьего триггера и ко U-входу второго триггера, а второй вход логического элемента И соединен с клем мой тактовых импульсов, с С-входами второго, третьего и четвертого триггеров и с К-входами третьего и четвертого триггеров, у которых через инвертор соединены R-входы, выход четвертого триггера подключен к К-вх ду второго триггера, прямой выход

{1-n)it 5 которого подключен к (1+1)-ым входам второго, (1-3) и (l-n)-ro времязадающих элементов И и к О -входу четвертого триггера, а инверсный выход второго триггера подключен к второму входу выходного логического элемента И 3 -входу третьего триггера и к первым входам 1-2, {l-n)-l и (1-п)2 времязадающих логических элементов И. Источники информации, принятые во внимание при экспертизе 1 . Авторское свидетельство СССР №457731, кл. Н 03 К 5/20, 1974. 2. Заявка ФРГ № 2358915, кл. Н 03 К 5/13, 1975.

Jfe

J3

n

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов по фронту и спаду | 1977 |

|

SU711671A1 |

| Селектор интервалов между импульсами | 1979 |

|

SU822341A1 |

| Формирователь импульсов | 1978 |

|

SU744943A1 |

| Цифровой фильтр | 1978 |

|

SU748803A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU684735A1 |

| Расширитель импульсов | 1976 |

|

SU603109A1 |

| Формирователь импульсов | 1975 |

|

SU541279A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| Формирователь дискретных сигналов | 1979 |

|

SU809523A1 |

| Устройство для управления двухтактным транзисторным инвертором | 1989 |

|

SU1644335A1 |

ц

Фиг.2

Авторы

Даты

1981-06-23—Публикация

1977-08-01—Подача