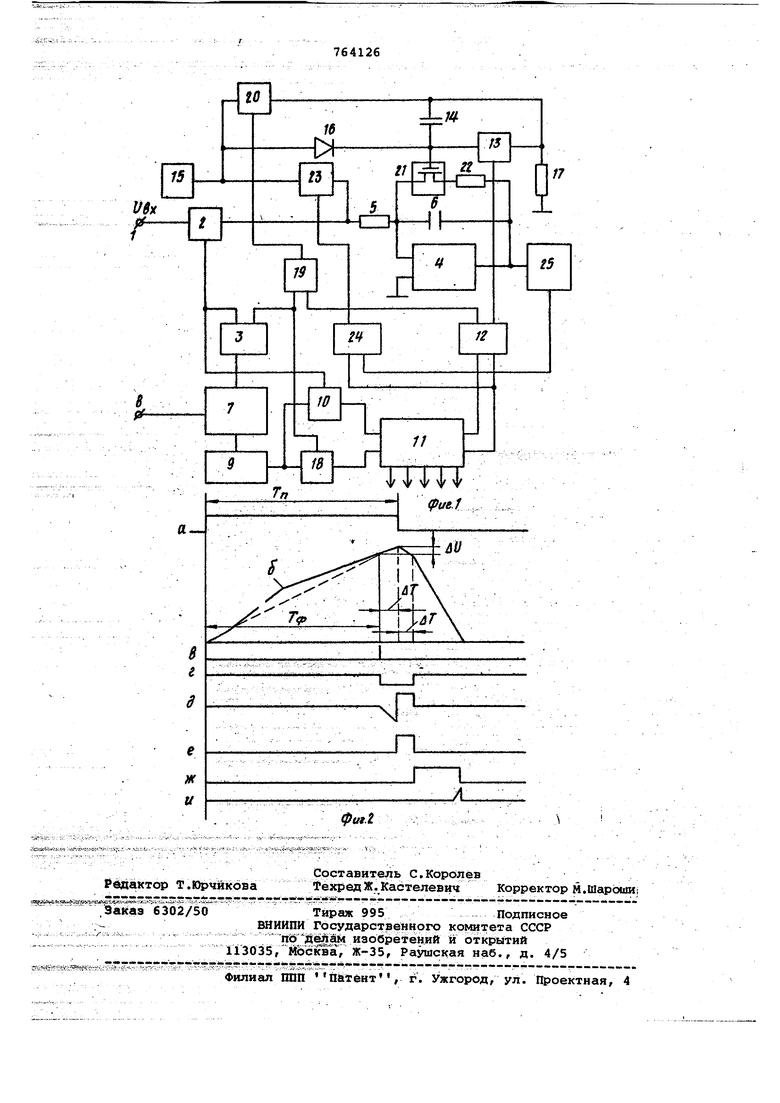

(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КОМПЕНСАЦИОННОГО ИНТЕГРИРОВАНИЯ , t . . Изобретение относится к импульсной технике. Устройство предназначено для аналого-цифрового преобразования электрических сигналов. Известен аналого-цифровой преобраЗователь (АЦП) компенсационного интегрирования, содержащий интегратор на операционном усилителе с ЕСцепью, ключи, нуль-орган, реверсивный счетчик, триггеры интегрирования входного и опорного напряжений, недостатком которого является значител ная неточность преобразования СИ. Известен аналого-цифровой преоб.разователь компенсационного интегрирования, содержащий интегратор, вход ные ключи, источники опорного напряжения и импульсов, реверсивный счетчик, блок управления, триггеры (2. Недостатком такого АЦП является наличие методической погрешности при изменении частоты помехи. Цель изобретения - повышение, точности преобразования АЦП компенсационного интегрирования, в котором период помех не равен фиксированному интервалу времени интегрирования .входного сигнала . Это достигается тем, что в АЦП компенсационного интегрирования, . содёржа18Ий источник опорного напряжения, интегратор, выполненный на операционном усилителе с входнь резистором и конденйатором, цепь аналоговой коррекции, состоящую из первого ключа и резистора, два ключа для подключения входного и опорного напряжений, нуль-орган, триггеры фиксации времени интегрирования входного и опорного напряжений, триггер коррекции, генератор заполняющих импульйов, реверсивный счетчик, первый элемент И и блок управления, причем вход интегратора соединен с выхода ми двух ключей для подключения входного и опорного напряжений, управляющие . входы этих ключей подключены к единичным выходам триггеров фиксаций времени инте1т ирования входного и опорного напряжений соответственно, выход Интегратора соединен с первым выводом первого резистора и с входом нуль-органа, выход которого подключен к нулевому входу триггера фиксации времени интегрирования опорного напряжения, единичный вход которого соединен с единичным входом триггера коррекции, выход генератора эаполняющйх импульсов соединен с первым входом первсэго элемента И, выходом подключенного к суммирующему входу реверсивного счетчика, выход которо,го подключен к нулевому входу триггера коррекции, единичным выходом подключенного.к управляющему входу первого ключа, первый выход блока управления соединен с входом генератора заполняющих импульсов, а второй выход - с единичным входом триггера фиксации времени интегрирования входного сигнала,единичный выход которого соединен с вторым входом первого элемента И, введены элемент с изменяемым сопротивлением, например МОПтранзистор, накапливающий конденсатор коррекции,диод,второй резистор,второй ключ,второй и третьей элементы И. При чем исток МОП-транзистора подклйчен к входу операционного усилителя интегратора, его сток - к второму выводу первого резистора, а затвор - к .катоду диода, к выходу первого ключа и к одной обкладке накапливающего конденсатора коррекции, другая обкладка которого соединена с входом первого ключа, с выходом второго ключа и с первым выводом второго резистора , другой вывод последнего соединен с общей шиной, второй ключ входом подключен к источнику опорного напряжения и к аноду диода, управляющим входом - к выходу третьего элемента И, первый вход которого соединен с нулевым выходом триггера коррекции, второй вход - с нулевым выходом триг гера фиксации времени интегрирования входного напряжения и с первым входо второго элемента И, второй йХОд кото рого соединен с выходой гёиёратора заполняющих импульсов, а выхйД - с вычитающим входом реверсивногосче чика, выход заем которого соединен с единичным входом триггера коррекции, . Структурная схема АЦП и временная диаграрлма его работы приведены на фиг.. 1 и 2.. - . Входной сигнал, подключенньай к клеме 1, с помощью ключа 2, управляёН мого триггером 3 фиксации времени . интегрирования входного напряжения, подается на вход интегратора, выполненного на операционном усилителе 4 с RC-цепью 5, 6. Интегрирование этого сигнала продолжается в течение периода ..Тр , (фиг. 2а) , формируемЬго блоком управления 7 по внешнему сигналу источника помехи, подключенного к входу 8. Так как преобразуемый сигнал содержит -гармоническую-помеху, то напряжение на выходе интегратора изменяется за период интегрирования не по линейному закону (фиг.26 К концу периода Tf, помеха сконпенсиррвана. За это же время от генератора 9 импульсов через элемент И 10 на су1ФШрую1ций вход реверсивного счетчика 11 поступают импульсы. В связи с тем, что Tf, не равно Т (t. выбирается так, чтобы Тф было меньще Т ), то до окончания интегрирования сигнала происходит переполнение счетчика (фиг. 2,в). По этому сигналу триггер коррекции 12 переключается и своим сигналом (фиг. 2г) закрывает ключ 13, разрешая тем самым заряд кЬнденсатора 14 по цепи ,от источника 15 опорного напряжения через диод 16 и резистор 17. При этом подсчет импульсов в счетчике 11 продолжается, С окончанием периода интегрирования элемент И 10 закрывается и открывается элемент И 18. Начинается режим вычитания импульсов от генератора 9 (фиг, 2,е). Одновременно с этим через элемент И 19 открывается ключ смещения 20, подключая источник 15 опорного напряжения к резистору 17, что приводит к автоматическому запиранию диода 16 и открыванию МОП-транзистора 21. Приг чем его сопррти вление зависит от величины накоплен ного на конденсаторе 14 напряжения ( фиг. 2,д). При открывании транзистора 21 конденсатор 6 интегратора начинает разряжаться по цепи, состоящей из МОП-транзистора 21 к резистора 22, Когда накопленный в счетчике 11 после перёполнения код в режиме вычитания станет равным нулю, с выхода .заем счетчика 11 импульс переключает триггер 12 и включает режим интегрирования опорного напряжения через ключ 23, управЯяелшй триггером 24, Режим интегрирования опорного напряжения (фиг, 2,ж) заканчивается в момент срабатывания компаратора 25 (фиг, 2и). Таккак в течение времени, определяемого йиафрагмой ё на фиг. 2,в счетчике 11 происходит вычитание, то результат лреобразования должен считываться с нулевых выходов разрядов этого счет- , чика. Уравнение преобразования в данном j АЦП имеет следующий вид: .(т,.. I I 4-Л.Т I-Kl 1г. где -дт|г tj JbV ( (причем ,- pU-Rg. сопротивление цепи элементов 21 к 22 соответственно откуда и„.( U«v t- Si-r j. ° .f . ГГ ) tl. on on I Преобразование выполняется без погрешности, если второй член выражения (3) равен нулю/Откуда1г -Тф-1-лТ или ( R-. + дк )-с Тф лТ/или если в схеме выполнить условия и лт &RC, TOat 0. Условие, что в АЦП величина сопротивления МОП-транзистора 21 пропорциональна лТ, означает, что окончательный результат преобразования не зависит, от соотношения Тф и Т„. Таким образом в предложенном устрой(стве достигнут положительный эффект, состоящий в повышении точности преобразования. Формула изобретения Аналого-цифровой преобразователь компенсационного интегрирования, содержащий источник опорного напряжени интегратор, выполненный на операционном усилителе с входным резистором и конденсатором, цепь аналоговой коррекции, состоящую из первого ключа и первого резистора,два ключа для подключения входного и опорного напряжений, нуль-орган, триггеры фиксации времени интегрирования входного .и опорного напряжений, триггер коррекции, генератор заполняющих импуль сов, реверсивный счетчик, первый эле мент И и блок управления, причем вхо интегратора соединен с выходами ключей для подключения входного и опорного напряжений, управлякяцие входы этих ключей подключены к единичным выходам триггеров фиксаций времени интегрирования входного и опоррого напряжений соответственно, выход интегратора соединен с первым выводом первого резистора и с входом нульоргана, выход которого подключен к нулевому входу триггера фиксации вре мени интегрирования опорного напряже ния, единичный вход которого соедине с единичным входом триггера коррекдин, выход генератора заполняющих ИМпульсов соединен с первым входом пер вого элемента И , выходом подключенного к суммирующему входу реверсив:ного счетчика, выход которого, подключен к нулевому входу триггера коррекции, единичным выходом подключенного к управляющему входу ijepBoro ключа, первый выход блока упра;вления соединен с входом генератора заполняющих импульсов , а второй выход - с единичным входом триггера фиксации времени интегрирования входного сигнала, единичный выход которого соединен с вторым входом первого элемента И, отличающийся тем, что, с .целью повышения, точности преобразования, он дополнительно содержитэле ент с изменяемым сопротивлением, например МОП-транзистор, накапливающий конденсатор коррекции, диод,второй резистор, второй ключ, второй и третий элементы И, причем исток МОПтранзистора подключен к входу операционного усилителя интегратора, его сток - к второму выводу . первого резистора, а затвор - к катоду диода, к выходу первого ключа и к одной обкладке накапливающего конденсатора коррекции, другая обклсщка которого соединена с входом первого ключа, с 1выходом второго ключа и с первым выводои второго резистора, другой вывод последнего соединен с общей шиной , второй ключ входом подключен к источнику опорного напряжения и к аноду диода, управляющим входом - к выходу третьего элемента И, первый вход которого соединен с нулевым выходом триггера коррекции; второй вход с нулевым выходом триггера фиксации времени интегрирования входного напряжения и с первым входом второго элемента И, второй вход которого соединен с выходом генератора заполняющих импульсов, а выход - с вычитающим входом реверсивного счетчика, выход заем которого соединен с единичным входом триггера коррекции. Источники информации, принятые во внимание при экспертизе 1.Гитис Э.И. Преобразователи информации, Энергия, 1970, с. 335. 2.Патент США № 3729733, кл. 340347, 24.04.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Интегрирующий многошаговый аналогоцифровой преобразователь | 1971 |

|

SU472453A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1298671A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-цифровое интегрирующее устройство | 1980 |

|

SU868784A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| Цифровой измеритель энергии ударного импульса | 1982 |

|

SU1016705A1 |

Авторы

Даты

1980-09-15—Публикация

1974-06-19—Подача