. , .,.; , , I . ; л

Изобретение относится к области вычислительной техники, в частности к стрзтстурам цифровых арифметических устройств, контроль которых организован по четности, а используемые сумматоры формируют разрядные переносы параллельным образом.

Известны сумматоры, содержащие в каждом разряде схему образования параллельного переноса из разряда, включающую схемы формирования функций генерации и транзита переноса, выхоДь которых соединены со входами собственно схемы образования параллельного переноса из разряда,. на дополнительные входы которой поступают сигналы функций генерации и транзита переноса из предыдущих разрядов, а выход является выходом схемы образования параллельного переноса из разряда, схему суммы, входы которой соединены с выходами схемы образовайия-параллельного переноса из предыдущего разряда и схем формирования функций генерации и транзита переноса этого же разряда 1.

Разрядные суммы при этом формируются в соответствии с выражением

(1)

Sn GnVTnVCn,

где On anbn,

Тр, Эп+Ьп - соответственно функвди геHepaiutH и транзита переноса п-го разряда;

Cn-i - перенос из предыдущего

(n-l)-ro разряда; Зп, Ьп - разряд1П)1е сжигаемые. Недостатком известных сумматоров является невозможность обнаружения ощибок, вызываемых неисправностью собственно схемы образования параллельных переносов из разрядов (схемы образования параллельных переносов за исключением схеМ . формирования функций Gn и Тп),. при организа.ции их контроля по чет:ности.

Из известных сумматоров с параллельными переносами и контролем по четности наиболее близким по технической сущности к изобретению является параллельный сумматор с контролем по четности, содержащий в каждом разряде блок формирования суммы с функциональЬой зависимостью от переноса, причем первый, второй и третий выходы блока формирования Параллельного переноса четных разрядов сумматора соедшены соответственно с первым, вторым и третьим входом блока формирования суммы с функциональной зависимостью от переноса 2. Здесь при формировании разрядных сумм предполагается использование выражения Sn anbnCnCn-i + GnCnCn-i + + Tn-Cn-Cn i +tn-Cn-Cn-i(2) что позволяет: -во- первых, применять в схемах суммы и переносов общие схемы формирования функшш генерации и транзита переноса; -во вторых, обеспечить высокое быстродействие (разрядная сумма по Ср переносу формируется в три уровня). К осно&ным недостаткам следует отнести: -относительно низкий уровень контроля собственно схем образования параллельных перёносов из разрядов (в 50% случаев эти схемы не контролируются по четности}. Действительно, так как булевы разности от Sn и Sn+i сумм соответственно равны 1 и Мп4.1 то ошибка в образовании переноса не всегда будет обнаружена контролем по четности, вопреки распространенному мнению 2, а лишь в случае равенства нулю полусуммы следующего разряд. -не позволяет организовать контроль схем, формующих инверсии Сп переносов. -использование в схеме суммы сумматора схем, формирующих разрядные суммы в соответствии с выражением (2), требует увеличени ее оборудования примерно на 40% в сравнеНИИ с исходным вариантом (то есть, когда разрядные суммы формируются в соответствии с соотношением (1). Целью изобретения является повь1шенйе конт ролирующей способности как за счет увеличения процента обнаруживаемых ошибок, так и за Счет сокращения избыточного оборудования. Поставленная цель достигается тем, что в каждый нечетный разряд сумматора введены блок формирования поразрядной суммы, блок формирования дублирующего переноса и блок сравнения, причем первый вход блока формирования поразрядной суммы соединён с первьш входом блока формирования дублирующего переноса и является входом устройства, первый р второй выходы блока формирования пэраллельного переноса нечетных разрядов соединены соответственно со вторьгм и третьим входом блока формирования поразрядной суммы соответствующего разряда, третий выходблока форм рования параллельного переноса каждого нечетного разряда соединен с первым входом соогветствующего блока сравнения и с четвертым входом

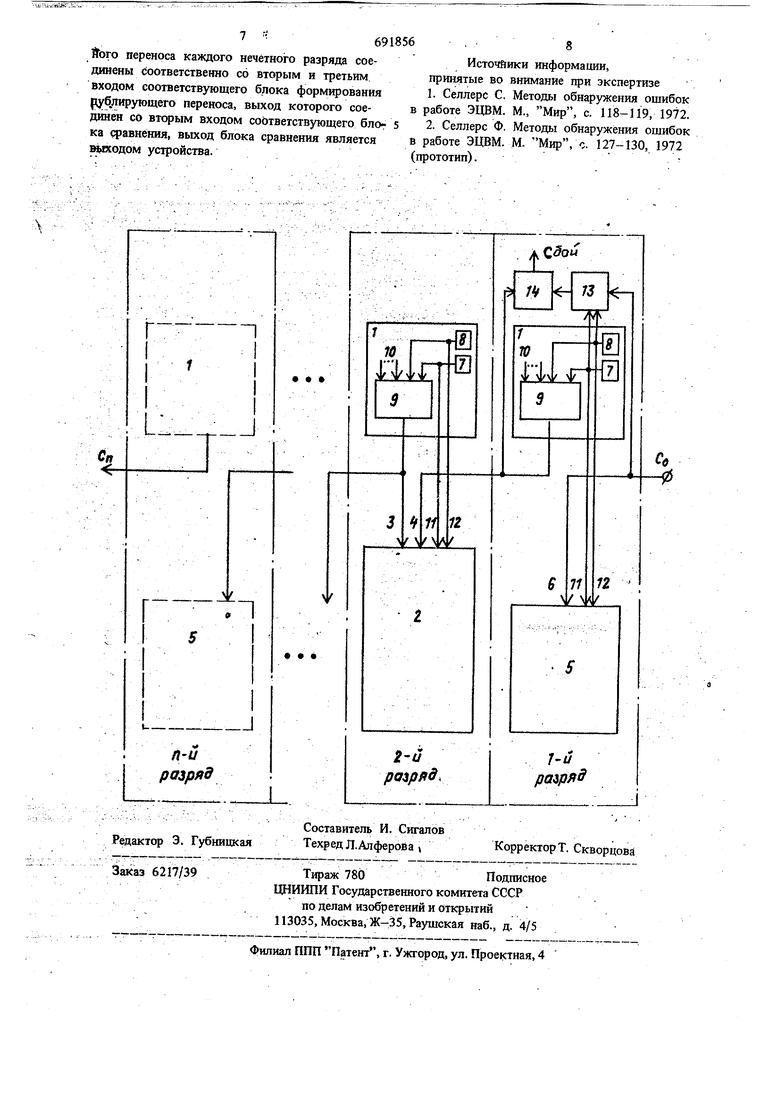

691856 блока формирования суммь с функциональной зависимостью от переноса последующего четного разряда, третий выход каждого четного блока формирования параллельного переноса соединен соответственно с первым входом блока формирования поразрядной суммы по- . следующего нечетного разрада, первый и второй выходы блока формирования параллельного переноса каждого нечетного разряда соединены соответственно со вторым и третьим входом соответствующего блока формирования дублирующего переноса, выход которого соединен со вторым входом соответствующего блока сравнения, выход блока сравнения является выходом устройства.. Таким образом, сумматор построен с рещетчатой функциональной зависимостью суммы От переноса, то есть, если Sn сумма зависит от переносов Сп и соответственно из собственного и предыдущего разрядов и формируется в соответствии с выражением (2), что Snfi и Sn-i суммы зависят соответственно от ,Сп и Сп-2 переносов из предыдущего разряда и формируются согласно соотношеншо (1). В зтом случае ощибка в образовании Сп переноса, вызванная любой неисправностью схемы образования параллельного переноса, будет обнаружена контролем по четности, так как булевы разности dSn/dCn и dSn.|.i/dCn всегда равны единице. Ошибка же в формировании переноса будет всегда обнаружена контролем по четности, если она вызвана неисправностью только схемы формирования Gn+i или ТптЦ функции (так как разрядная сумма Оп4-1 VTn4.i V-Cn не обнаружена контролем ,как и в-известном сумматоре в 50% случаев (в предлагаемом сумматоре, когда полусумма Нп.2 следующего разряда равна нулю), если она вызвана неисправностью собственно схемы образования параллельного переноса. , Введение в сумматор п/2- (п-разрядность сумматора) схем формирования дублирующих переносов с их последующим сравнением с дублируемыми перенорами позволяет организовать полный контроль сзпиматора. На чертеже приведена структурная Ьхема параллельного сумматора с контролем по четности. Сумматор содержит в каждом разряде блок 1 формирования параллельного переноса, блок 2 формирования суммы с функциональной зависимостью от переноса в разрядах с четными номерами, входы 3 и 4 которого соединены с выходами блока 1 формирования параллельных переносов из собственного и предыдущего разрядов, блок 5 формирования

поразрядной суммь в разрядах с нечетными номерами, вход 6 которого соединен с выходом блбка 1 формирования параллельного переноса из предыдущего разрйда (для первого разряда на этот вход поступает входной перенос сумматора CQ).

Блок 1 формирования параллельного пере(носа из разряда в каждом разряде содержит элемент И 7 и элемент ИЛИ 8, которые выполняют функцию генерации и транзита переноса, соответственно выходы которых соединены со входами узла 9 формирования паралельного переноса из разряда, на дополнительные входы 10 которого поступают сигналы функций генерации и транзита переноса из предыдущих разрядов, а выход является выходом блока 1 формирования параллельного переноса из разряда.

Дополнительные входы 11 и 12 блоков 2(5) в каждом разряде соединены с выходами элементов И 7 и ИЛИ 8 формирования функций генерации и транзита переноса этого же разряда.

Сумматор содержит в разрядах с нечетными номерами блок 13 формирования дублирующего переноса, входы которого соедшены выходами блока 1 формирования параллельного переноса из предыдущего разряда элемента И 7 и элемента ИЛИ 8 формирования функций генерации и транзита переноса этого же. разряда, а выход подключен к первому входу блока 14 сравнения, второй вход которого соединен с выходом блока 1 формирования параллельного переноса из этого же разряда.

Сумматор работает следующим образом. Пусть ощибка в образовании параллельного переноса, например, из 1-го разряда Cj, вызвна неисправностью элемента И 7 формирования фзлнкции генерации или элемента ИЛИ 8 транзита переноса. Тогда эта ощибка обязательно вызовет ощибки в формировании Si и Sj сумм, что будет обнаружено контролем по четности, так как общее число ощибок в разрядах суммы и переноса нечетно. Распространение же ошибки переноса Ci вдоль разрядов сумматора не нарушает условие нечетности обц)1его числа ощибок в разрядах суммы и переноси. Если же ощибка в образовании параллельного переноса вызвана неисправностью узла 9 формирования параллельного переноса из разряда, то она будет обнаружена контролем по четности, если номер разряда сумма- . тора, в котором произощла ощибка, четный, например 2-й, так как она при этом вызовет ощибки в разрядньгх суммах Sj и 83, не всегда будет обнаружена контролем по четности, если номер разряда, в котором произощла

ошибка, нечетный, например 1-й, так как она может вызвать ошибку в разрядной сумме S (случай необнаружения ощибки), а может и не вызвать ощибку в -разряде суммы (случай обнаружения ошибки).

В нечетных разрядах ошибка в работе узfia 9 будет обнаружена в результате сравнения выхода сигналов на выходе блока 1 с выходом блока 13 формирования дублирующего

0 переноса блоком 14 сравнения.

Таким образом, введение в параллельный сумматор с контролем по четности в разрядах с нечетными номерами п/2 блоков формирования дублирующих переносов п/2 блоков срав5нения и п/2 блоков формирования поразрядной суммы позволит обнаруживать контролем по четности все сочетания ощибок, вызываемые одиночной неисправностью сумматора.

..., Формула изобретения

0

Параллельный-сумматор с контролем по четности, содержащий в каждом разряде блок формирования параллельного переноса, каждый четный разряд содержит блок формирования

5 суммы с функциональной зависимостью от переноса, причем первый, второй и третий выходы блока формирования параллельного переноса четных разрядов сумматора соединены соответственно с первым, вторым и третьим вхо0дом блока формирования суммы с функциональной зависимостью от переноса, отличающийся тем, что, с целью повышения контролирующей способности сумматора, в каждый нечетный разряд сумматора введены

5 блок формирования поразрядной суммы, блок формирования дублирующего переноса и блок сравнения, причем первый вход блока формирования поразрядАой. суммы соединен с первым входом блока формирования дублирующего

0 переноса, первый вход блока формирования поразрядной суммы первого разряда является входом устройства, первый и второй выходы блока формирования нараллельпого переноса нечетных разрядов соединены соответственно

5 со вторым и третьим входом блока -формирования поразрядной суммы соответствзпощего разряда, третий выход блока формирования параллельного переноса каждого нечетного разряда соединен с первым входом соответствую0щего блока сравнения и с четвертым входом блока формирования суммы с функциональной зависимостью от переноса последующего четного разряда, третий выход каждого четного блока формирования параллельного пере5носа. соединен соответственно с первым входом блока формирования поразрядной суммы последующе1о нечетного разряда, первый и второй выходы блока формирования параллельftbro переноса каждого нечётного разряда соединены соответственно со вторым и третьим входом соответствующего блока формирования рублирующего переноса, выход которого соединен со вторым входом соответствующего блог 5 ка (равнения, выход блока сравнения является вводом устройства.

Источйики информации, принятые во внимание при экспертизе

1.Селлерс С. Методы обнаружения ощибок в работе ЭЦВМ. М., Мир, с. 118-119, 1972.

2.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. М- Мир, с. 127-130, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Контролируемый сумматор с групповым переносом | 1977 |

|

SU684545A1 |

| Сумматор с функциональной зависимостью сумм от переносов и с контролем по четности | 1977 |

|

SU767763A1 |

| Параллельный сумматор с контролем по четности | 1977 |

|

SU739535A1 |

| Контролируемый параллельный сумматор | 1977 |

|

SU703817A1 |

| Параллельный сумматор | 1976 |

|

SU643871A1 |

| Сумматор с параллельным переносом | 1977 |

|

SU744557A1 |

| Параллельный сумматор с контролем по четности | 1982 |

|

SU1121674A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Устройство для сложения чисел с контролем | 1978 |

|

SU885995A1 |

Авторы

Даты

1979-10-15—Публикация

1977-01-18—Подача