предсказания четности результата соответственно объединены и подключены к соответствующим выходам блока формирования инверсных функций генерации и передачи переноса,первые входы функций передачи переноса и функций инверсной передачи переноса блока младших разрядных сумматоров подключены к соответствующим выходам блока формирования функций генерации и передачи переноса и блока формирования инверсных функций генерации и передачи переноса, первый и третий входы функции передачи переноса и инверсных функций передачи переноса блока предсказания четности результата объединены соответственно с вторым и третьим входами функций передачи переноса и инверсных функций передачи Переноса блока младших разрядных сумматоров и подключены соответственно к второму и третьему выходам функций передачи переноса блока формирования функций генерации и передачи переноса и блока формирования инверсных функций генерации и пе174 редачи переноса, четверт;ые выходы функций генерации переноса, функций передачи переноса, инверсных функций генерации переноса и инверсных функций передачи переноса подключены соответственно к третьему, четвертому, пятому и шестому входам блока формирования старшего разряда суммы, выход которого подключен к бторому входу первого блока сравнения, третий, четвертый и пятый входы которого соответственно объединены с соответствующими входами второго блока сравнения и подключены соответственно к первому, второму и третьему выходам блока младших разрядных сумматоров, вход входного переноса которого объединен с входом входного переноса блока формирования четности результата и подключен к входу входного переноса сумматора, входы четности входных слагаемых которого подключены соответственно к входам четности входных слагаемых блока предсказания четности результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор с контролем по четности | 1983 |

|

SU1124283A1 |

| Параллельный сумматор с контролем по четности | 1984 |

|

SU1187168A1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| Многоразрядное устройство для сложения с контролем по четности | 1981 |

|

SU1035598A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| Сумматор с функциональной зависимостью сумм от переносов и с контролем по четности | 1977 |

|

SU767763A1 |

| Контролируемый параллельный сумматор | 1977 |

|

SU703817A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Параллельный сумматор с контролем по четности | 1977 |

|

SU739535A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

ПАРАЛЛЕЛЬНЫЙ СУММАТОР С КОНТРОЛЕМ ПО ЧЕТНОСТИ, содержащий блок формирования функций генерации . и передачи переноса, входы которого являются входами слагаемых сумматора, блок формирования параллельных переносов, блок младших разрядных сумматоров, выходы которого являются выходами суммы младших разрядов суммато- . ра, блок формирования старшего разряда суммы, выход которого является выходом суммы старшего разряда сумматора, блок формирования четности результата, блок предсказания четности результата, первый и второй блоки сравнения, выходы которых являются соответственно выходами Сбой 1 и Сбой 2 сумматора, причем первый вход первого блока сравнения подключен к выходу блока предсказания четности результата, первый вход второго блока сравнения подключен к выходу блока формирования четности результата, вторые входы первого и второго блоков сра-внения объединены между собой, первые и вторые входы блока младших разрядных сумматоров и блока формирования четности результата соответственно объединены и подключены соответственно, к первому и второму выходам блока формирования параллельных переносов, третий вход блока формирования четности результата и первый вход блока формирования старшего разряда суммы объединены и подключены к третьему выходу блока формирования параллельных переносов, четвертый выход которого подключен к второму входу блока формирования старшего разряда суммы, вход входного переноса блока формирования четности результата объединен с входом входного переноса блока формирования параллельных переносов и входом входного переноса блока предсказания четности результата и является входом входного переноса сумматора, а вхо(Л ды четности слагаемых блока формирования четности результата являются входами четности слагаемых сумматора, отличающий с я тем, что, с целью повьш1ения быстродействия, сумматор содержит блок формирования инверсных функций генерации и передачи переноса, входы которого подключены соответственно к входам блока формирования функций генерации и передачи переноса, выходы которого подключены к соответствующим входам блока формирования параллельных переносов, первьш, второй и третий входы функций генерации переноса блока млапших раз рядных сумматсэров и блока предсказания четности результата соответственно объединены и подключены к соответствующим выходам блока формирования функций генерации и передачи переноса, первый, второй и третий входы инверсных функций генерации переноса блока младших разрядных сумматоров и блока

I

Изобретение относится к вычисли. тельной технике и может быть использовано дпя построения арифметических устройств, в которых контроль организован по четности, а используе1яые сумматоры формируют разрядные переносы параллельным способом.

Известен параллельный сумматор с функциональной зависимостью суммы от переносов, содержащий в каждом разряде .блок формирования параллельного переноса, блок формирования разрядно суммы с функциональной зависимостью от переносов, блок формирования дублирующего переноса и блок сравнения, первый вход которого соединен с выходом блока формирования дублирующег переноса, вход которого соединен с выходом блока формирования параллельного переноса предьщущего разряда и с вторым входом блока формирования разрядной суммы с функциональной зависимостью от переносов, первый вход которого соединен с выходом бло.ка формирования параллельного переноса данного разряда и с вторым входом блока сравнения, выход которого соединен с внешнего приемника сигнала Ошибка ij .

Недостатком такого сумматора является большой временный цикл работы вследствие необходимости формирования дублирующих переносов сквозным методом.

Наиболее близким к изобретению является параллельный сумматор с контролем по четности, содержащий первый блок сравнения, блок предсказания четности, блок формирования четности суммы, а каждый разряд сумматора, кроме старшего, содержит блок формирования параллельного переноса, элемент И, элемент ИЛИ, блок формирования поразрядной суммы, старший разряд сумматора содержит блок формиро- вания параллельного переноса, элемент И и элемент ИЛИ, причем первые выходы блоков формирования поразрядной

суммы всех разрядов, кроме старшего, соединены соответственно с первым, вторым и третьим входами блока предсказания четности, четвертый и пятый входы блока предсказания четности являются соответственно первым и вторым входами сумматора, вторые выходы блоков формирования поразрядной суммы всех разрядов, кроме старшего, соединены соответственно с первьм, вторым и третьим входами блока формирования четности суммы, выход которого соединён с первым входом первого блока сравнения, первый выход блока предсказания четности соединен с вторым входом первого блока сравнения, выход которого является первым выходом сумматора, выходы элементов И и ИЛИ каждого разряда соединены соответственно с первым и вторым входами блока формирования параллельного переноса соответствующего разряда, выход блока формирования параллельного переноса старшего разряда является вторым выходом сумматора, выходы элементов И и ИЛИ каждого разряда сумматора, кроме старшего, соединены соответственно с первым и вторым входами блока формирования поразрядной суммы соответствующего разряда, выход блока формирования параллельного переноса каждого разряда, кроме двух старших, соединен с третьим входом блока формирования поразрядной суммы последующего разряда, третий вход блока формирования поразрядной суммы первого разряда соединен с третьим входом сумматора и с шестым входом блока предсказания четности . Кроме того,

в сумматор введень второй блок сравнения, блок формирования четности результата, -старший разряд сумматора содержит блок формирования поразрядной суммы с функциональной зависимостью от переносов, причем выход блока формирования параллельного переноса старшего разряда соединен с первым входом блока формирования поразрядной суммы с функциональной зависимостью от переносов, выход которого соединен с четвертым входом блока формирования четности суммы, выход элемента ИЛИ старшего разряща соединен с вторым входом блока формирования поразрядной суммы с функционапьной зависимостью от переносов, третий вход которого соединен с выходом блока формирования параллельного

переноса предыдущего разряда, выход блока формирования параллельного переноса всех разрядов, кроме старшего соединен соответственно с первым, вторым и третьим входами блока формирования четности результата, четвертый и пятый входы которого соединен соответственно с третьим входом сумматора и с вторьм выходом блока предсказания четности, выход блока формирования четности результата соединен с первым входом второго блока сравнения, выход которого является третьим выходом сумматора, выход блока формирования четности суммы соединен с вторым входом второго блока сравнения 2 .

Недостатком данного сумматора является низкое быстродействие, связанное с необходимостью формирования поразрядных полусумм в блоке предсказания четности.

Цель изобретения - повышение быстродействия .

Поставленная цель достигается тем что параллельный сумматор с контролем по четности, содержащий блок формировг ния функций генерации и передачи переноса, входы которого являются входами слагаемых сумматора, блок формирования параллельных переносов, блок младших разрядных сумматоров, выходы которого являются выходами суммы младших разрядов сумматора, блок (Ьормиоования старщего разряда суммы, выход которого является выходом суммы старшего разряда сумматора, блок формирования четности результата, блок предсказания четности результата, первый и второй блоки сравнения, выходы которых являются соответственно выходами Сбой 1 и Сбой 2 сумматора, причем первый вход первого блока сравнения подключен к выходу блока предсказания четности результата, первый вход второго блока сравнения подключен к выходу блока формирования четности результата, вторые входы первого и второго блоков сравнения объединены между собой, первые и вторые входы блока младших разрядных сумматоров и блока формирования четности результата соответственно объединены и подключены соответственно к первому и второму выходам блока формирования параллельных переносов, третий вход блока формирования четности результата и первый вход блока формирования старшего разряда суммы объединены и подключены к третьему выходу блока формирования параллельных переносов, четвертый выход которого подключен к второму входу блока формирования старшего разряда суммы, вход входного переноса блока формирования четности результата объединен с входом входного переноса блока формирования параллельных переносов и входом входного переноса блока предсказания четности результата и является входом входного переноса сумматора, а входы четности слагаемых блока формирования четности результата являются входами четности слагаемых сумматора, включает в себя блок формирования инверсных функций генерации и передачи переноса, входы которого подключены соответственно к входам блока формирования функций генерации и передачи переноса, выходы которого подключены к соответствующим входам блока формирования параллельных переносов, первый, второй и третий входы функций генерации переноса блока мпадших разрядных сумматоров и блока предсказания четности результата соответственно объединены и подключены к соответствующим выходам блока формирования функций генерации и передачи переноса, первый, второй и третий входы инверсных функций генерации переноса блока мпадших разрядных сумматоров и блока предсказания четности результата соответственно объединены и подключены к соответствующим выходам блока формирования инверсных функций генерации и передачи переноса, первые входы функций передачи переноса и функций инверсной передачи переноса блока младших разрядных сумматоров подключены к соответствующим выходам блока формирования функций генерации и передачи переноса и блока формирования инверсных функцийгенерации и передачи переноса, первый и третий входы функций передачи переноса и инверсных функций передачи переноса блока предсказания четности результата объединены соответственно с вторым и третьим входами функций передачи переноса и инверсных функций передачи переноса блока младших разрядных сумматоров и подключены соответственно к второму и третьему выходам функхщй

передачи переноса блока.формирования функций генерации и передачи переноса и блока формирования инверсных функций генерации и передачи переноса, четвертые выходы функций генерации переноса,функций передачи переноса, инверсных функций генерации переноса и инверсных функций передачи переноса подключены соответственно к третьему, четвертому, пятому и шестому входам блока формирования старшего, разряда суммы, выход которого подключен к второму входу первого блока сравнения, третий, четверты и пятый входы которого соответственно объединены с соответствующими входами второго блока сравнения и подключены соответственно к первому, второму и третьему выходам блока младших разрядньк сумматоров, вход входного переноса которого объединен с входом входного переноса блока формирования четности результата и подключен к входу входного переноса сумматора, входы четности входных слагаемых которого подключены соответственно к входам четности входных слагаемых блока предсказания четности результата.

Все блоки сумматора рассматриваются на. примере четьфехразрядного сумматора.

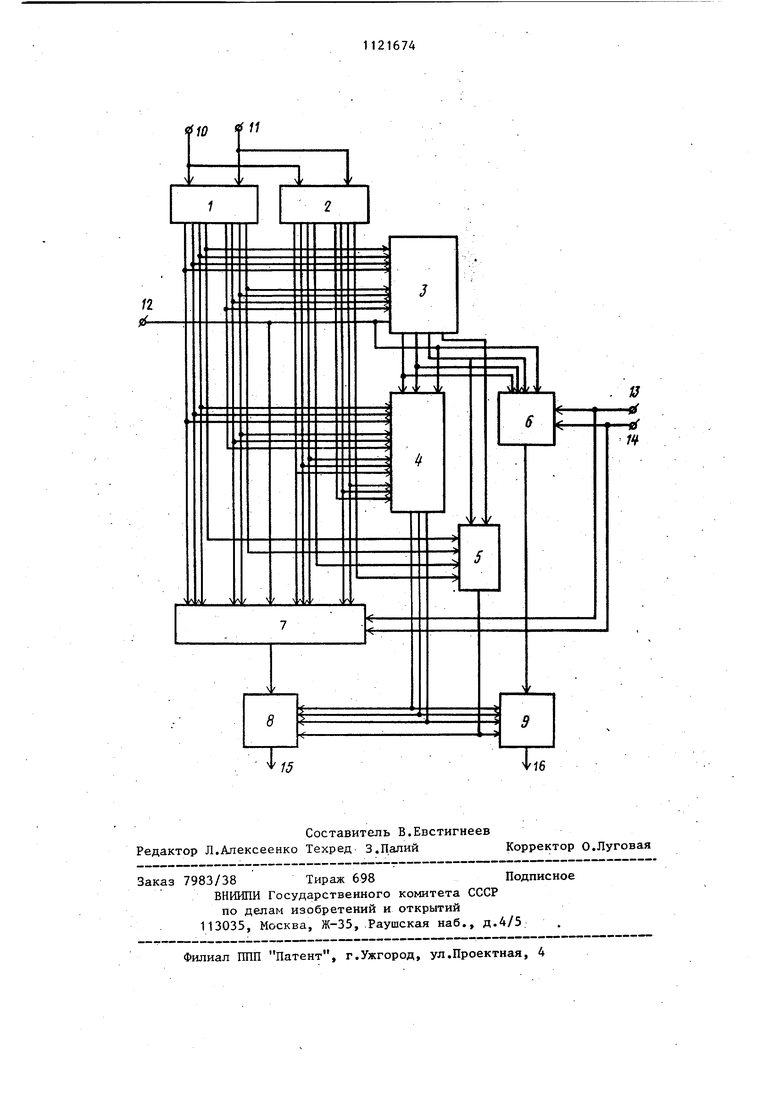

На чертеже представлена структурная схема предлагаемого параллельного сумматора с контролем по четности.

Сумматор содержит блок 1 формирования функций генерации и передачи переноса, блок 2 формирования инверсных функций генерации и передачи переноса, блок 3 формирования параллельных переносов, блок 4 младших разрядных сумматоров, блок 5 формирования старшего разряда суммы, блок 6 формирования четности результата, блок 7 предсказания четности результата, первый 8 и второй 9 блоки сравнения, вход первого 10 и второго 11 слагаемых, вход 12 входного переноса, входы 13 и 14 четности первого и второго слагаемых, выходы 15 и 16 Сбой 1 и Сбой 2 сумматора.

Блок 1 формирования функций генерации и передачи переноса содержит четыре элемента И, выходы которых обозначены соответственно Go,G,G2,G и четыре элемента ИЛИ, выходы которых обозначены соответственно Т (i причем G- Aj8B , То,Тз 2,13, при 0,1,2,3). Блок 2 формирования инверсных функций генерации и передачи переноса содержит четыре элемента И-НЕ, выходы которых обозначены соответственно ,0 ,6 , и четьфе элемента ИЛИ-НЕ, выходы которых обозначены соответственно Т ДуД, причем , Т,,-. Блок 3 формирования параллельных переносов предназначен для формирования параллельных переносов сумматора в соответствии с выражением Co G /V8Cg, ,/T,8Go/T, C2 G2/T28G /T28T,8G3/T28T,,, C,G,,,/T,8T28G /T,8T..8T, . /Tj8T28T,8To8Cgx где С, - перенос,, входящий в парал лельный сумматор (12); С,,С ,СпИ С, - переносы соответ ственно из первого, второго, третьего и четвертого разрядов параллельного сум матора. Блок 4 младших разрядных сумматоров предназначен для формирования п разрядных сумм параллельного сумматора в соответствии с выражением .®T.ffiC; 1 где S. значение суммы i-ro-разряда;значение переноса из (i-l)-ro разряда, номер разряда (0,1,2), ® - сложение по модулю два. Блок 5 формирования старшего раз ряда суммы содержит два элемента НЕ четьфе элемента И и один элемент ИЛИ выход которого обозначен S; и предназначен для формирования суммы в старшем разряде параллельного сумма тора в соответствии с выражением: Sj A B G28Cj/Gj8C28G3/T 8C28C /Tj8C28 где Сл,С2 - инверсные значения пере носов соответственно из третьего и четвертого разрядов параллельного сумматора. Блок 6 формирования четности результата представляет собой шестивходовби сумматор по модулю два и 48, предназначен для формирования четности результата в соответствии с выражением ,®С,®Рд0Р,, где Р и Р0 - значения четности соответственно первого и второго слагаемых (13, 14); четность результата. Блок 7 предсказания четности результата предназначен для ускоренного формирования четности суммы в соответствии с выражением Рд Рд®Рр0Р 0К, где Р. - предварительно формируемая четность суммы Рд и Pg - четность первого и второго слагаемых; Р - предсказываемая четность переносов сумматора при Со 0; К - значение коррекции четности переносов cy Iмaтopa по входному переносу Cg,( ; сложение по модулю два. . Предсказываемая четность переносов сумматора Р формируется в соответствии с вьфажением л,/T,8GQ)0(G /T28G /T28T 8Go)Go8 ()8(G /T 8G /Tt8T 8Ge)/ /(Gi/T,8Go)B(Gj./T,L8G4/Ti.8Ty8Ge) / /G,8 ()8(Gi/T 8G /Ti8T 8G j/ /()8(Gi/Ti8G /T4.8T48G) G2.8Gy8Go8Ti/Gi8G48G«8Ti/Gi8G 8G,/ /Gi.8Go8T /Gi8G48Ge/G,8Ge8Tt/G 8Tx8T. Значение коррекции четности переносов сумматора по входному переносу Cjx определяется согласно выражению ,,8(,8И2, де Н - инверсное значение полусуммы первого разряда, равное ToSGo; Н - значение полусуммы второго разряда, равное Н. - инверсное значение полусуммы третьего разряда, равное T28G2. Подставляя значения полусумм, выаженные через функции генерации пееноса и передачи переноса, и используя правила Де Моргана, получим (Tft8Go/T,8G,8Tj8G2)Ti,8CB;, / /GO SCjjx /Tj8T , 8Т;8Св . Первый блок 8 сравнения представляет собой сумматор по модулю два и предназначен для сравнения четности суммы и предварительно формируемой четности суммь и выработки сигнала Сбой в соответствии с выражением (i )S2®Sj®Pg где сигнал Сбой 1. Второй блок 9 сравнения представляет собой сумматор по модулю два и предназначен дпя сравнения четности суммы и формируемой четности результата и выработки сигнала Сбой в соответствии с выражением Фч. где 0 - сигнал Сбой 2, Параллельный сумматор с контролем по четности работает следующим образом. Предположим, что произошла ошибка в блоке 3 Эта ошибка вызывает ошибку в блокгх 4 и 5, что приводит к нечетному числу ошибок в разрядах суммы и переноса. Следовательно, эта ошибка обнаруживается контролем по четности в блоке 8 сравнения путем сравнения четности суммы И предварительно формируемой четности суммы. Предположим, что возникла одиночная ошибка в 1-м разряде блока 1 формирования функций генерации и передачи переноса или блока 2 формирования инверсных функций генерации и передачи переноса. Эта ошибка вызывает ошибку либо только на выходе блока 4 в i-M разряде, либо ошибку на выходе блока 3 из 1-го разряда и ошибку на выходе блока 4 в данном и последующем разрядах сумматора. Распространение ошибки вдоль разрядов параллельного сумматора приводит к нечетному числу ошибок в разрядах суммы и переноса, что обнаруживается в блоке 9 сравнения. Ошибка в формировании переноса из старшего разряда параллельного сумматора также обнаруживается контролем по четности в блоке 9 сравне ния, так как зта ошибка вызывает ошибку в формировании суммы старшего разряда параллельного сумматора. Таким образом, введение в состав сумматора блока формирования инверсных функций генерации и передачи переноса и соответствующих связей позволяет за счет более, быстрого формирования четности результата повысить быстродействие в среднем в 1,5 раза.

f2 ff1.

. 13

-«r

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Параллельный сумматор | 1976 |

|

SU643871A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Установка для сборки крупногабаритных резинотехнических изделий | 1978 |

|

SU739835A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-30—Публикация

1982-02-22—Подача