00 05 00

эо

Изобретение относится к вычислительной технике и может быть применено при разработке быстродействующих арифметических устройств, контроль которых организован по четности.

Цель изобретения - повышение достоверности формируемых в устройстве результатов путем обнаружения всех ошибок, вызываемых его одиночной неисправностью.

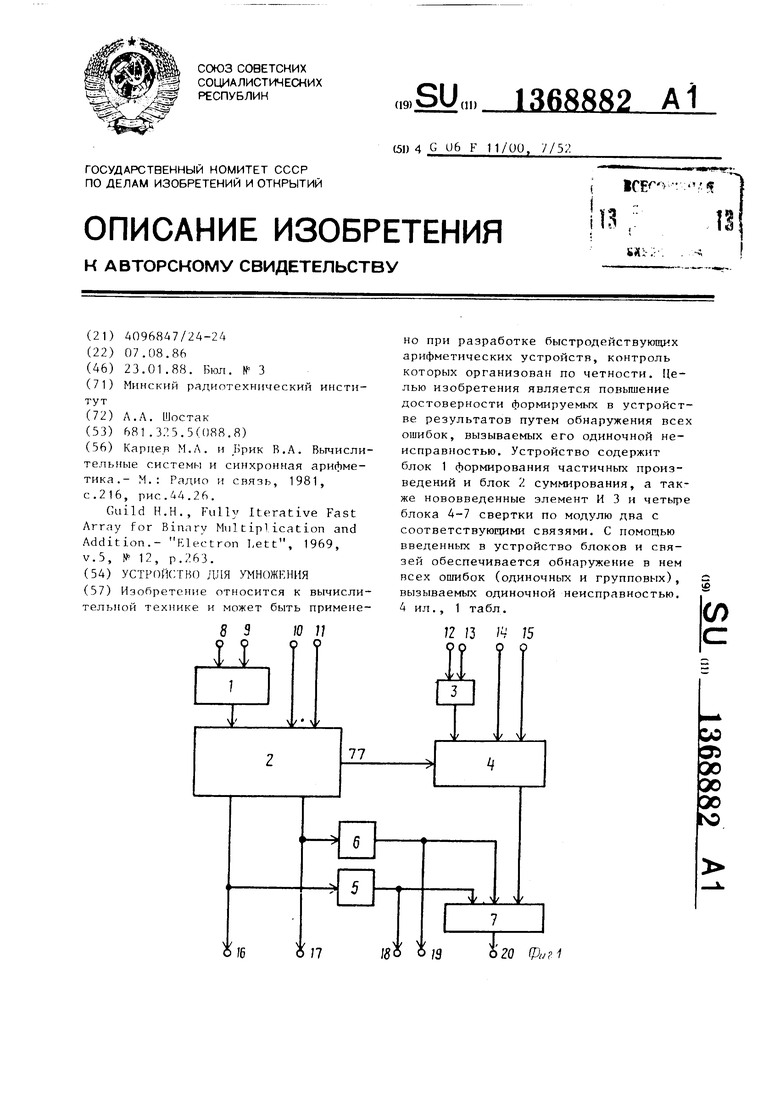

На фиг.1 приведена структурная схема устройства для умноженияj на фиг.2 - функциональная схема блока формирования частичных произведений для случая перемножения в устройстве А-разрядных чисел; на фиг.3 - функциональная схема блока суммирования, для этого же случая; на фиг.4 - функциональная схема одноразрядного двоичного сумматора с дублирующим переносом, используемого в блоке суммирования .

Устройство для умножения (фиг.1) содержит блок 1 формирования частичных произведений, блок 2 суммировани элемент И 3, блоки А-7 свертки по модулю два с первого по четвертый соответственно, вход 8 множимого, вход 9 множителя, вход 10 первого слагаемог вход 11 второго слагаемого, вход 12 четности множимого, вход 13 четности множителя, вход 14 четности первого слагаемого, вход 15 четности второго слагаемого, выход 16 старшей части результата, выход 17 младшей части результата, выход 18 четности старше части результата, выход 19 четности младшей части результата устройства и выход 20 признака ошибки. Первый и второй входы блока 1 формирования частичных произведений соединены с входами 8 и 9 множимого и множителя соответственно, выход блока 1 формирования частичных произведений соединен с первым входом блока 2 суммирования, второй и третий входы которог соединены с входами 10 и 11 первого и второго слагаемых соответственно, выход старших разрядов суммы блока 2 суммирования соединен с входом второго блока 5 свертки по модулю два и является выходом 16 старшей части результата устройства, выход младших разрядов суммы блока 2 суммирования соединен с входом третьего блока 6 свертки по модулю два и является выходом 17 младшей части результата устройства, первый и второй входы

fi

0

элемента И 3 соединены с входами 12 и 13 четностей множимого и множителя соответст.венно, выход элемента И 3 соединен с первым входом первого блока 4 свертки по модулю два, второй и третий входы которого соединены с входами 14 и 15 четностей первого и второго слагаемых соответственно, четвертый вход первого блока 4 свертки по модулю два соединен с выходом дублирующих переносов блока 2 суммирования, выход второго блока 5 свертки по модулю два соединен с первым входом четвертого блока 7 свертки по модулю два и является выходом 18 четности старшей части результата устройства, выход третьего блока 6 свертки по модулю два соединен с вторым входом четвертого блока 7 свертки по модулю два и является выходом 19 четности младшей части результата устройства, выход первого блока 4 свертки по модулю два соединен с третьим входом четвертого блока 7 свертки по модулю два, выход которого является вьосодом 20 признака ошибки устройства.

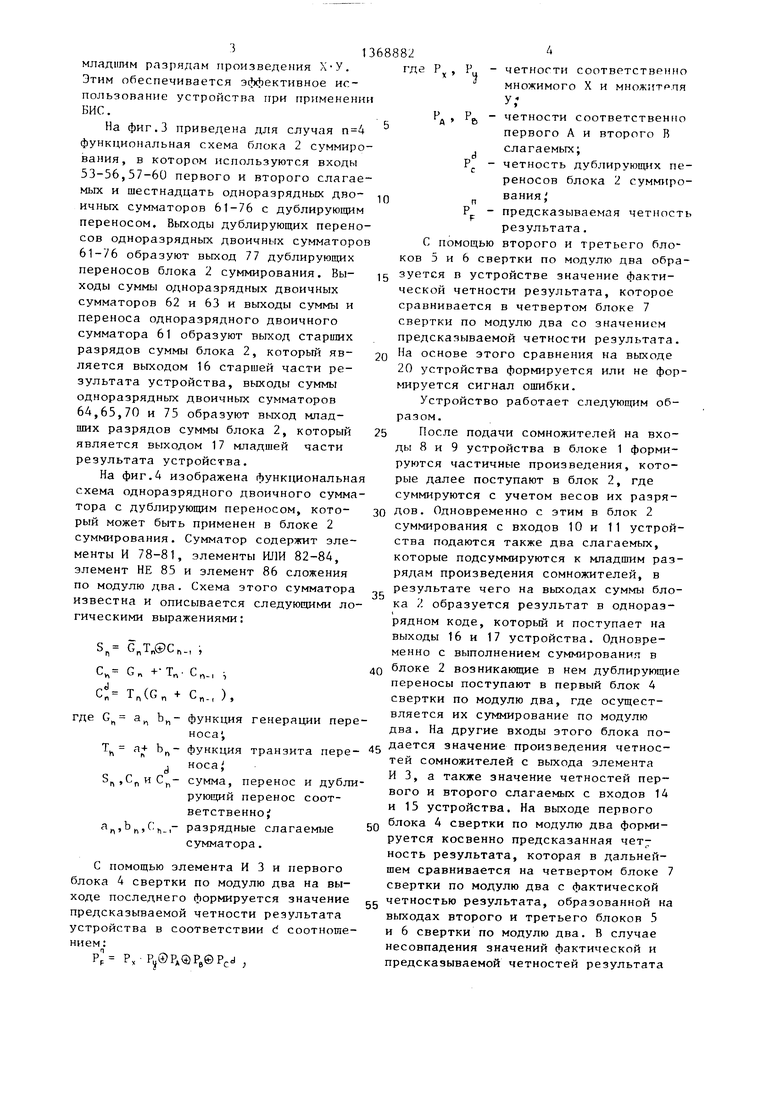

Блок 1 предназначен для формирования частичных произведений множимого на цифры множителя. Он может быть реализован в виде матрицы двухвходо- вых элементов И. На фиг.2 для случая перемножения в устройстве 4-разрядных g сомножителей изображена такая матрица. Она содержит шестнадцать двух- входовых элементов И 21-36 с выходами с 37-52 соответственно.

В блоке 2 осуществляется суммирование частичных произведений, формируемых в блоке 1 и поступающих на первый вход блока 2 суммирования с учетом весов их разрядов. Кроме частичных произведений в блок 2 поступают еще два слагаемых через его второй и третий входы с входов 10 и 11 устройства. Этим самым обеспечивается реализация в устройстве умножения следующей сложной функции:

5

0

0

5

F X-YH-A + B

где X, Y, - п- разрядные соответственно множимое и мно- житель

А, В - п- разрядные соответственно первое и второе слагаемое.

Отметим, что п-разрядные слагаемые А и В подсуммируются в блоке 2 к п

младишм разрядам произведения Х-У. Этим обеспечивается эффективное использование устройства при применении БИС.

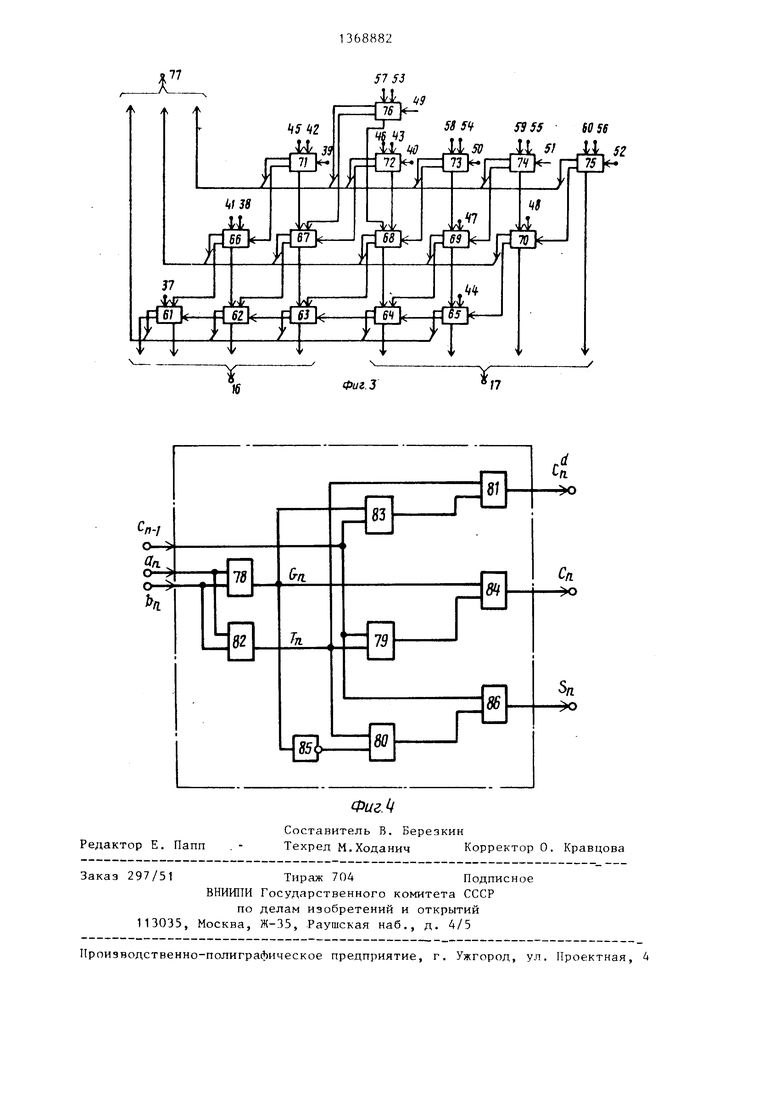

На фиг.З приведена для случая функциональная схема блока 2 суммирования, в котором используются входы 53-56,57-60 первого и второго слагаемых и шестнадцать одноразрядных двоичных сумматоров 61-76 с дублирующим переносом. Выходы дублирующих переносов одноразрядных двоичных сумматоров 61-76 образуют выход 77 дублирующих переносов блока 2 сумтчирования. Выходы суммы одноразрядных двоичных сумматоров 62 и 63 и выходы суммы и переноса одноразрядного двоичного сумматора 61 образуют выход старишх разрядов суммы блока 2, который является выходом 16 старшей части результата устройства, выходы суммы одноразрядных двоичных сумматоров 64,65,70 и 75 образуют выход младших разрядов суммы блока 2, который является выходом 17 младшей части результата устройства.

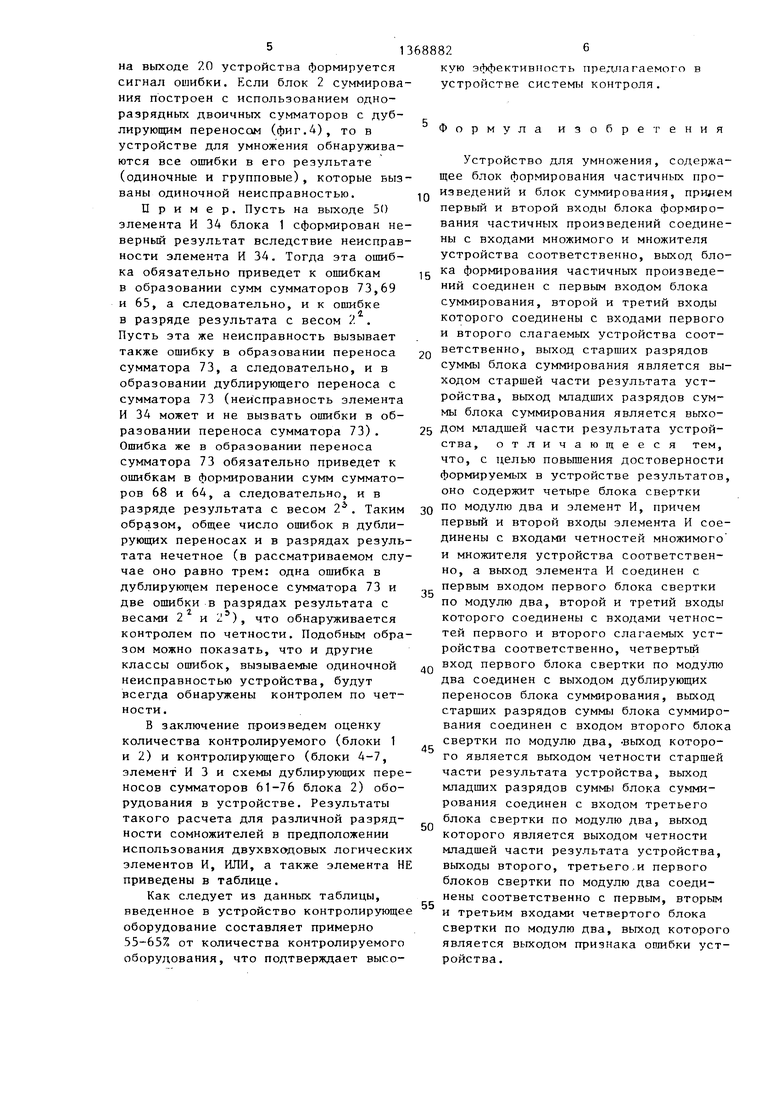

На фиг,4 изображена функциональная схема одноразрядного двоичного сумматора с дублирующим переносом, который может быть применен в блоке 2 суммирования. Сумматор содержит элементы И 78-81, элементы ШШ 82-84, элемент НЕ 85 и элемент 86 сложения по модулю два. Схема этого сумматора известна и описывается следующими логическими выражениями:

1

с„т„®с,., ,

с„ +-т„

Tn(Gn +

Р

- П-1 1

Сп-, ),

де

G.

Т h

а+

Ьп5п.,Ь, функция генерации переноса;

функция транзита пере носа

сумма, перенос и дублирующий перенос соответственноразрядные слагаемые сумматора,

С помощью элемента И 3 и первого блока 4 свертки по модулю два на выходе последнего формируется значение предсказываемой четности результата устройства в соответствии d соотношением:

п

PF Р, Р ®РД®РЦ©РС

и

368882 где

Р,. 10

1

РЬ Р Р 15

20

25

четности соответственно

множимого X и МНОЖИТРЛЯ

у;

четности соответственрю первого А и второго В слагаемых;

четность дублирующих переносов блока 2 суммирования,

предсказываемая четность результата.

С помощью второго и третьего блоков 5 и 6 свертки по модулю два образуется в устройстве значение фактической четности результата, которое сравнивается в четвертом блоке 7 свертки по модулю два со значением предсказываемой четности результата. На основе этого сравнения на выходе 20 устройства формируется или не формируется сигнал ошибки.

Устройство работает следующим образом.

После подачи сомножителей на входы 8 и 9 устройства в блоке 1 формируются частичные произведения, которые далее поступают в блок 2, где суммируются с учетом весов их разрядов. Одновременно с этим в блок 2 суммирования с входов 10 и 11 устройства подаются также два слагаемых, которые подсуммируются к младшим разрядам произведения сомножителей, в результате чего на выходах суммы блока 2 образуется результат в одноразрядном коде, который и поступает на выходы 16 и 17 устройства. Одновременно с выполнением суммирования в блоке 2 возникающие в нем дублирующие переносы поступают в первый блок 4 свертки по модулю два, где осуществляется их суммирование по модулю два. На другие входы этого блока по- g дается значение произведения четнос- тей сомножителей с выхода элемента И 3, а также значение четностей первого и второго слагаемых с входов 14 и 15 устройства. На выходе первого блока 4 свертки по модулю два формируется косвенно предсказанная четность результата, которая в дальнейшем сравнивается на четвертом блоке 7 свертки по модулю два с фактической gc четностью результата, образованной на выходах второго и третьего блоков 5 и 6 свертки по модулю два. В случае несовпадения значений фактической и предсказываемой четностей результата

30

35

40

50

на выходе .0 устройства формируется сигнал ошибки. Если блок 2 суммирования построен с использованием одноразрядных двоичных сумматоров с дублирующим переносом (фиг,4), то в устройстве для умножения обнаруживаются все ошибки в его результате (одиночные и групповые), которые вызваны одиночной неисправностью.

Пример. Пусть на выходе 50 элемента И ЗА блока 1 сформирован неверный результат вследствие неисправности элемента И 34. Тогда эта ошибка обязательно приведет к ошибкам в образовании сумм сумматоров 73,69 и 65, а следовательно, и к ошибке в разряде результата с весом . . Пусть эта же неисправность вызывает также ошибку в образовании переноса сумматора 73, а следовательно, и в образовании дублирующего переноса с сумматора 73 (неисправность элемента И 34 может и не вызвать ошибки в образовании переноса сумматора 73). Ошибка же в образовании переноса сумматора 73 обязательно приведет к ошибкам в формировании сумм сумматоров 68 и 64, а следовательно, и в разряде результата с весом 2. Таким образом, общее число ошибок в дублирующих переносах и в разрядах результата нечетное (в рассматриваемом случае оно равно трем: одна ошибка в дублирующем переносе сумматора 73 и две ошибки в разрядах результата с весами 2 и 2), что обнаруживается контролем по четности. Подобным образом можно показать, что и другие классы ошибок, вызываемые одиночной неисправностью устройства, будут всегда обнаружены контролем по четности.

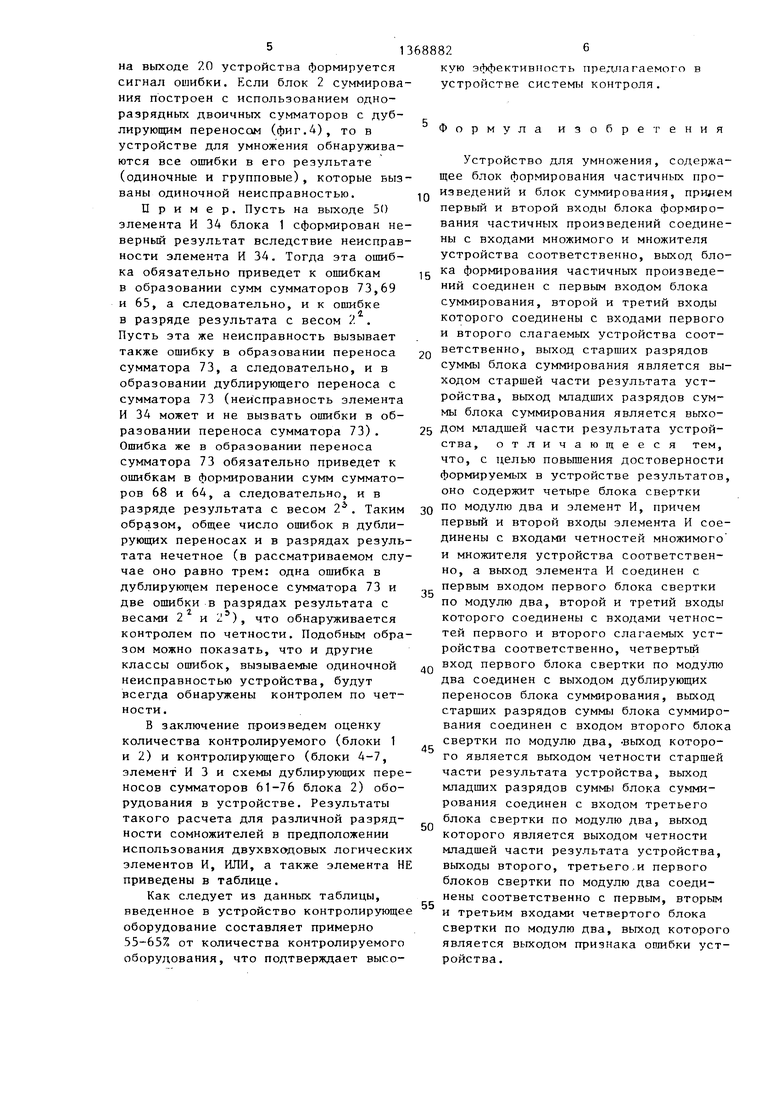

В заключение произведем оценку количества контролируемого (блоки 1 и 2) и контролирующего (блоки 4-7, элемент И 3 и схемы дублирующих переносов сумматоров 61-76 блока 2) оборудования в устройстве. Результаты такого расчета для различной разрядности сомножителей в предположении использования двухвходовых логически элементов И, ИЛИ, а также элемента Н приведены в таблице.

Как следует из данных таблицы, введенное в устройство контролирующе оборудование составляет примерно 55-65% от количества контролируемого оборудования, что подтверждает высо

5

0

кую эффективность предлагаемого в устройстве системьЕ контроля.

Формула изобретения

Устройство для умножения, содержащее блок формирования частичных произведений и блок суммирования, принем первый и второй входы блока формирования частичных произведений соединены с входами множимого и множителя устройства соответственно, выход блока формирования частичных произведений соединен с первым входом блока суммирования, второй и третий входы которого соединены с входами первого и второго слагаемых устройства соответственно, выход старших разрядов суммы блока суммирования является выходом старшей части результата устройства, выход младших разрядов суммы блока суммирования является выхо- 5 дом младшей части результата устройства, отличающееся тем, что, с целью повьшения достоверности формируемых в устройстве результатов, оно содержит четыре блока свертки Q по модулю два и элемент И, причем

первый и второй входы элемента И соединены с входами четностей множимого и множителя устройства соответственно, а выход элемента И соединен с первым входом первого блока свертки по модулю два, второй и третий входы которого соединены с входами четностей первого и второго слагаемых устройства соответственно, четвертый вход первого блока свертки по модулю два соединен с выходом дублирующих переносов блока суммирования, выход старших разрядов суммы блока суммирования соединен с входом второго блока свертки по модулю два, -выход которого является выходом четности старшей части результата устройства, выход младших разрядов суммы блока суммирования соединен с входом третьего блока свертки по модулю два, выход которого является выходом четности младшей части результата устройства, выходы второго, третьего,и первого блоков свертки по модулю два соединены соответственно с первым, вторым и третьим входами четвертого блока свертки по модулю два, выход которого является выходом признака ошибки устройства.

5

0

5

0

55

57 53

6056

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1675879A1 |

| Устройство для умножения | 1989 |

|

SU1683016A1 |

| Устройство для деления | 1990 |

|

SU1721603A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Матричное устройство для умножения чисел (его варианты) | 1983 |

|

SU1160398A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

Изобретение относится к вычислительной технике и может быть применено при разработке быстродействующих арифметических устройств, контроль которых организован по четности. Целью изобретения является повышение достоверности формируемых в устройстве результатов путем обнаружения всех ошибок, вызываемых его одиночной неисправностью. Устройство содержит блок 1 формирования частичных произведений и блок 2 суммирования, а также нововведенные элемент И 3 и четыре блока А-7 свертки по модулю два с соответствующими связями. С помощью введенных в устройство блоков и связей обеспечивается обнаружение в нем всех ошибок (одиночных и групповых), вызываемых одиночной неисправностью. 4 ил., 1 табл, |) (Л

L. 00-9

&/1

Гп

ci

Cn

S«

| Карцев М.Л | |||

| и Брик В.А | |||

| Вычислительные системы и синхронная арифметика.- М.: Радио и связь, 1981, с | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Guild Н.Н., Fully Iterative Fast Array for Binary Multiplication and Addition.- PUectron l,ett, 1969, V.5, № 12, p.263. | |||

Авторы

Даты

1988-01-23—Публикация

1986-08-07—Подача