Изобретение относится к автоматике и вычис лительной технике. Известно устройство для проверки реверсивного счетчика, содержащее счетчик, логические схемы, триггеры и схему И 1. Однако известное устройство не обеспечивает достаточную достоверность контроля. Наиболее близко предлагаемому по технической сущности устройство ДЛЯ контроля реверсивного счетчика, содержащее дешифраторы,, схему ИЛИ, схему управления реверсом, коммутатор режимов, при зтом два дешифратора подключены к выходам реверсивного счетчика и настррены на взаимно инверсньте комбинации два входа .и даа выхода блока управления реверсом соединены с соответствующими выходами и входами реверсивного счетчика, два входа коммутатора режимов соединены с соответствующ1{ми входами устройства, три выхода соединены соответственно с третьим, четвертым и пятым входами схемы управления реверсом, шестой вход которой подключен к счетному входу реверснвного счетчика, первый и второй входы схемы управления реверсом подключены соответственно ко входам первого и второго дешифраторов, выходы jcoTopbix через схему ИЛИ соединены с выходом устройства 2 Недостатком известного устройства вляется невозможность обнаружения постоянного отказа типа короткого замыкания в элемента и цепях переноса реверснвного счетчика, что существенно снижает достоверность контроля. Цель изобретения - повыщенне достоверности контроля. . Для достижения указанной цели в устройство ДЛЯ контроля реверсивного счетчика, содержащего блок индикации, блок управления реверсом, при этом выход блока индикации является выходом устройства, группа входов блока индикации подключена к группе выходов контролируемого реверсивного счетчика, суммирующий и вьпштающий входы которого подключены соответственно к первому и второму входам блока управления реверсом, третий вход которого соединен с управляющим входом блока индикации, четвертый и пятый входы блока управления реверсом подключены соответственно к первому и второму выходам коммутатора режимов, первый вход которого является единичным . входом устроства, а второй вход - нулевым входом устроства, введены управляемый делитель, элементы И и элемент ИЛИ, причем первый выход управляемого делителя подключен к третьему входу блока управления реверсом, шестой вход которюго. соединен со вторым выходом управляемого делителя, управляющий вход которого подключен к выходу коммутатора режимов и к первому входу первого элемента И, второй вход которого соединен с первым входом второго элемента И, с импульсным входом управляемого делителя и с импульсным входом устройства, выход первого элемента И подключен к первому входу элемент ИЛИ, выход которого соединен со счетным входом контролируемого реверсивного счетчика, второй вход элемента ИЛИ подключен к выходу второго элемента И, второй вход которого, соединен с нулевым входом устройства.

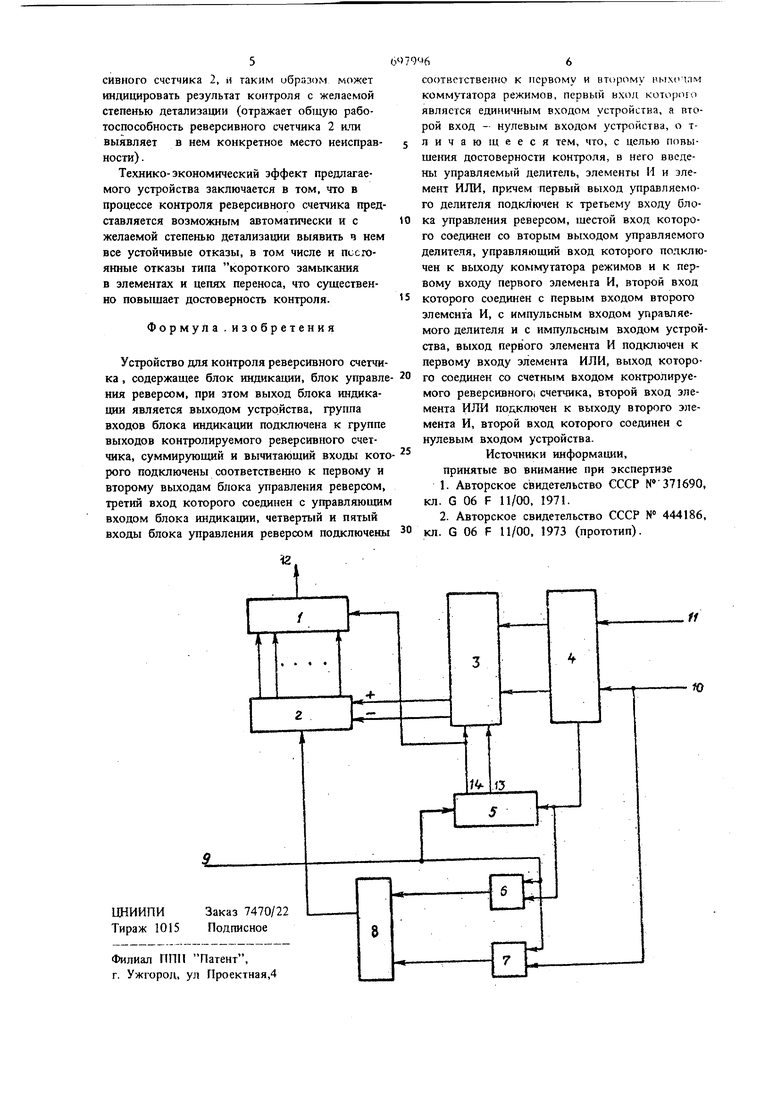

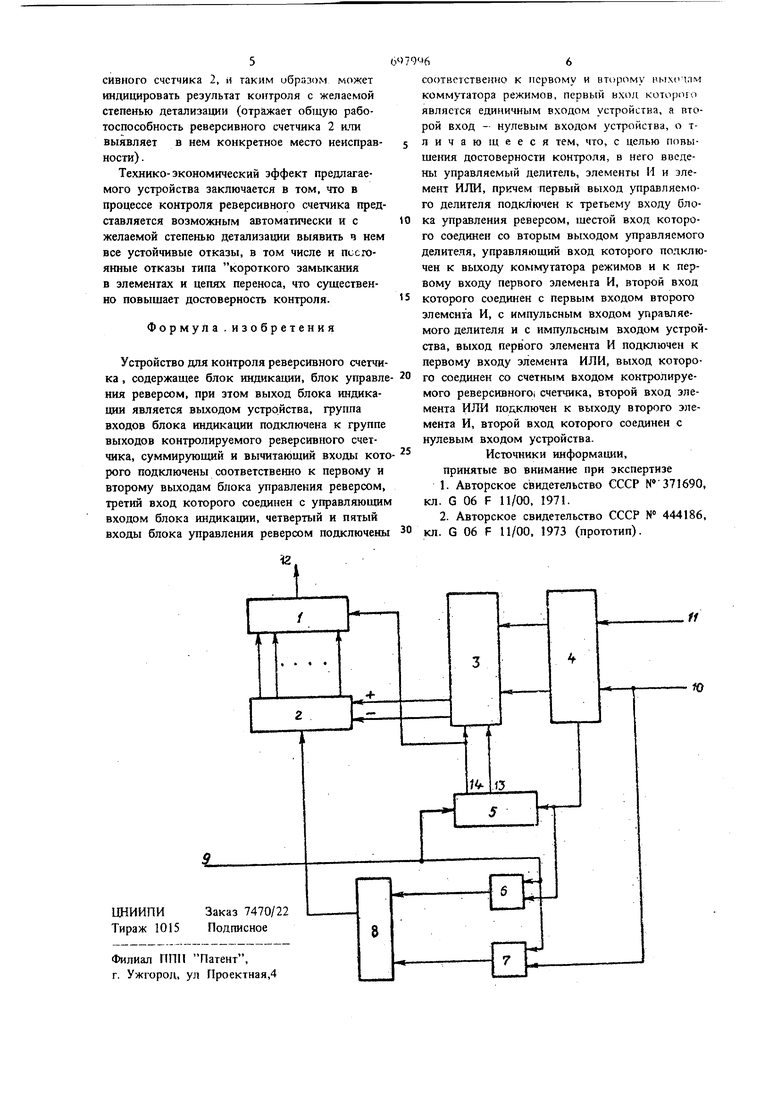

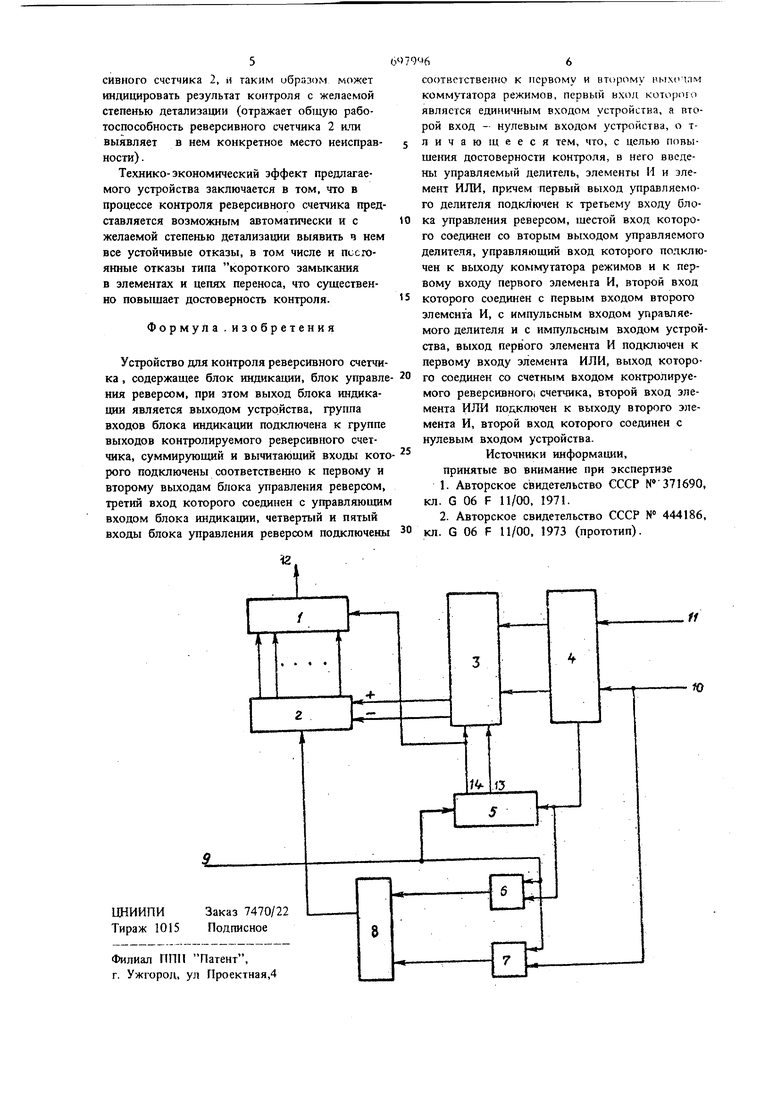

На чертеже изображена блок-схема предлагаемого устройства., .

Устройство содержит блок индикации 1, контролируемый реверсивный счетчик 2, блок управления реверсом 3, коммутатор режимов 4, управляемый делитель 5, элементы И 6,7, элемент И.ПИ 8, вход 9 импульсов запуска реверсивного счетчика, входы 10, 11 устройства, выход 12 устройства.

Устройство работает следуюишм образом.

В рабочем режиме на вход 11, поступает потенциал логической единицы, разрешающий прохождение сигналов управления реверсом со входа 11. При 1 (О) на входе М, на выходе блока управления реверсом 3 появляется сигнал, соответствующий сложению (вычитанию) . Импульсы запуска поступают со входа 9 через управляемый делитель 5 на счетный вход реверсивного счетчика 2.

В режиме контроля на вход 9 устройства поступает уровень логического нуля. Он запрещает прохождение сигнала управления реверсом со входа 11, устанавливает уровень I на третьем выходе коммутатора режимов 4 и обеспечивает работу устройства в режиме контроля. Уровень О на входе 9 устройств запрещает прохождение импульсов запуска на счетный вход реверсивного счетчика 2 со входа 9 устройства через элемент И 7, а уровень 1 на третьем выходе коммутатора режимов 4 разрешает их прохождение через элемент И 6 и обеспечивает работу управляемого делителя 5. В исходном состоянии по началу контроля на выходе 13 управляемого делителя 5 образуется сигнал, по которому на выходе блока управления реверсом 3 устанавливается потенциал, соответствуюцдай сложению. Под действием первого, а затем и второго импульсов запуска на выходе 13 управляемого делителя 5 сохраняется сигнал, по которому на выходе блока управления реверсом 3 образуется потенциал, соответствующий сложению. В случае исправности первых двух разрядов реверсивного счетчика 2 последовательно изменяется состояние его первого разрядами через цепь переноса сложения изменяется состояние второго разряда, т.е. записывается число два. Под действием третьего импульса запуска сигнал на выходе 13 управляемого делителя 5 снимается, а на его выходе 14 образуется сигнал, по которому на выходе блока управления реверсом 3 устанавливается потенциал, соответствующий вычитанию. Этот же импульс в реверсивном счетчике 2 -изменяет состояние первого разряда, а через цепь переноса, соответствующую вычитанию, изменяется состояние второго разряда реверсивного счетчика 2, т.е. происходит вычитание единицы из числа, записанного в реверсивном счетчике ,2, и в нем оказывается записанным число один. В этом состоянии реверсивный счетчик 2 опрашивается в блоке индикации 1 сигналом с выхода 14 управляемого делителя 5.

Последуюадае четвертый и пятый импульсы запуска вновь способствуют образованию на выходе блока управления реверсом 3 потенциала, соответствующего сложению, а шестой импульс запуска - вычитанию. Соответственно в реверсивном счетчике 2 сначала будет записано число три, а затем число два,и в этом его состоянии будет произведен очередной опрос блока индикации 1. Затем процесс контроля реверсивного счетчика 2 повторяется, т.е последующие седьмой и восьмой импульсы запуска устанавливают в счетчике число четыре, а девятый импульс запуска - число три и производится опрос блока индикации 1, и так далее до окончания режима контроля.

Таким образом, опрос блока индикации 1 производится после того, как первый разряд реверсивного счетчика 2 изменит свое состояние как в результате воздействия на него сигнала по цепи сложения, так и по цепи вычитания.

В случае возникновения любой постоянной неисправности, в том числе типа короткого замыкания в элементах и цепях переноса, нарушается ожидаемая очередность загшси числа в реверсивном счетчике 2. Поэтому опрос блока индикации 1 сигналом с выхода 14 управляемого делителя 5 позволяет выявить временное несоответствие в последовательности импульсов, отражающих состояние ревер

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения статистических характеристик | 1976 |

|

SU716044A1 |

| Устройство для автоматического контроля многоканального объекта | 1982 |

|

SU1104472A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Счетчик ампер-часов | 1977 |

|

SU702301A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Устройство для контроля счетчиков | 1977 |

|

SU741268A2 |

| Устройство контроля дальномера | 1975 |

|

SU563656A1 |

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

Авторы

Даты

1979-11-15—Публикация

1978-03-16—Подача