лами i-oro элемента ИЛИ, выход которого соединен с соответствующим информационным входом коммутатора, входы управления коммутатора соединены с сответствующими выходами управления распределителя сдвига, первый выход коммутатора - со счетным входом первого счетчика цифр произведения (делимого) , j-ые выходы коммутатора (j 2(2п-1) - соответственно с первыми входами )-ых элементов ИЛИ счетных сигналов, вьаходы которых соединены соответственно со счетными входами j-ых счетчиков цифр произведения (делимого).

В основу работы известного устройства заложен способ деления без восстановления остатка. Способ вычисления произведения аналогичен способу вычисления частного 2 ,

Однако быстродействие известного устройства ограничивается временем прохождения сигналов переноса в разрядах счетчика множителя (частного). Кроме того; использование ячеек заг держки счетчиков произведения (делимого) и ячейки задержки тактирующего устройства (делителя на основе системы счисления) для устранения временных наложений импульсов усложняет синхронизатшю работы отдельных узлов известного устройства.

Цель изобретения -- повышение быстродействия.

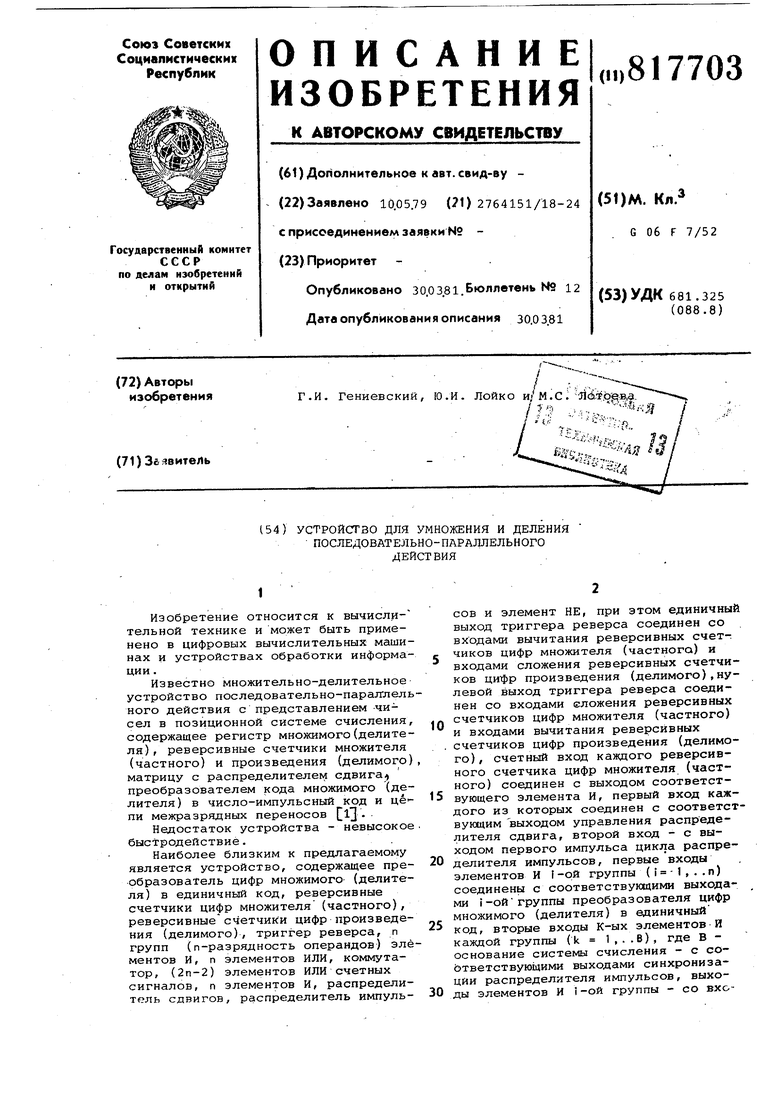

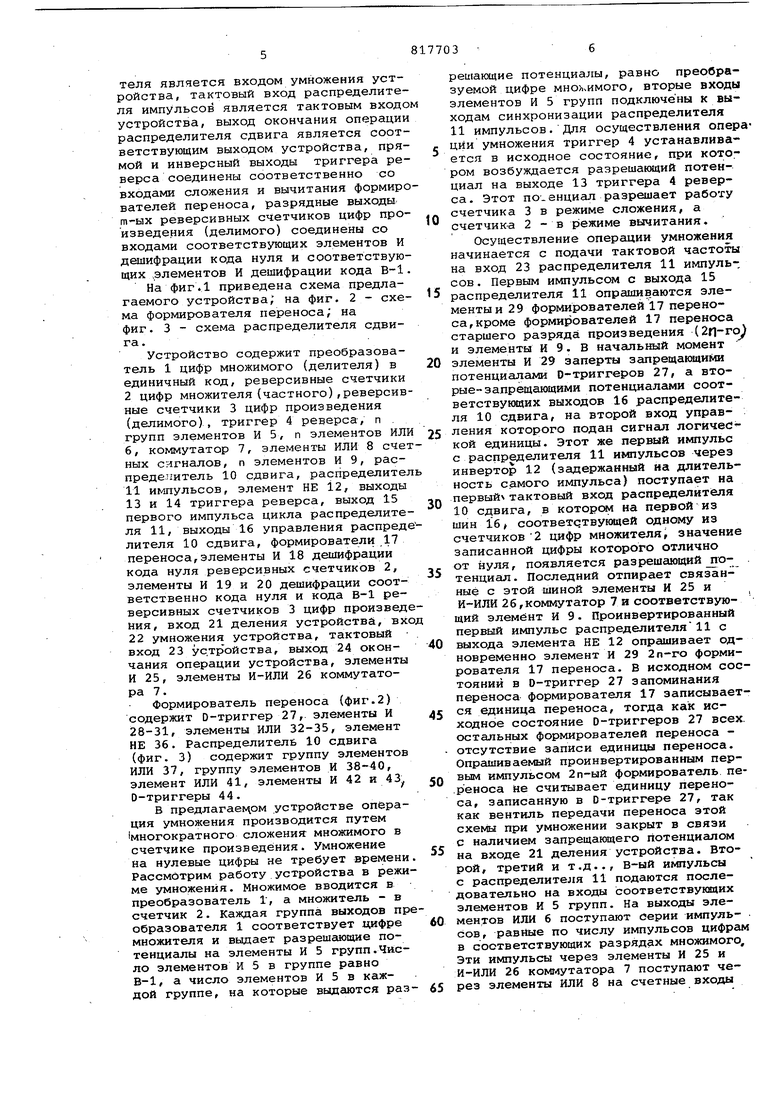

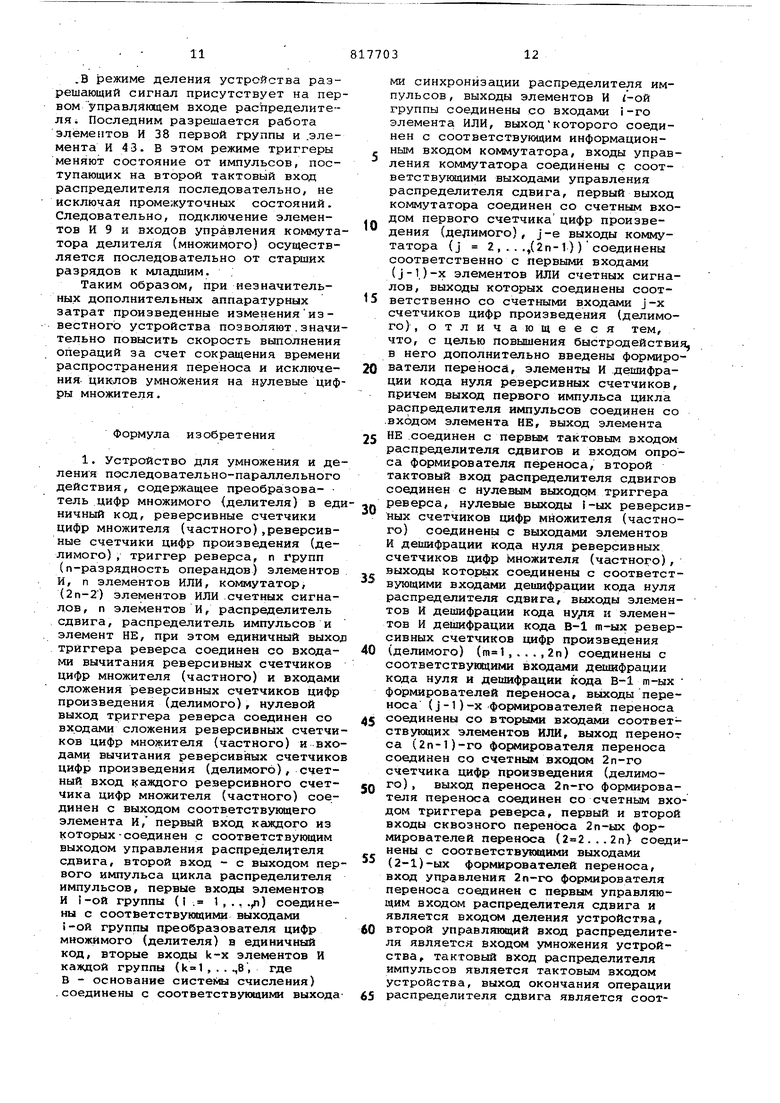

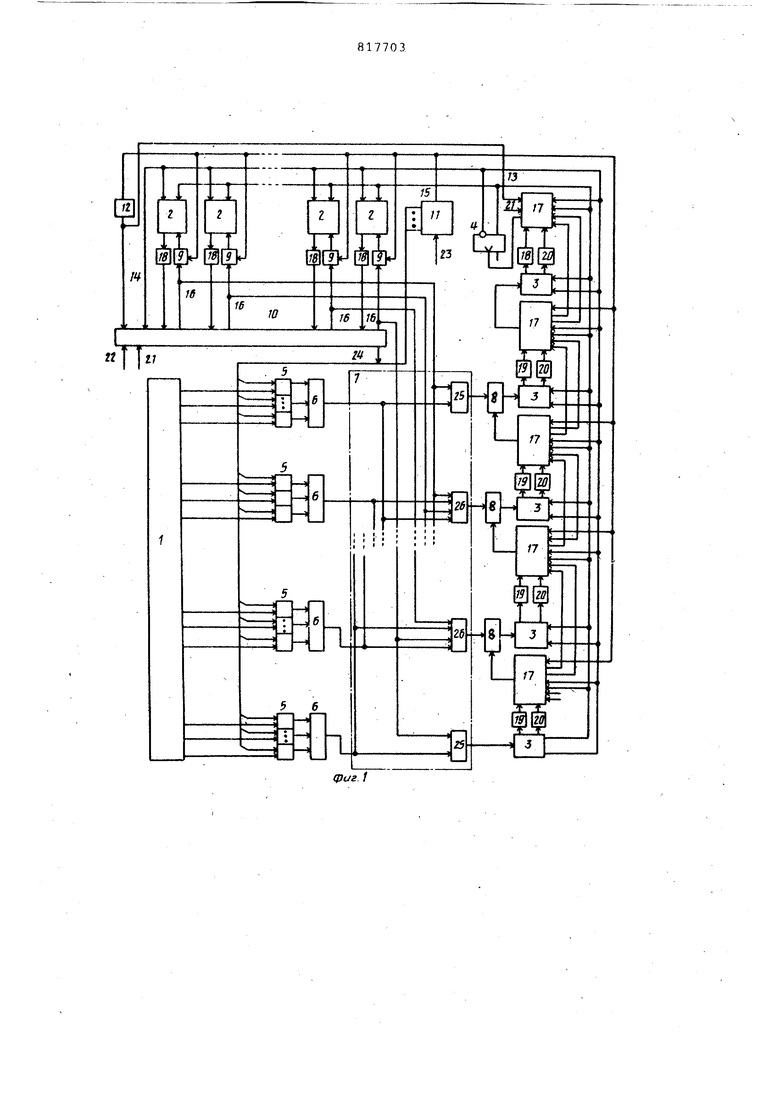

Поставленная цель достигается тем что в устройство для умножения и деления последовательно-параллельного действия, содержащее преобразователь цифр множимого (делителя) в единичный код, реверсивные счетчики цифр множителя (частного), реверсивные Счетчики цифр произведения (делимого) , триггер реверса, п групп (п - разрядность операндов) элементов И, п элементов ИЛИ, коммутатор, . (2п-2) элементов ИЛИ счетных сигналов, п элементов И, распределитель сдвига, распределитель импульсов и элемент НЕ при этом единичный выход триггера реверса соединен со входами вычитания реверсивных счетчиков цифр множителя (частного) и входами сложения реверсивных счетчиков цифр произведения Тделимого), нулевой выход триггера реверса соединен со входами сложения реверсивных счетчиков цифр множителя (частного) и входами врлчитания реверсивных счетчиков цифр произведения (делимого),счетный вход.каждого реверсивного счетчика цифр множителя (частного) соединен с выходом соответствующего, элемента И, первый вход каждого из которых соединен с соответствуюцщм выходом управления распределителя сдвига, второй вход - с выходом первого импульса цикла распределителя импульсов, первые входы элементов И . группы (i 1,.. .п) соединены с соответствующими выходами i-ой группы преобразователя цифр множимого (делителя) в единичный код, вторые входы k-x элементов И каждой группы (k 1,...В), где В основание системы счисления) соединены с соответствукяцими выходами синхронизации распределителя импуль7 сов, выходы элементов И i-ой группы соединены со входами i-ro элемента ИЛИ, выход которого соединен с соответствующим информационным входом коммутатора, входы управления коммутатора соединены с соответствующими выходами управления распределителя сдвига, первый выход коммутатора соединен со счетным входом первого счетчика цифр произведения (делимого) j-e выходы коммутатора (j 2,... (2п-1)) соединены соответственно с первыми входами (j-l)-x элементов ИЛИ счетных сигналов, выходы которого соединены соответственно со счетными входами J-X счетчиков цифр произведения (делимого) дополнительно введены формирователи переноса, элементы И дешифрации кода нуля реверсивных счетчиков, причемВЫХОД первого импульса цикла распределителя импульсов соединен со входом элемента НЕ, выход элемента НЕ соединен с первым тактовым входом распределителя сдвигов и входом опроса формирователя переноса, второй тактовый вход распределителя сдвигов соединен с нулевым выходом триггера реверса,нулевые выходы i-ых реверсивных счетчиков цифр множителя (частного) соединены с выходами элементов И дешифрации кода нуля реверсивных счетчиков цифр множителя (частного), выходы которых соединены с соответствующими входами дешифрации кода нуля распределителя сдвига.у выходы элементов И дешифрации кода нуля и -элементов И дешифрации кода В-1 т-ых реверсивных счетчиков цифр произведения (делимого) (т 1,..2п) соединены с соответствующими входами дешифрации кода нуля и дешифрации кода В-1 т-ых формирователей переноса, выходы переноса (j-l)-x формирователей переноса соеднены со вторыми входами соответствующих элементов ИЛИ, выход переноса (2п-1)-го формирователя переноса соединен со счетным входом 2п-го счетчика цифр произведения (делимого),выход переноса 2п-го формирователя переноса соединен со счетным входом триггера реверса, первый и второй входы сквозного переноса 2-ых формирователей переноса (.,..2п) соединены с соответствующими выходами (2-1.)-ых формирователей переноса, вход управления 2п-го формирователя переноса соединен с первым управляющим входом распределителя сдвига и является входом деления устройства, второй управляющий вход распределителя является входом умножения устройства, тактовый вход распределите ля импульсов является тактовым вход устройства, выход окончания операци распределителя сдвига является соот ветствующим выходом устройства, пря мой и инверсный выходы триггера ре верса соединены соответственно со входами сложения и вычитания формир вателей переноса, разрядные выходы т-ых реверсивных счетчиков цифр про изведения (делимого) соединены со входами соответствующих элементов И дешифрации кода нуля и соответствую щих .элементов И дешифрации кода В-1 На фиг .1 приведена схема предлагаемого устройства; на фиг. 2 - схе ма формирователя переноса; на фиг, 3 - схема распределителя сдвига. Устройство содержит преобразователь 1 цифр множимого (делителя) в единичный код, реверсивные счетчики 2 цифр множителя(частного),реверсив ные счетчики 3 цифр произведения (делимого), триггер 4 реверса, п . групп элементов И 5, п элементов ИЛ 6, коммутатор 7, элементы ИЛИ 8 сче ных сигналов, п элементов И 9, распределитель 10 сдвига, распределите 11 импульсов, элемент НЕ 12, выходы 13 и 14 триггера реверса, выход 15 первого импульса цикла распределите ля 11, выходы 16 управления распред лителя 10 сдвига, формирователи 17 переноса,элементы И 18 дешифрации кода нуля реверсивных счетчиков 2, элементы И 19 и 20 дешифрации соответственно кода нуля и кода В-1 реверсивных счетчиков 3 цифр произведе ния, вход 21 деления устройства, вхо 22 умножения устройства, тактовый вход 23 ус.тройства, выход 24 окончания операции устройства, элементы И 25, элементы И-ИЛИ 26 коммутатора 7 . Формирователь переноса (фиг.2) содержит D-триггер 27, элементы И 28-31, элементы ИЛИ 32-35, элемент НЕ 36. Распределитель 10 сдвига (фиг. 3) содержит группу элементов ИЛИ 37, группу элементов И 38-40, элемент ИЛИ 41, элементы И 42 и 43 О-триггеры 44. В предлагае1 ом устройстве операция умножения производится путем многократного сложения множимого в счетчике произведения. Умножение на нулевые цифры не требует времени. Рассмотрим работу устройства в режиме умножения. Множимое вводится в преобразователь 1, а множитель - в счетчик 2. Каждая группа выходов пре образователя 1 соответствует цифре множителя и выдает разрешшощие потенциалы на элементы И 5 групп.Число элементов И 5 в группе равно В-1, а число элементов И 5 в каждой группе, на которые выдаются разрешающие потенциалы, равно преобразуемой цифре мно)1,имого, вторые входы элементов И 5 групп подключены к выходам синхронизации распределителя 11 импульсов. Для осуществления операции умножения триггер 4 устанавливается в исходное состояние, при котором возбуждается разрешающий потенциал на выходе 13 триггера 4 реверса. Этот ПО-енциал разрешает работу счетчика 3 в режиме сложения, а счетчик-а 2 - в режиме вычитания. Осуществление операции умножения начинается с подачи тактовой частоты на вход 23 распределителя 11 импуль-. сов. Первым импульсом с выхода 15 распределителя 11 опршливаются элементы и 29 формирователей 17 переноса, кроме формирователей 17 переноса старшего разряда произведения () и элементы И 9. В начальный момент элементы И 29 заперты запрещакяцими потенциалами D-триггеров 27, а вторые- запрещающими потенциалами соответствующих выходов 16 распределителя 10 сдвига, на второй вход управления которого подан сигнал логичеС кой единицы. Этот же первый импульс с распределителя 11 импульсов через инвертор 12 (задержанный на длительность самого импульса) поступает на пepвый тактовый вход распределителя 10 сдвига, в котором на первой из шин 16 соответдтвующей одному из счетчиков 2 цифр множителя, значение записанной цифры которого отлично от нуля, появляется разрешаюцдай jioтенциал. Последний отпирает связанные с этой шиной элементы И 25 и И-ИЛИ 26,коммутатор 7 и соответствующий элемент И 9. Проинвертированный первый импульс распределителя11 с выхода элемента НЕ 12 опрашивает одновременно элемент И 29 2п-го формирователя 17 переноса. В исходном состояний в О-триггер 27 запоминания переноса формирователя 17 записывается единица переноса, тогда как исходное состояние D-триггеров 27 всех, остальных формирователей переноса отсутствие записи единицы переноса. Опрашиваемый проинвертированным первым импульсом 2п-ый формирователь переноса Не считывает единицу переноса, записанную в D-триггере 27, так как вентиль передачи переноса этой схемы при умножении закрыт в связи с наличием запрещающего потенциалом на входе 21 деления устройства. Втоой, третий и т.д.., в-ый импульсы распределителя 11 подаются послеовательно на входы соответствукнцих лементов И 5 групп. На выходы элеентов ИЛИ 6 поступсцот серии импуль- ов, равйые по числу импульсов цифрам соответствующих разрядах множимого. ти импульсы через элементы И 25 и -ИЛИ 26 комглутатора 7 поступают чеез элементы ИЛИ 8 на счетные входы

соответствующих разрядов счетчика 3. После В импульсов тактовой частоты заканчивается один цикл работы распределителя 11 импульсов, а множимое однократно записывается в счетчик 3. Очередной первый импульс с выхода 15 распределителя 11 опрашивает формирователи 17 переноса и через открытый элемент И 9 вычитает единицу из i-pro разряда множителя. В каждом очередном цикле к содержимому счетчика 3 прибавляется значение множимого, а из i-ого разряда счетчика 2 вычитается единица. В случае возникновения в процессе сложения в счетчике 3 единиц сигнала переноса в старший разряд или сигнала сквозного переноса, они каждым импульсом с выхода 15 распределителя 11 записываются через выходы переноса формирователей 17 переноса и злементы ИЛИ 8 в соответствующие разряды счетчика 3. После того, как содержимое разряда счетчика 2 множителя, на которое производится умножение, после очередного вычитания единицы становится раврав.ным нулю, на выходе элемента И 18, дешифрации кода i-ого разряда счетчика 2 появляется сигнал, разрешающий переключение проинвертированным перг вым импульсом (выход элемента НЕ 12) по первому тактовому входу, распределителя 10 сдвигов. Выходной шиной 16 распределителя 10 сдвигов подключается вентиль 9 более младшего разряда, содержимое которого отлично от нуля, и другая, связанн ая с шиной 16, группа элементов И 25 и И-ИЛИ 26 коммутатора 7, т.е. происходит сдвиг множимого. Операция умножения заканчивается, когда значения всех разрядов счетчика 2 становятся равными нулю, и на шине 24 распределителя сдвигов появляется сигнал об окончании операции. .

Операция дешения чисел в предлагаемом устройстве осуществляется способом деления с восстановлением отрицательного остатка.Работа устройства в режиме деления происходит следующим образом. Делимое записывается в счетчике 3, а делитель - в преобразователь 1, причем младший разряд делимого записывается в младший разряд счетчика 3. Триггер 4 реверса устанавливается в исходное состояние, при котором счетчик 3 готов к работе в режиме сложения, а счетчик 2 - в режиме вычитания. В режиме деления, при наличии сигнала единицы на входе 21, переключение распределителя 10 сдвигов осуществляется по второму тактовому входу сигналом с выхода 14 счетчика 4 реверса. Сигналом на входе 21 разрешен также опрос О-триггера 27 2п-го формирователя 17 переноса, осуществляемый с выхода элемента НЕ 12 каждым первым импульсом распределителя 11. Осуществление операции деления начинается с подачи тактовой частоты на вход 23 устройства. Как и при умножении, первый импульс с выхода 15 распределения 11 не оказывает воздействия на состояние реверсивных счетчиков 2 и 3. Данный импульс, поступая с выхода элемента НЕ 12, опрашивает 2п-ый формирователь 17 переноса, считывает записанную в 0-триггер 27

формирователя единицу переноса и перебрасывает по счетному входу триггер 4 реверса. Изменение потенциалов на выходах последнего разрешает работу счетчика 3 в режиме вычитания, счетчика 2 - в режиме сложения, и переключает распределитель 10 сдвигов. Сигналом с выхода 16 распределителя 10 разрешается работа элемента И 9 старшего разряда частного и подключается связанная с выходом 16 распредеG лителя 10 группа элементов И 25 и И-ИЛИ 26 коммутатора 7. Следующими после первого В-1 импульсами, выдаваемыми распределителем 11 на элементы И 5, групп, осуществляется однократное вычитание делителя из содержимого старших разрядов счетчика 3. Первым импульсом следующего цикла работы распределителя 11 импульсов записывается единица в старший разряд

счетчика 2 и осуществляются межразрядные переносы в счетчике 3. Этим же инвертированным импульсом (с выхода элемента НЕ 12) , .опрашивается О-триггер 27 2п-го формирователя переноса, в случае положительного

остатка (отсутствие в D-триггере 27 единицы переноса) в течение второго цикла работы распределителя .11 значение делителя вторично вычитается из содержимого старших разрядов делителя, а первым импульсом третьего цикла работы распределителя 11 вторая единица записывается в старший разряд счетчика 2. Вычитание производится до образования в старших разрядах счетчика 2 отрицательного-остатка. В этом случае в D-триггер 27 2п-го формирователя 17 переноса записывается единица. Первым импульсом очередного цикла единица прибавляетQ ся к содержимому старшего разряда счетчика частного и этим же инвертированным импульсом перебрасывается триггер 4 реверса. Весь начавшийсяцикл работы .распределителя 11 счетчики 3 работают на сложение и в них

восстанавливается остаток предьщущего цикла, при этом в О-триггер 27 2п-го формирователя переноса записывается единица переноса.Первым импульсом следующего цикла дополнительно записанная единицы вычитается из старшего разряда счетчика 2, а этим же инвертированным импульсом считывается единица переноса из 2п-го формирователя 17 переноса и вторично

5 перебрасывается триггер 4, реверсируя работу счетчиков 2 и 3 и переключая распределитель 10 сдвигов в следующее положение. Распределитель сдвигов разрешает работу вентиля 9 более младшего разряда частного и подключает другую группу вентилей 7 матрицы сдвига делителя. Таким образом, в начавшемся цикле импульсы с элементов ИЛИ 6 поступают через коммутатор 7 на более младшие разряды счетчиков 3. Следуквдие циклы до обра зования отрицательного остатка счетчики 3 работают на вычитание, а счетчики 2 - на сложение. Операция деления производится до тех пор,пока не произойдет перекидывание триггера 4 реверса при образовании отрицательного остатка в младших разрядах счетчика 3 делимого, и восстановление его до положительного остатка или нуля. Тогда на выходе 23 появляется сигнал об окончании операции .

Быстродействие множительно-делительного устройства определяется тактовой частотой F. .Период следования тактирующих импульсов

где Т,- максимальная длительность переходных процессов в разряде счетчика 3 (2),

Tgi- длительность переходных процессов при переключении распределителя сдвигов. Длительность импульсов на выходе первого канала распределителя 11 импульсов должна быть не менее Т.

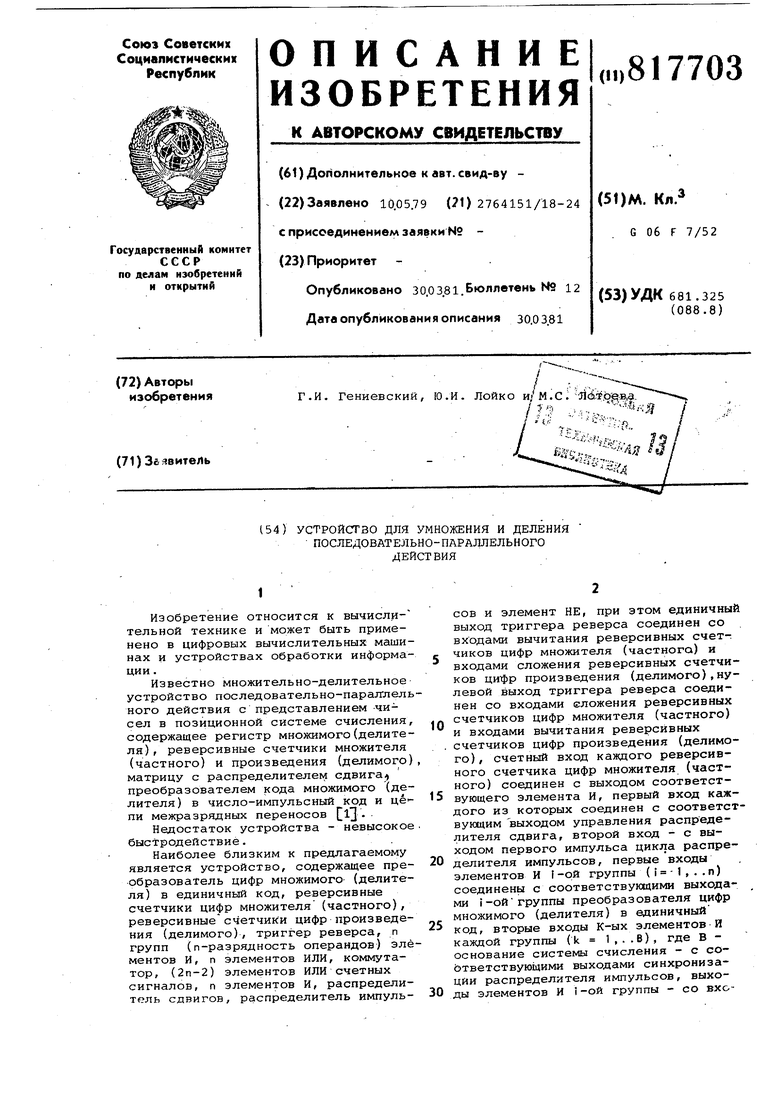

Формирователь 17 переноса работает следующим образом.

В режиме умножения, (режим сложения для счетчика 3) с выхода 13 сложения подается разрешающий потенциал на элемент И 31. Другой вход элемента И 31 подключен к выходу дешифрации В-1 данного счетчика 3. Когда в разряде счетчика 3 записана цифра В-1, на выходе элемента И 20 дешифрации кода В-1 обязательно присутствует высокий потенциал. При переполнении разряда счетчика 3 перепад напряжения с высокого на низкий по цепи элемента И 31, элементов ИЛИ 32 и 33, элемента НЕ 36 устанавливает О-триггер 27 в единичное состояние. Разрешающий потенциал с единичного выхода триггера 27 через второй вход элемента ИЛИ 32 подается на первый вход элемента И 29. Опросовым импульсом, поступающим на вход опроса формирователя, формируется единица переноса в следующий разряд при помощи элемента И 29. Задним фронтом опросового импульса D-триггер 27 возвращается в исходное состояние. В случае наличия единицы из предьщущего разряда в данный разряд и записанной в данном разряде счетчика цифры В-1 единица переноса через второй вход элемента ИЛИ 35, через элемент И 28, разрешенный высоким потенциалом с выхода элемента И 20 дешифрации кода В-1 данного разряда, подается на -первый вход элемента И 29 передачи переноса данного разряда. Опросовым импульсом формируется единица переноса из данного разряда в последующий и единица переноса из предыдущего разряда в данный. Т1ри этом в О-триггер 27 данного разряда записывается дополнительная единица

to переноса в последующий разряд, которая стирается по окончании опросового импульса (задним его фронтом).Организация записи единицы сквозного переноса в последующий разряд при

15 записанных в предыдущих разрядах цифрах В-1 осуществляется аначогично по первому входу элемента ИЛИ 35.

В режиме деления (режим вычитания для счетчика 3) разрешающий потенциал подается с входа вычитания форми20рователя на вход элемента И 30, другой вход которого подключен k выходу элемента И 9 дешифрации кода нуля состояния соответствующего счетчика 3. Работа схемы происходит аналогич25но режиму сложения для счетчика 3, только сигналом переполнения разряда счетчика является перепад потенциала с высокого на низкий при переходе состояния разряда счетчика S от

0 записанной цифры О к цифре В-1. Третий вход элемента И 29 2п-го формирователя соединён со входом управления формирователя. Распределитель сдвига работает следующим образом.

5

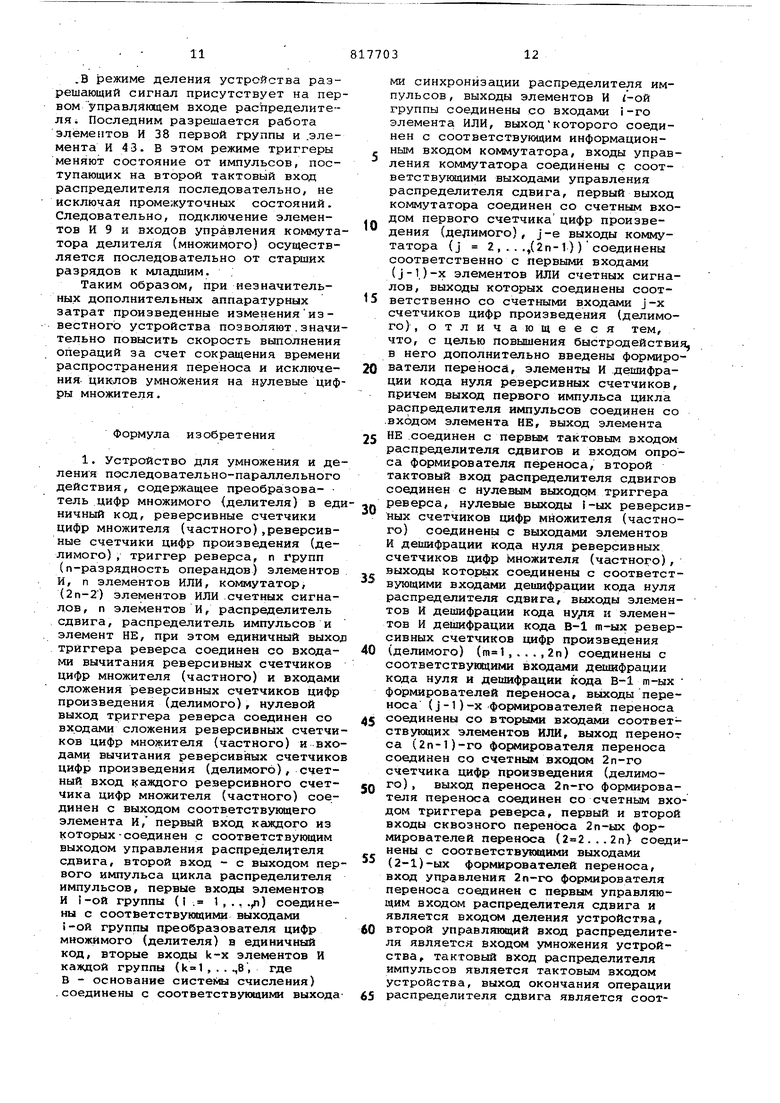

Исходное состояние всех триггеров распределителя нулевое. В режиме умножения разрешающий сигнал присутствует на шине 22. Этим сигналом разрешается работа элементов И 39 второй группы и элемента И 42 (тактовыми

0 являются каждый первый проинвертированный импульс распределителя 11). Первый триггер готов к переключению первым же та товым импульсом. Переключение каждого триггера следукяцего

5 разряда разрешается по соответствующему входу дешифрации нуля распределителя, подключенному к выходу дешифрации нуля соответствующего счетчика 2, и выходу элемента И.39 предьщу0щего разряда. Таким образом, переключение триггера каждого разряда зависит от содержимого всех предшествующих разрядов счетчика 2. Переключение одного (или одновременно нескольких

5 триггеров) происходит в том случае, когда содержимое предшествующего разряда (или предшествующих разрядов) счетчика 3 равно нулю. Тем самым исключается перемножение множимого на нулевые значения множителя. Дешиф-.

0 рация сигналов на выходах управления распределителя для i-ого разряда осуществляется группой двухвходовых элементов И 40 соглас.но уравнения

V О - .( N 1 Jii-n .В режиме деления устройства разрешающий сигнал присутствует на пер вом управляющем входе расЬределите-ляi Последним разрешается работа элементов И 38 первой группы и .элемента И 4 3. В этом режиме триггеры меняют состояние от импульсов, поступающих на второй тактовый вход распределителя последовательно, не исключая промежуточных состояний. Следовательно, подключение элементов И 9 и входов управления коммута тора делителя (множимого) осуществляется последовательно от старших разрядов к младшим. Таким образом, при незначительных дополнительных аппаратурных затрат произведенные измененияизвестного устройства позволяют.значи тельно повысить скорость выполнения операций за счет сокращения времени распространения переноса и исключения циклов умножения на нулевые циф ры множителя. Формула изобретения 1. Устройство для умножения и де ления последовательно-параллельного действия, содержащее преобра зова- тель цифр множимого {делителя) в ед ничный код, реверсивные счетчики цифр множителя (частного).реверсивные счетчики цифр произведения (делимого) , триггер реверса, п групп (п-разрядность операндов) элементов И, п элементов ИЛИ, коммутатор, (2п-2) элементов ИЛИ .счетных сигналов, п элементов И, распределитель сдвига, распределитель импульсов и элемент НЕ, при этом единичный выхо триггера реверса соединен со входами вычитания реверсивных счетчиков цифр множителя (частного) и входами сложения реверсивных счетчиков цифр произведения (делимого), нулевой выход триггера реверса соединен со входами сложения реверсивных счетчи ков цифр множителя (частного) и вхо дами вычитания реверсивных счетчико цифр произведения (делимого), счетный вход каждого реверсивного счетчика цифр множителя (частного) соединен с выходом соответствующего элемента И, первый вход каждого из которых-соединен с соответствующим выходом управления распределителя сдвига, второй вход - с выходом пер вого импульса цикла распределителя импульсов, первые входы элементов И i-ой группы (i . 1 , . , ./|) соедине ны с соответствующими выходами i-ой группы преобразователя цифр множимого (делителя) в единичный код, вторые входы k-x элементов И каждой группы (k 1 , . . .,8, где В - основание системы счисления) .соединены с соответствующими выход ми синхронизации распределителя импульсов, выходы элементов И i-ой группы соединены со входами i-ro элемента ИЛИ, выход которого соединен с соответствующим информационным входом коммутатора, входы управления коммутатора соединены с соответствующими выходами управления распределителя сдвига, первый выход коммутатора соединен со счетным входом первого счетчика цифр произведения (делимого), j-e выходы коммутатора (j 2 ,.. .,(2n-l) )соединены соответственно с первыми входами (j- 1)-X элементов ИЛИ счетных сигналов, выходы которых соединены соответственно со счетными входами j-x счетчиков цифр произведения (делимого), отличающееся тем, что, с целью повышения быстродействия, в него дополнительно введены формирователи переноса, элементы И дешифрации кода нуля реверсивных счетчиков, причем выход первого импульса цикла распределителя импульсов соединен со .входом элемента НЕ, выход элемента НЕ соединен с первым тактовым входом распределителя сдвигов и входом опроса формирователя переноса, второй тактовый вход распределителя сдвигов соединен с нулевь1М выходом триггера реверса, нулевые выходы i-ых реверсивных счетчиков цифр множителя (частного) соединены с выходами элементов И дешифрации кода нуля реверсивных счетчиков цифр множителя (частного), выходы которых соединены с соответствующими входами дешифрации кода нуля распределителя сдвига, выходы элементов И дешифрации кода ну/1я и элементов И дешифрации кода В-1 т-ых реверсивных счетчиков цифр произведения (делимого) (,...,2п) соединены с соответствукицими входами дешифрации кода нуля и дешифрации кода В-1 т-ых формирователей переноса, выходы переноса (j-l)-x формирователей переноса соединены со вторыми входами соответствугацих элементов ИЛИ, выход перенот са (2п-1)-го формирователя переноса соединен со счетным входе 2л-го счетчика цифр произведения (делимого) , выход переноса 2п-го формирователя переноса соединен со счетным входом триггера реверса, первый и второй входы сквозного переноса 2п-ых формирователей переноса (...2п) соединены с соответствующими выходами (2-1)-ых формирователей переноса, вход управления 2п-го формирователя переноса соединен с первым управляющим входом распределителя сдвига и является входом деления устройства, второй управлякнций вход распределителя является входом умножения устройства, тактовый вход распределителя импульсов является тактовым входом устройства, выход окончания операции распределителя сдвига является соответствующим выходом устройства, пря мой и инверсный ВЫХОДЫтриггера реверса соединены соответственно со входами сложения и вычитания формир вателей переноса, разрядные выходы т-ых реверсивных счетчиков цифр про изведения (делимого) соединены со входами соответствукядих элементов И дешифрации кода нуля и соответствую щих элементов И дешифрации кода В-1 2. Устройство по п. 1, отлич а ю щ е е с я тем, что каждый фор мирователь переноса содержит D-триггер переноса, четыре элемента И, четыре элемента ИЛИ и элемент НЕ, при этом выход первого элемента И соединен с первым входом первого элемента ИЛИ и является первым выходом сквозного переноса формирователя переноса единичный выход D-триггера соединен со вторым входом первого элемента ИЛ и является вторым выходом сквозного переноса формирователя переноса,, выход первого элемента ИЛИ соединен с первым входом второго элемента И, второй и третий входы которого являются соответственно входом опроса и входом управления формирователя переноса, выход второго элемента И является выходом переноса формирователя переноса и соединен с первым входом второго.элемента ИЛИ, выход которого соединен со входом элемента НЕ, выход элемента НЕ соедине со входом синхронизации 0-триггера, нулевой выход которого соединен со своим информационным входом, первые входы третьего и четвертого элементо И являются соответственно входами вычитания и сложения формирователя переноса, вторые входы - входами дешифрации кода нуля и дешифрации кода В-1 формирователя, выходы третьего. и четвертого элементов И соединены со входами третьего элемента ИЛИ, первый и второй входы четвертого эле мента ИЛИ являются соответственно пе вым и вторым входами сквозного переноса формирователя, выход третьего элемента ИЛИ соединен с первым входом первого элемента И и вторым входом второго элемента ИЛИ, выход четвертого элемента ИЛИ соединен со вторым входом первого элемента И. 3. Устройство по п 1/ отличающееся тем, что распределитель сдвига содержит группу элементов ИЛИ, три группы элементов И, элемент ИЛИ, два элемента И и п + 1 D-триггеров, при этом первые входы первого и второго элементов И являются соответственно первым и вторым тактовыми входами распределителя,выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен со входами синхронизации О-триггеров, единичные выходы триггеров соединены с первыми входами соответ- . ствующйх элементов И первой группы, вторые входы которых соединены со вторым входом второго элемента И и являются первым управля{адим входом распределителя, выходы Г-ых элементов И первой группы соединены соответственно с первыми входами элементов ИЛИ группы, выходы -ыУ. элементов ИЛИ группы соединены соответственно с информационными входами (-ых D-триггеров ( tf 2 ,... п+i ) .первые входы i-ых элементов И второй группы соединены со вторым входом цервого элемента И и являются вторым управляющим входом распределителя сдвигов, вторые входы - с соответствующими входами дешифрации кода нуля распределителя сдвига, выходы - со вторыми входами соответствукндих элементов ИЛИ группы, выходы (р -ых элементов И второй группы (Ц 1,...п-1) соединены соответственно с третьими входами (ср+ 1)-ых элементов И второй группы, первые входы i-ых элементов И третьей группы соединены с единичными выходами соответствующих О-триггеров, а вторые входыср-ых элемедтов И соединены соответственно с нулевыми выходами vCp + 1)-X -О-триггеров, нулевой выход первого D-триггера соединен со вторым входом п-го элемента И третьей группы, выходы элементов И третьей группы являются выходами управления распределителей сдвига,выход (п+))-го D-триггера является выходом окончания операции распределителя сдвига, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 190658, кл. G 06 F 7/52, 1966. 2.Авторское свидетельство СССР № 217718, кл. G 06 F 7/08, 1965 (прототип) ,

U

П

0

7J

/5

гз

/tf

r/f

/ff

/5

. 5

/7

т

н«кз

25

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Устройство для умножения | 1978 |

|

SU771669A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

5 б

Sb

to и- Г-, le uiiB 6 It и Id f tfjfffff

Авторы

Даты

1981-03-30—Публикация

1979-05-10—Подача