(54) ДЕШИФРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичногоКОдА B КОд ВОСьМиСЕгМЕНТНОгОиНдиКАТОРА | 1979 |

|

SU822172A1 |

| Преобразователь двоично-десятичногоКОдА B КОд СЕМиСЕгМЕНТНОгО иНдиКАТОРА | 1978 |

|

SU796836A1 |

| Дешифратор | 1986 |

|

SU1361724A1 |

| Преобразователь двоично-десятичного кода в код восьмисегментного индикатора | 1983 |

|

SU1130857A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1999 |

|

RU2168763C2 |

| Ассоциативный запоминающий элемент | 1982 |

|

SU1057988A1 |

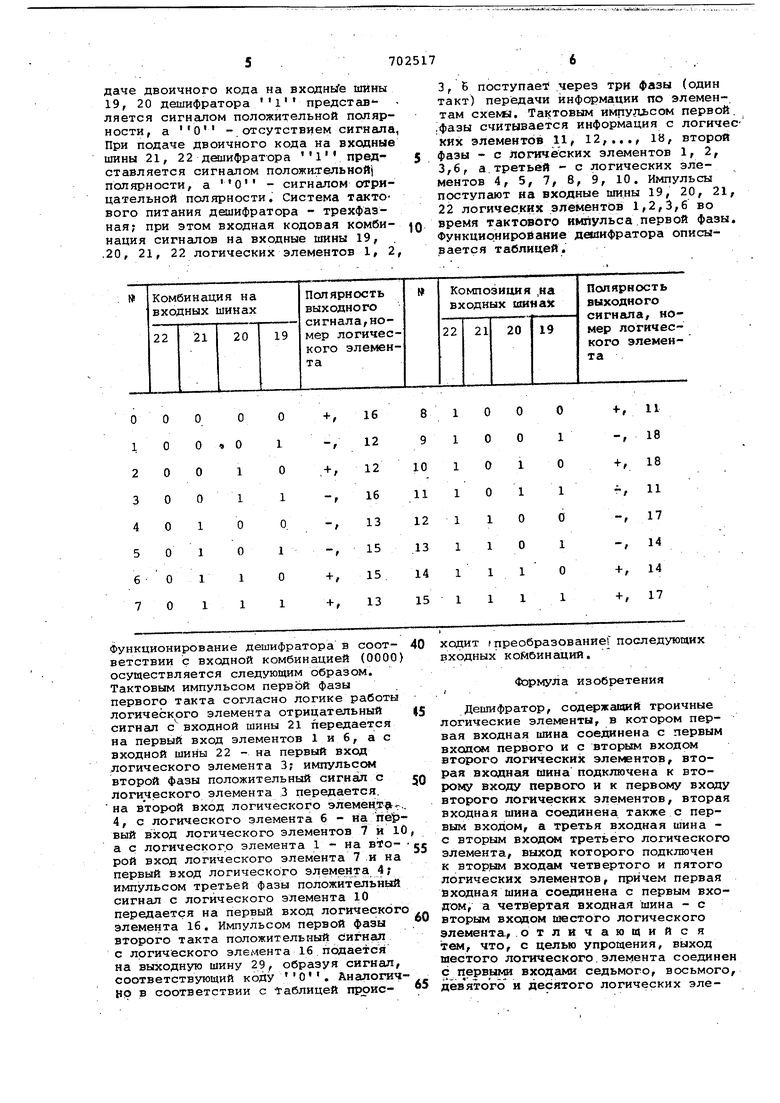

Иэобретение относится к области автоматики и вычислительной техники Известны дешифраторыji содержащие троичные логические элементы, в кот рых первая входная шина соединена с первым входом первого и с вторым входом.второго логических элементов а вторая вхбдная шина - с вторым входом первого и с первым входом второго логических элементов 1 . К недостаткам известного стройст за относится сложность конструдшзд, .Известен также дешифратор/ содержащий троичные логические эле- менты, в котором первая входная шина соединена с первым входом первого и с вторым входом второго логических элементов, а вторая входная шина подключена к второму входу первого и к первому входу второго логических элементов,- вторая входная шина соединена,также с первым входом, а третьявходная шина - с вторым входом третьего логического элемента, выход которого подк,шочен к вторым входс1м четвертого и пятого логичесКих элементов, причем первая входная шина соединена с первым входом, а четвертая входная шина - свторым входом шестого логического элемента 2. К недостаткам известного устройства относится также сложность конструкции. Целью изобретения является упроЬцение дшиифратора. Для этого в дешифраторе, содержащем троичные логические элементы, в котором первая входная шина соединена с первым входом первого и с BTOtisiM нхххцрм второго логических элементов,; вторая входная шина подключена к второму входу первого и к .первому входу второго логически элементов, вторая входная шина соединена также с первым входом, а третья входная шина, - с вторым входом третьего логического элемента, выход которого подключен к вторьгм входам четвертого и пятого логических элементов, причем первая входная ьшна соединена с первым входом, а четвертая входная шина - с вторым входом шестого логического элемента, выход шестого логического элемента сбёданен с первыми входами седьмого, восьмого, девятого и десятого логических элементов,выход первого логического элемента подключен к первым

входам четвертого, пятого и к вторым входам седьмого и восьмого логиг ческих элементов, выход второго логического элемента соединен с вторыми входами девятого и Десятого логических элементов, выход седьмого логического элемента соединен с первыми входами одиннадцатого и две- надцатого логических элементов, выход восьмого логического элемента с первым входом тринадцатого и с вторым входом четырнадцатог о логических элементов, выход четвертого логического элемента подключен к первому входу пятнадцатого и к вторым входам двенадцатого, тринадцатого и шестнадцатого логических элементов, выход пятого логического элемента соединен с первым входом четырнадцатого и с вторыми входами одиннадцатого, семнадцатого и восемнадцатого логических элементов, выход девятого логического элемента подключен к первому входу семнадцатого и к второму входу пятнадцатого логических элементов, выход десятогб логического элемента соединен q.первыми входами шестнадцатого и восемнадцатого ;лoгичecкйk э тементов, причеМ выходы Логических элементов с одиннадцатого по восем |надцатый включительно .образуют выхЪдйые .шины даиифратора.

Структурная электрическая схема дешифратйра представлена на чертеже

Устройство содержит следующие элементы: 1, 2,..,, 18 - троичные логические элементы; 19, 20, 21, 22 входные шины; 23, 24,..., 30 - выходные шины. Входная шина 19 соединена с первым входом и с вторым входом соответственно логических элементов 1 и 2. Входная шина 20 подключена к второму входу и к первому входу

На входные иины 19, 20, 21, 22 даиифратора подаются кодовые комбинации в двоичной форме (по входной. шине 19 с естественным весом 2, по входной шине 20 - 2, по входной шине 21-2,по входной шине 22-2),

соответственно логических элементов

Iи 2. Входная шина 20 соединена также с первым входом, а входная шина

21 - с вторым входом логического элемента 3, выход которого подключен ко 5 вторым входам логических элементов 4 и 5. Входная шина 19 соединена с первым входом, а четвертая входная шина 22 - с вторым входом логического элемента 6, выход которого соеQ динен с первыми входами логических элементов 7, 8, 9, 10. Выход логи- . .ческого элемента 1 подк.гаочен к первым входам логических элементов 4 и 5 к вторым-входам логических элементов 7 и 8. Выход логического элемента 2 соединен со вторыми входами логических элементов 9 и 10. Выход логического элемента 7 соединен с первыми входами логических элементов

IIи 12. Выход логического элемента 8 соединен с первым входом логического элемента 13 и с вторым входом логического элемента 14. Выхой логического элемента 4 подключен к первому входу и к вторым входам- соответственно логических элементов 15, и 12, 13, 16. Выход логического элемента 5 соединен с первым входом и. с вторйми входами соответственно логических элементов 14 и 11, 17, 18.

0 Выход логического элемента 9 подк™чен к первому входу и к второму входу соответственно логических элементов 17 и 15. Выход логического элемента 10 соединен с- первыми входа5 ми логических элементов 16 и 18. Выхсяы логических элементов с 11 по 18 включительно образуют выходные шины с 23 по 30.

Дешифр ат ор.р аб от ает еледующим

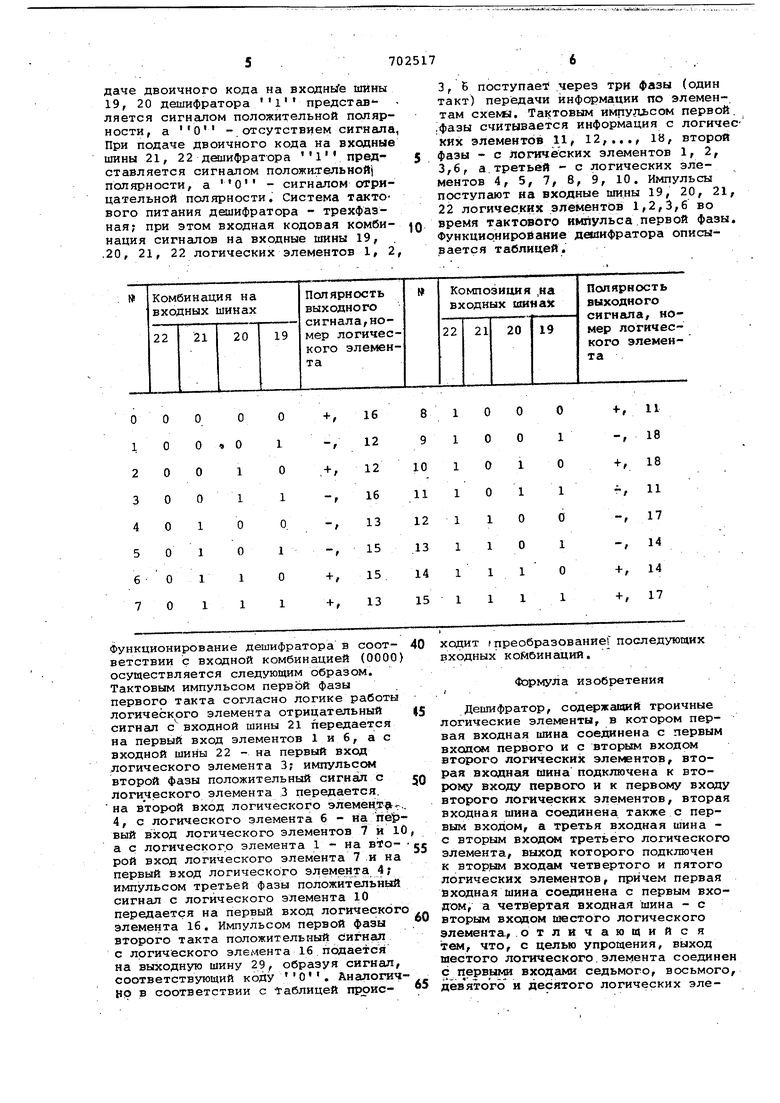

0 образом. Каждый логический элемент 1,2,..,, 18 реализует троичные операции, опи -:ываемые таблицей-.

при этом на одном из выходов :трбичных логических элементов 11, 12,..., 18 появляется сигнал положительной или отрицательной полярности, однозначно соответствуюи1ий входной комбинации сигналов. При подаче двоичного кода на входнь е шины 19, 20 дешифратора Ч представ ляется сигналом положительной полярности, а О - отсутствием сигнала При подаче двоичного кода на входные шины 21, 22 дешифратора 1 представляется сигналом положи.тельной| полярности, а О - сигналом отрицательной полярности. Система тактового питания дешифратора - трехфазная при этом входная кодовая комбинация сигналов на входные шины 19, .20, 21, 22 логических элементов 1, 2 функционирование дешифратора в соответствии с входной комбинацией (0000 осуществляется следующим образом. Тактовым импульсом первой фазы первого такта согласно логике работы логического элемента отрицательный сигнал с входной шины 21 передается на первый вход элементов 1 и 6, ас входной шины 22 - на первый вход логического элемента 3; импульсом второй фазы положительный сигнал с Логического элемента 3 передается, на второй вход логического элемент -4, с логического элемента 6 - на вход логического элементов 7 и 10 а с логического элемента 1 - на втророй вход логического элемента 7 .и на первый вход логического элемента 4; импульсом третьей фазы положительный сигнал с логического элемента 10 передается на первый вход логического элемента 16. Импульсом первой фазы второго такта положительный сигнал с логического элемента 16.подается на выходную шину 29, образуя сигнал, соответствующий коду О . АналогичНО в соответствии с -таблицей пррис 3, S поступает .через три фазы (один такт) передачи информации по элементам схема. Тактовым импудьсом первой. ;фазы считывается информация с логических элементов 11, 12,..., 18, второй фазы - с ЛогичёЪких элементов 1, 2, 3,6, а.третьей - с логических элементов 4, 5, 1, 8, 9, 10. Импульсы поступают на входные шины 19, 20, 21, 22 логических элементов 1,2,3,6 во время тактового импульса первой фазы. Функционирование дешифратора описывается таблицей. ходит преобразованиеГпоследующих входных комбинаций. Формула изобретения ; Дешифратор, содержасций троичные логические элементы, в котором первая входная шина соединена с первым входом первого и с вторым входом второго логических элементов, вторая входная шина подключена к второму входу первого и к первс у входу второго логических элементов, вторая входная шина соединена также с первым входом, а третья входная шина с вторым входом третьего логического элемента, выход которого подключен к вторым входам четвертого и пятого логических элементов, причем первая входная шина соединена с первым входом, а четвертая входная шина - с вторым входом шестого логического элемента, отличающийся тем, что, с целью упрощения, выход естого логического.элемента соединен входами седьмого, восьмого, евятого и десятого логических элементов, выход первого логического элемента подключен к первым входам четвертого, пятого, и к вторым входам седьмого и восьмого логических элементов, выход второго логического элемента соединен с вторыми входами девятого и десятого логических элементов, выход седьмого логического йШяёНга сЬедйнен с первыми входами одиннадцатого и двенадцатого логических элементов, выход восьмого логического элемента - с первым входом тринадцатого и с вторым входом четырнадцатого логических элементов, вйхЪд четйертого логического элемент подключен к первому входу пятнадцато,го и к вторым входам двенадцатого .тринадцатого и шестнадцатого Логических элементов, выход пятого логического элемент а соединен с первыми Входами четырнадцатого и с вторыми

7

702 517входами одиннадцатого,семнадцатого и восемнадцатого логических элементов, выход девятого логического элемента подключен к первому входу семнадцатого и к второму входу пятнадцатого логических элементов, выход десятого логического элемента соединен с первыг-т входами шестнадцатого и восемнадцатого логических элементов, причем выходы логических Q элементов с одиннадцатого По восемнадцатый включительно образуют выходные шины дешифратора.

Источники информации, принятые во .внимание при экспертизе

.1. Авторское свидетельство СССР №483785, КЛ. Н 03 К 13/247, 05.09.75.. 2. Кузнецов В.Ф. ii др. Ферритовые логические элементы, М., Энергия, 71975, с.89-91, рис.3-35.;

11

Авторы

Даты

1979-12-05—Публикация

1977-01-05—Подача