Изобретение относится к цифровой технике и может быть использовано для вычисления логических функций суммы и переноса одноразрядного двоичного сумматора.

Аналогами заявляемого устройства являются: логическая схема и полный сумматор (Европейский патент № ЕР 1111791 А1, кл. H01K 19/21, G06F 7/50, дата публикации 27.06.2001), схема 1-битного сумматора с малым напряжением питания, низкой потребляемой мощностью и высоким быстродействием на основе комплементарных металл-оксид-полупроводник (КМОП) транзисторов (патент Китая № CN 1567722A, кл. H03K 19/0948, H03K 19/20, дата публикации 19.01.2005), сумматор (патент Российской Федерации № RU 2380739 C1, кл. G06F 7/50, дата публикации 27.01.2010), одноразрядный сумматор (патент Российской Федерации № RU 2408058 C2, кл. G06F 7/50, дата публикации 27.12.2010), одноразрядный двоичный сумматор (патент Российской Федерации № RU 2408922 C1, кл. G06F 7/50, дата публикации 10.01.2011). Недостатком патентов ЕР 1111791 А1 и CN 1567722 A является низкая нагрузочная способность сумматоров, обусловленная отсутствием буферных элементов на выходах схем. В сумматорах, представленных патентами RU2380739C1, RU 2408058 C2 и RU 2408922 C1, цепь формирования сигнала суммы является нагрузкой для цепи формирования сигнала переноса, что ограничивает быстродействие схем.

Ближайшим прототипом заявляемого устройства является одноразрядный двоичный КМОП сумматор (Zimmermann R., Fichtner W. "Low-power logic styles: CMOS versus pass-transistor logic," IEEE Journal of Solid-State Circuits, 1997, vol. 32, issue 7, pp.1085, fig.4(p)). Схема содержит двадцать восемь транзисторов, с первого по пятый, одиннадцатый, тринадцатый, четырнадцатый, семнадцатый, девятнадцатый, двадцатый, двадцать третий, двадцать пятый, двадцать седьмой металл-оксид-полупроводник (МОП) транзисторы с каналом р-типа, подложки которых подключены к положительной шине питания, и с шестого по десятый, двенадцатый, пятнадцатый, шестнадцатый, восемнадцатый, двадцать первый, двадцать второй, двадцать четвертый, двадцать шестой, двадцать восьмой МОП транзисторы с каналом n-типа, подложки которых подключены к земляной шине питания, входной сигнал А подается на затворы первого, третьего, восьмого, десятого, тринадцатого, пятнадцатого, девятнадцатого и двадцать второго транзисторов, входной сигнал В подается на затворы второго, пятого, седьмого, девятого, четырнадцатого, шестнадцатого, двадцать седьмого и двадцать восьмого транзисторов, входной сигнал С подается на затворы четвертого, шестого, семнадцатого, восемнадцатого, двадцатого и двадцать первого транзисторов, истоки первого, второго, третьего, одиннадцатого, тринадцатого, четырнадцатого, семнадцатого, девятнадцатого и двадцать третьего транзисторов подключены к положительной шине питания, истоки восьмого, девятого, десятого, двенадцатого, пятнадцатого, шестнадцатого, восемнадцатого, двадцать второго и двадцать четвертого транзисторов подключены к земляной шине питания, стоки транзисторов с четвертого по седьмой соединены с затворами одиннадцатого, двенадцатого, двадцать пятого и двадцать шестого транзисторов, соединение стоков одиннадцатого и двенадцатого транзисторов является выходом сигнала переноса СО, стоки двадцатого, двадцать первого, двадцать пятого и двадцать шестого транзисторов соединены с затворами двадцать третьего и двадцать четвертого транзисторов, соединение стоков двадцать третьего и двадцать четвертого транзисторов является выходом сигнала суммы S, стоки первого и второго транзисторов соединены с истоком четвертого, сток третьего транзистора соединен с истоком пятого, стоки восьмого и девятого транзисторов соединены с истоком шестого, сток десятого транзистора соединен с истоком седьмого, стоки тринадцатого, четырнадцатого и семнадцатого транзисторов соединен с истоком двадцать пятого, стоки пятнадцатого, шестнадцатого и восемнадцатого транзисторов соединены с истоком двадцать шестого, сток девятнадцатого транзистора соединен с истоком двадцать седьмого транзистора, сток которого соединен с истоком двадцатого транзистора, сток двадцать второго транзистора соединен с истоком двадцать восьмого транзистора, сток которого соединен с истоком двадцать первого транзистора.

Недостаток известных схем одноразрядных двоичных сумматоров, в том числе и прототипа, заключается в значительных временах задержек формирования выходных сигналов суммы и переноса. Задача предлагаемого изобретения - уменьшение времен задержек формирования выходных сигналов одноразрядного двоичного сумматора.

Решение поставленной задачи достигается тем, что предлагаемая схема одноразрядного двоичного КМОП сумматора содержит двадцать четыре транзистора, с первого по пятый, одиннадцатый, тринадцатый, четырнадцатый, семнадцатый, девятнадцатый, двадцатый, двадцать третий МОП транзисторы с каналом р-типа и с шестого по десятый, двенадцатый, пятнадцатый, шестнадцатый, восемнадцатый, двадцать первый, двадцать второй, двадцать четвертый МОП транзисторы с каналом n-типа подложки с первого по третий, одиннадцатого, тринадцатого, семнадцатого, девятнадцатого, двадцать третьего транзисторов и истоки с первого по третий, одиннадцатого, тринадцатого, семнадцатого, девятнадцатого, двадцать третьего транзисторов подключены к положительной шине питания, подложки с восьмого по десятый, двенадцатого, пятнадцатого, шестнадцатого, восемнадцатого, двадцать первого, двадцать второго, двадцать четвертого транзисторов и истоки с восьмого по десятый, двенадцатого, восемнадцатого, двадцать четвертого транзисторов подключены к земляной шине питания, входной сигнал А подается на затворы первого, третьего, восьмого, десятого, тринадцатого и пятнадцатого транзисторов, входной сигнал В подается на затворы второго, пятого, седьмого, девятого, четырнадцатого и шестнадцатого транзисторов, входной сигнал С подается на затворы четвертого, шестого, двадцатого и двадцать первого транзисторов, стоки транзисторов с четвертого по седьмой соединены с затворами одиннадцатого и двенадцатого транзисторов, соединение стоков одиннадцатого и двенадцатого транзисторов является выходом сигнала переноса СО, соединение стоков двадцать третьего и двадцать четвертого транзисторов является выходом сигнала суммы S, в отличие от прототипа, схема не содержит двадцать пятого, двадцать шестого МОП транзисторов с каналом р-типа и двадцать седьмого, двадцать восьмого МОП транзисторов с каналом р-типа, входной сигнал А подается на исток шестнадцатого транзистора, входной сигнал В подается на исток пятнадцатого транзистора, входной сигнал С подается на исток двадцать второго транзистора, стоки первого и второго транзисторов соединены с истоком и подложкой четвертого, сток третьего транзистора соединен с истоком и подложкой пятого, стоки восьмого и девятого транзисторов соединены с истоком и подложкой шестого, сток десятого транзистора соединен с истоком и подложкой седьмого, сток тринадцатого транзистора соединен с истоком и подложкой четырнадцатого, сток девятнадцатого транзистора соединен с истоком и подложкой двадцатого транзистора, стоки транзисторов с четырнадцатого по шестнадцатый соединены с затворами семнадцатого и восемнадцатого транзисторов, стоки семнадцатого и восемнадцатого транзисторов соединены с истоком двадцать первого и затворами девятнадцатого и двадцать второго транзисторов, стоки транзисторов с двадцатого по двадцать второй соединены с затворами двадцать третьего и двадцать четвертого транзисторов.

За счет схемотехнического решения с организацией параллельной работы цепей формирования выходных сигналов суммы и переноса, уменьшением числа транзисторов и исключением ряда паразитных емкостей путем соединения стоков и подложек транзисторов в предложенном одноразрядном двоичном КМОП сумматоре достигается уменьшение времен задержек формирования сигналов суммы и переноса.

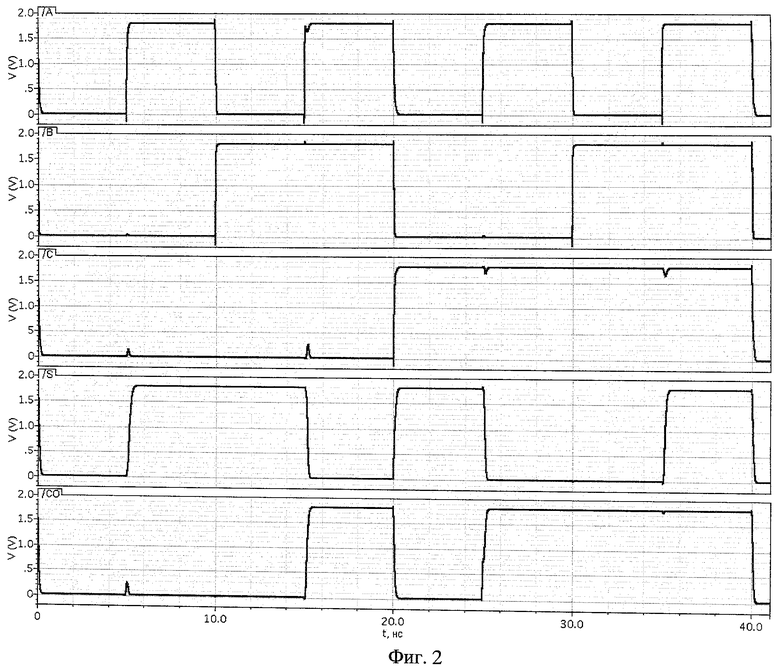

Предлагаемое изобретение иллюстрируется графическими материалами, представленными на фиг.1 и 2:

на фиг.1 изображена схема одноразрядного двоичного КМОП сумматора;

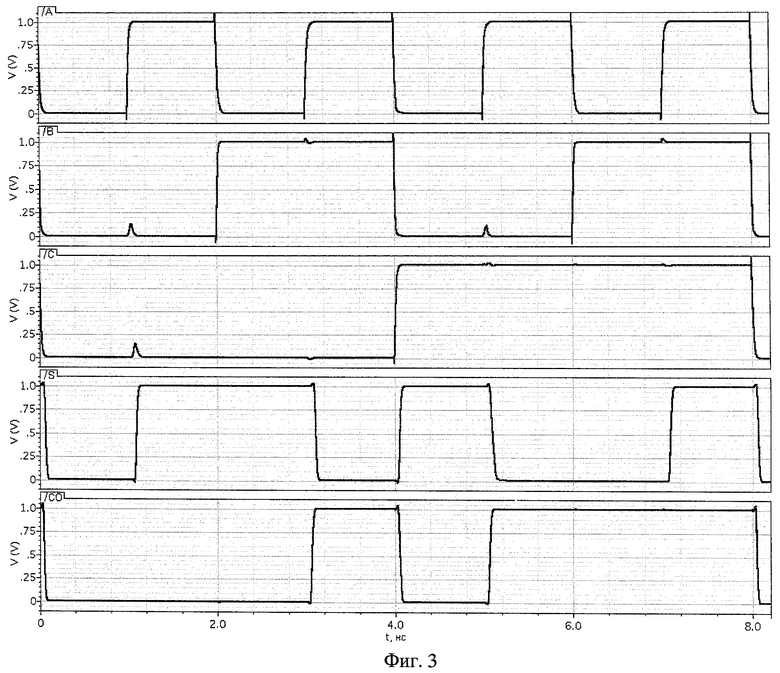

на фиг.2 приведены результаты моделирования одноразрядного двоичного КМОП сумматора во временной области для 180 нм МОП технологии при напряжении питания 1,8 В;

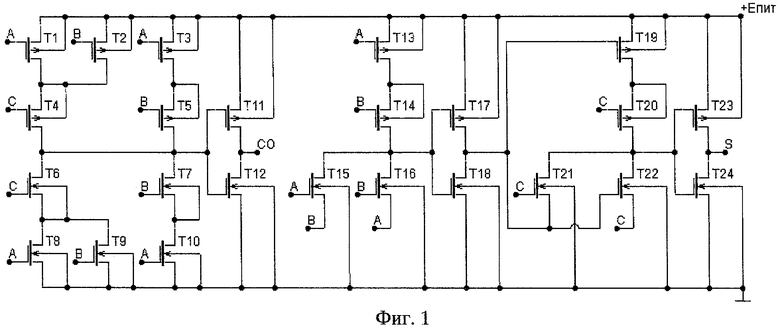

на фиг.3 приведены результаты моделирования одноразрядного двоичного КМОП сумматора во временной области для 90 нм МОП технологии при напряжении питания 1,0 В.

Заявляемый одноразрядный двоичный КМОП сумматор (фиг.1) состоит из отдельных цепей формирования выходных сигналов суммы S и переноса СО. Цепь формирования сигнала суммы реализована на транзисторах Т1-Т12, а цепь формирования сигнала цепи переноса реализована на транзисторах Т13-Т24. Для обеспечения уменьшения времени задержки формирования сигнала переноса сделано следующее. Во-первых, сигнал из цепи переноса не используется для формирования сигнала суммы, что уменьшает емкостную нагрузку в узле, где соединяются стоки транзисторов Т4-Т7 и затворы транзисторов Т11 и Т12. Во-вторых, подложки транзисторов Т4-Т7 отключены от шин источника питания и соединены с истоками этих транзисторов, что позволило исключить паразитные емкости исток-подложка. Уменьшение времени задержки формирования сигнала суммы обеспечивается схемотехническим решением, не требующим сформированного сигнала переноса и состоящим из последовательного соединения двух ячеек исключающего ИЛИ - первой на транзисторах Т13-Т18 и второй на транзисторах Т19-Т24.

Схема работает согласно таблице истинности, представленной в таблице 1. При воздействии на схему первой комбинации входных сигналов транзисторы Т1-Т5, Т13, Т14 работают в линейном режиме, а транзисторы Т6-Т10, Т15, Т16 - в режиме отсечки. На входах инверторов на транзисторах T11, T12 и Т17, Т18 оказывается напряжение положительной шины питания, а на выходах инверторов - напряжение земляной шины питания. Напряжение на выходе цепи переноса СО соответствует логическому нулю. Транзисторы Т19, Т20 работают в линейном режиме, а транзисторы Т21, Т22 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания, что соответствует логическому нулю на выходе цепи суммы S.

При воздействии на схему второй комбинации входных сигналов транзисторы Т1-Т3, Т5, Т6, Т13, Т14 работают в линейном режиме, а транзисторы Т4, Т7-Т10, Т15, Т16 - в режиме отсечки. На входах инверторов на транзисторах Т11, T12 и Т17, Т18 оказывается напряжение положительной шины питания, а на выходах инверторов - напряжение земляной шины питания. Напряжение на выходе цепи переноса СО соответствует логическому нулю. Транзисторы Т19, Т21 работают в линейном режиме, а транзисторы Т20, Т22 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи суммы S.

При воздействии на схему третьей комбинации входных сигналов транзисторы Т1, Т3, Т4, Т9, Т13, Т16 работают в линейном режиме, а транзисторы Т2, Т5, Т6, Т8, Т10, Т14, Т15 - в режиме отсечки. На входе инвертора на транзисторах Т11, Т12 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания, что соответствует логическому нулю на выходе цепи переноса СО. На входе инвертора на транзисторах Т17, Т18 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания. Транзистор Т22 работает в линейном режиме, а транзисторы Т19, Т21 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи суммы S.

При воздействии на схему четвертой комбинации входных сигналов транзисторы Т1, Т3, Т6, Т9, Т13, Т16 работают в линейном режиме, а транзисторы Т2, Т4, Т5, Т8, Т10, Т14, Т15 - в режиме отсечки. На входе инвертора на транзисторах Т11, Т12 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи переноса СО. На входе инвертора на транзисторах Т17, Т18 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания. Транзисторы Т21, Т22 работают в режиме близком к линейному, а транзисторы Т19, Т20 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания, что соответствует логическому нулю на выходе цепи суммы S.

При воздействии на схему пятой комбинации входных сигналов транзисторы Т2, Т4, Т8, Т10, Т15 работают в линейном режиме, а транзисторы Т1, Т3, Т6, Т7, Т9, Т13, Т16 - в режиме отсечки. На входе инвертора на транзисторах Т11, Т12 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания, что соответствует логическому нулю на выходе цепи переноса СО. На входе инвертора на транзисторах Т17, Т18 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания. Транзистор Т22 работает в линейном режиме, а транзисторы Т19, Т21 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи суммы S.

При воздействии на схему шестой комбинации входных сигналов транзисторы Т2, Т6, Т8, Т10, Т15 работают в линейном режиме, а транзисторы Т1, Т3, Т4, Т7, Т9, Т13, Т16 - в режиме отсечки. На входе инвертора на транзисторах T11, T12 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи переноса СО. На входе инвертора на транзисторах Т17, Т18 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания. Транзисторы Т21, Т22 работают в режиме близком к линейному, а транзисторы Т19, Т20 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания, что соответствует логическому нулю на выходе цепи суммы S.

При воздействии на схему седьмой комбинации входных сигналов транзисторы Т7-Т10, Т15 работают в линейном режиме, транзисторы Т15, Т16 работают в режиме, близком к линейному, а транзисторы Т1-Т3, Т5, Т6, Т13, Т14 - в режиме отсечки. На входе инвертора на транзисторах T11, T12 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи переноса СО. На входе инвертора на транзисторах Т17, Т18 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания. Транзисторы Т19, Т20 работают в линейном режиме, а транзисторы Т21, Т22 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания, что соответствует логическому нулю на выходе цепи суммы S.

При воздействии на схему восьмой комбинации входных сигналов транзисторы Т6-Т10 работают в линейном режиме, транзисторы Т15, Т16 работают в режиме, близком к линейному, а транзисторы Т1-Т5, Т13, Т14 - в режиме отсечки. На входе инвертора на транзисторах Т11, Т12 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной тины питания, что соответствует логической единице на выходе цепи переноса СО. На входе инвертора на транзисторах Т17, Т18 оказывается напряжение положительной шины питания, а на выходе инвертора - напряжение земляной шины питания. Транзисторы Т19, Т21 работают в линейном режиме, а транзисторы Т20, Т22 - в режиме отсечки. На входе инвертора на транзисторах Т23, Т24 оказывается напряжение земляной шины питания, а на выходе инвертора - напряжение положительной шины питания, что соответствует логической единице на выходе цепи суммы S.

Работоспособность устройства подтверждается результатами моделирования предложенной схемы одноразрядного двоичного КМОП сумматора. Моделирование проводилось с помощью программного обеспечения платформы Virtuoso IC5.1.41 компании Cadence Design Systems с использованием параметров 180 нм МОП технологии при напряжении питания 1,8 В и с использованием параметров 90 нм МОП технологии при напряжении питания 1,0 В. На фиг.2 и 3 приведены результаты моделирования одноразрядного двоичного КМОП сумматора во временной области. На графиках представлены входные сигналы А, В, С и выходные сигналы S, СО. Графики на фиг.2 и 3 соответствуют таблице истинности одноразрядного двоичного сумматора.

Для 180 нм МОП технологии с напряжением питания 1,8 В и 90 нм МОП технологии с напряжением питания 1,0 В в таблице 2 приведено сравнение средней работы переключения Аперекл. и средних времен задержек формирования выходных сигналов суммы tзд.S и переноса tзд.СО схем одноразрядных двоичных сумматоров:

- схема 1 - прототип из статьи Zinimermann R., Fichtner W. "Low-power logic styles: CMOS versus pass-transistor logic," IEEE Journal of Solid-State Circuits, 1997, vol.32, issue 7, pp.1085, fig. 4(p);

- схема 2 - аналог - патент Российской Федерации № RU 2380739 C1;

- схема 3 - аналог - патент Российской Федерации № RU 2408058 C2;

- схема 4 - аналог - патент Российской Федерации № RU 2408922 C1;

- схема 5 - предложенная схема одноразрядного двоичного КМОП сумматора.

Таким образом, результаты моделирования (фиг.2 и 3) подтверждают правильное функционирование схемы одноразрядного двоичного КМОП сумматора. Согласно таблице 2 по сравнению с аналогами и прототипом заявляемого устройства достигается уменьшение времен задержек формирования сигналов суммы и переноса. При этом значения средней работы переключения предложенной схемы и прототипа близки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2011 |

|

RU2450324C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2011 |

|

RU2444050C1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

| РЕГИСТР СДВИГА, СХЕМА УПРАВЛЕНИЯ ЗАТВОРОМ ПОЭТАПНОГО СДВИГА И ПАНЕЛЬ ОТОБРАЖЕНИЯ | 2014 |

|

RU2658887C1 |

Изобретение относится к цифровой технике Технический результат заключается в уменьшении времен задержек формирования выходных сигналов суммы и переноса одноразрядного двоичного сумматора. Схема сумматора состоит из работающих параллельно отдельных цепей формирования выходных сигналов суммы и переноса на основе комплементарных металл-оксид-полупроводник транзисторов. Для обеспечения уменьшения времени задержки формирования сигнала переноса сделано следующее. Во-первых, сигнал из цепи переноса не используется для формирования сигнала суммы, что уменьшает емкостную нагрузку цепи переноса. Во-вторых, подложки всех транзисторов в цепи переноса и транзисторов с каналом р-типа в цепи суммы соединены с истоками этих транзисторов, что позволило исключить паразитные емкости сток-подложка. Уменьшение времени задержки формирования сигнала суммы обеспечивается схемотехническим решением, не требующим сформированного сигнала переноса и состоящим из последовательного соединения двух ячеек исключающего ИЛИ. 3 ил., 2 табл.

Одноразрядный двоичный КМОП сумматор содержит с первого по пятый, одиннадцатый, тринадцатый, четырнадцатый, семнадцатый, девятнадцатый, двадцатый, двадцать третий МОП транзисторы с каналом р-типа и с шестого по десятый, двенадцатый, пятнадцатый, шестнадцатый, восемнадцатый, двадцать первый, двадцать второй, двадцать четвертый МОП транзисторы с каналом n-типа, подложки с первого по третий, одиннадцатого, тринадцатого, семнадцатого, девятнадцатого, двадцать третьего транзисторов и истоки с первого по третий, одиннадцатого, тринадцатого, семнадцатого, девятнадцатого, двадцать третьего транзисторов подключены к положительной шине питания, подложки с восьмого по десятый, двенадцатого, пятнадцатого, шестнадцатого, восемнадцатого, двадцать первого, двадцать второго, двадцать четвертого транзисторов и истоки с восьмого по десятый, двенадцатого, восемнадцатого, двадцать четвертого транзисторов подключены к земляной шине питания, входной сигнал А подается на затворы первого, третьего, восьмого, десятого, тринадцатого и пятнадцатого транзисторов, входной сигнал В подается на затворы второго, пятого, седьмого, девятого, четырнадцатого и шестнадцатого транзисторов, входной сигнал С подается на затворы четвертого, шестого, двадцатого и двадцать первого транзисторов, стоки транзисторов с четвертого по седьмой соединены с затворами одиннадцатого и двенадцатого транзисторов, соединение стоков одиннадцатого и двенадцатого транзисторов является выходом сигнала переноса СО, соединение стоков двадцать третьего и двадцать четвертого транзисторов является выходом сигнала суммы S, отличающийся тем, что входной сигнал А подается на исток шестнадцатого транзистора, входной сигнал В подается на исток пятнадцатого транзистора, входной сигнал С подается на исток двадцать второго транзистора, стоки первого и второго транзисторов соединены с истоком и подложкой четвертого, сток третьего транзистора соединен с истоком и подложкой пятого, стоки восьмого и девятого транзисторов соединены с истоком и подложкой шестого, сток десятого транзистора соединен с истоком и подложкой седьмого, сток тринадцатого транзистора соединен с истоком и подложкой четырнадцатого, сток девятнадцатого транзистора соединен с истоком и подложкой двадцатого транзистора, стоки транзисторов с четырнадцатого по шестнадцатый соединены с затворами семнадцатого и восемнадцатого транзисторов, стоки семнадцатого и восемнадцатого транзисторов соединены с истоком двадцать первого и затворами девятнадцатого и двадцать второго транзисторов, стоки транзисторов с двадцатого по двадцать второй соединены с затворами двадцать третьего и двадцать четвертого транзисторов.

| Комбинационный двоичный сумматор | 1990 |

|

SU1795453A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Одноразрядный двоичный сумматор | 1980 |

|

SU943712A1 |

| EP 1039372 A1, 27.09.2000. | |||

Авторы

Даты

2012-06-27—Публикация

2011-06-07—Подача