(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов наносекундной длительности | 1978 |

|

SU705659A1 |

| Устройство формирования импульсных последовательностей | 1973 |

|

SU507917A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 1972 |

|

SU432678A1 |

| -ГСО-ОЗНАЯ | 1973 |

|

SU369688A1 |

| Устройство для регулирования температуры | 1988 |

|

SU1594503A1 |

| Формирователь ступенчатых импульсов | 1973 |

|

SU494842A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВБИБЛ;10.: КЛ | 1972 |

|

SU350140A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Формирователь импульсов | 1981 |

|

SU984004A1 |

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

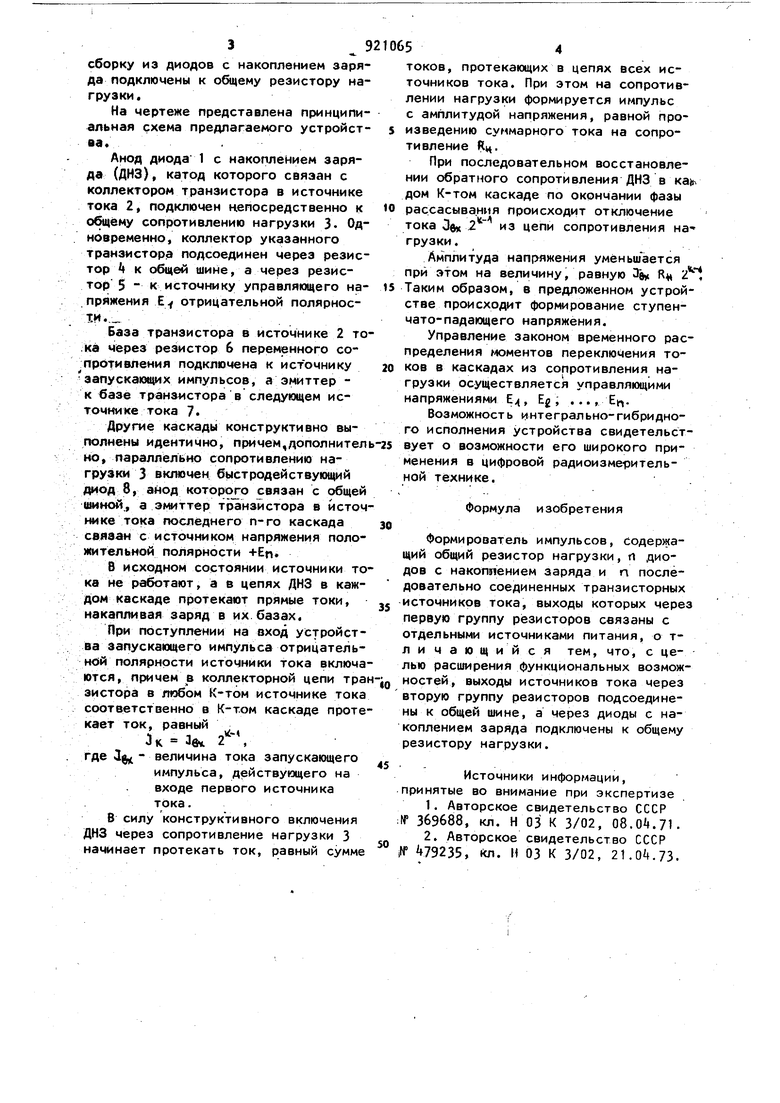

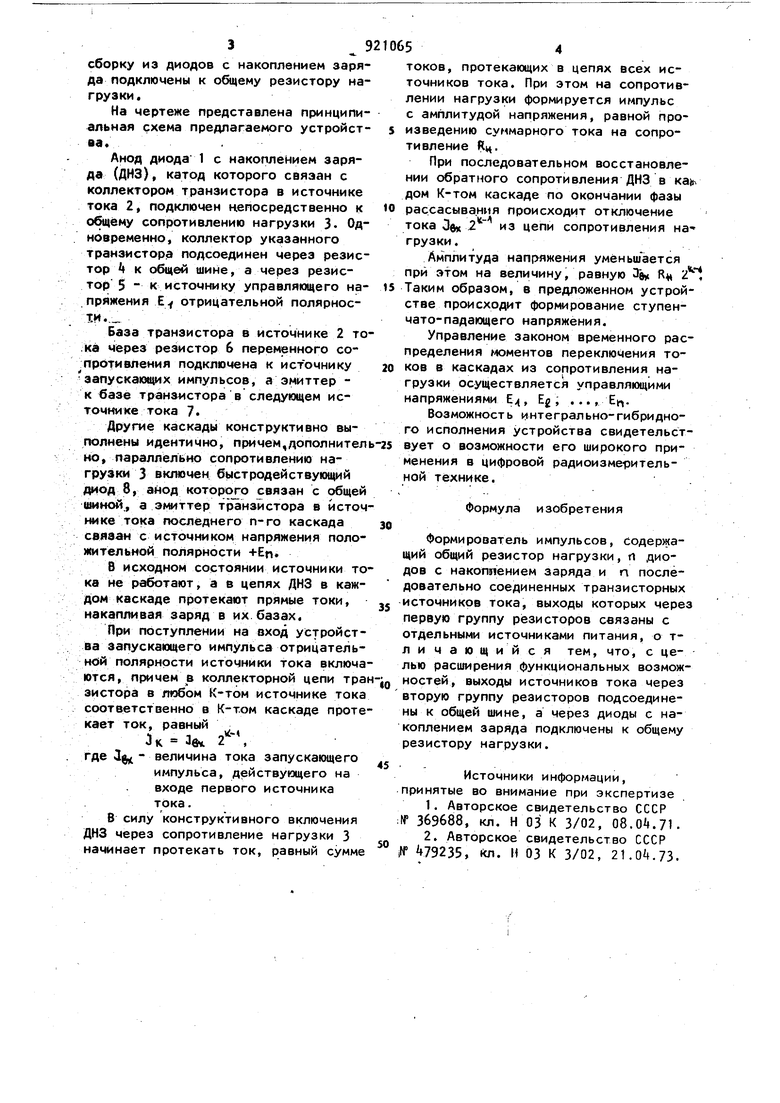

Изобретение относится к наносекун ной полупроводниковой импульсной тех нике и может найти применение в вычислительной и цифровой радиоизмерительной технике, устройствах моделирования и контроля систем передачи информации. Известно устройство, которое содержит п транзисторных каскадов и п диодов с накоплением заряда, причем с целью формирования имПульсов ступенчатого напряжения выходы транзисторных каскадов подключены через резисторы к общему сопротивлению нагрузки 1. Недостатком известного устройства является невозможностью формирова ния импульсов со ступенчатым задним фронтом. Известен также формирователь импульсов, который содержит общий резистор нагрузки, п диодов с накопле нием заряда и п последовательно соединенных транзисторных источников тока на составных транзисторах, в каждом из которых переход база - коллектор управляющего транзистора объединен, а коллектор выходного транзистора соединен через резистор с отдельным источником питания С23. Недостатком известной схемы является невозможность формирования на выходе импульсов со ступенчатым задним фронтом, т.е. низкие фрикционные возможности. Цель изобретения - расширение функциональных возможностей. Указанная цель достигается тем, что в фор ирователе импульсов, содержащем общий резистор нагрузки, п диодой с накоплением заряда и п последовательно соединенных транзисторных источников тока, выходы которых через первую группу резисторов связаны с отдельными источниками питания, выходы источников тока через вторую группу резисторов подсоединены к общей шине, а через диодную сборку из диодов с накоплением заряда подключены к общему резистору нагрузки. На чертеже представлена принципиальная схема предлагаемого устройст- ва, . . Анод диода 1 с накоплением заряда (ДНЗ), катод которого связан с коллектором транзистора в источнике тока 2, подключен непосредственно к общему сопротивлению нагрузки 3- Одновременно, коллектор указанного транзистору подсоединен через резистор t к общей шине, а через резистор 5 - к источнику управляющего напряжения Е отрицательной полярнос,ТИ., . , База транзистора в источнике 2 то ка 4iepe3 резистор 6 переменного сопротивления подключена к источнику запускающих импульсов, а эмиттер к базе транзистора в следующем источнике тока 7. Другие каскады конструктивно выполнены идентично, причем,дополнител но, параллельно сопротивлению нагрузки 3 включен быстродействующий диод 8, айод которого связан с общей шиной., а эмиттер транзистора в источ нике тока последнего п-го каскада связан с источником напряжения положительной полярности +ЕП. В исходном состоянии источники то ка не работают, а в цепях ДНЗ в кажД|ОМ каскаде протекают прямые токи, накапливая заряд в их.базах. При поступлении на вход устройства запускающего импульса отрицательной полярности источники тока включа ются, п(1чем в коллекторной цепи тра зистора в любом К-том источнике тока соответственно в К-том каскаде проте кает ток, равный S щ К Зв 2 , где J - величина тока запускающего импульса, действующего на входе первого источника тока. В силу конструктивного включения ДНЗ через сопротивление нагрузки 3 начинает протекать ток, равный сумме токов, протекающих в цепях всех источников тока. При этом на сопротивлении нагрузки формируется импульс с амплитудой напряжения, равной произведению суммарного тока на сопротивление Яц. При последовательном восстановлении обратного сопротивления ДНЗ в каь дом К-том каскаде по окончании фазы рассасывания происходит отключение тока Лох из цепи сопротивления на грузки. Амплитуда нап яжения уменьшается при этом на величину, равную 3 П , Таким образом, в предложенном устройстве происходит формирование ступенчато-падающего напряжения. Управление законом временного распределения юментов переключения токов в каскадах из сопротивления нагрузки осуществляется управляющими напряжениями Е, Eg, ..., Е Возможность интегрально-гибридного исполнения устройства свидетельствует о возможности его широкого применения в цифровой радиоизмерительной технике.. Формула изобретения Формирователь импульсов, содержащий общий резистор нагрузки, п диодов с накоплением заряда и п последовательно соединенных транзисторных источников тока, выходы которых через первую группу резисторов связаны с отдельными источниками питания, о тли чающийся тем, что, с целью расширения функциональных возможностей, выходы источников тока через вторую группу резисторов подсоединены к общей шине, а через диоды с накоплением заряда подключены к общему резистору нагрузки. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР :№ 369688, кл. Н 03 К 3/02, 08.0i.71. 2.Авторское свидетельство СССР i№ 79235, Кл. И 03 К 3/02, 21,04.73.

Авторы

Даты

1982-04-15—Публикация

1980-07-29—Подача