1

Изобретение относится к области импульсной техники и может быть применено в устройствах автоматики и вычислительной техники.

Известно устройство сортировки импульсов, в состав которого входит накопитель, а также один каскад, соединенный с накопителем с целью сортировки импульсов. В состав этого каскада входит ждущий мультивибратор. Скорость сортировки определяется характеристиками этого каскада, причем каскад не может сортировать следующий импульс до тех пор, пока мультивибратор не окажется в исходном состоянии. По меньшей мере один дополнительный каскад соединен с накопителем, причем вход дополнительного каскада соединен последовательно с первым каскадом для приема упомянутых импульсов после того, как они приняты первым каскадом и для сортировки всех тех входных импульсов, которые не отсортированы первым каскадом. В состав каждого дополнительного каскада входит ключевая схема и ждуишй мультивибратор, соединенный с этой схемой. Требуемое число каскадов зависит от скорости и распределения входаых импульсов относительно характеристик разрешающей способности каскадов 1.

Недостатком известного устройства является его сложность.

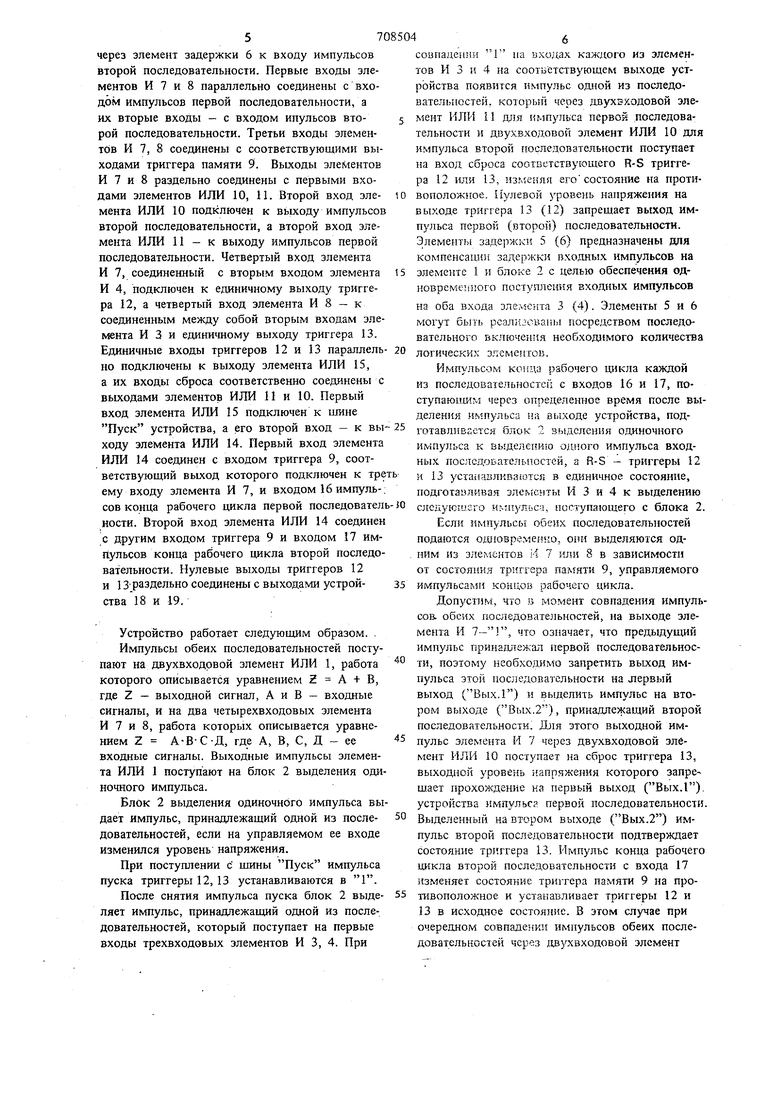

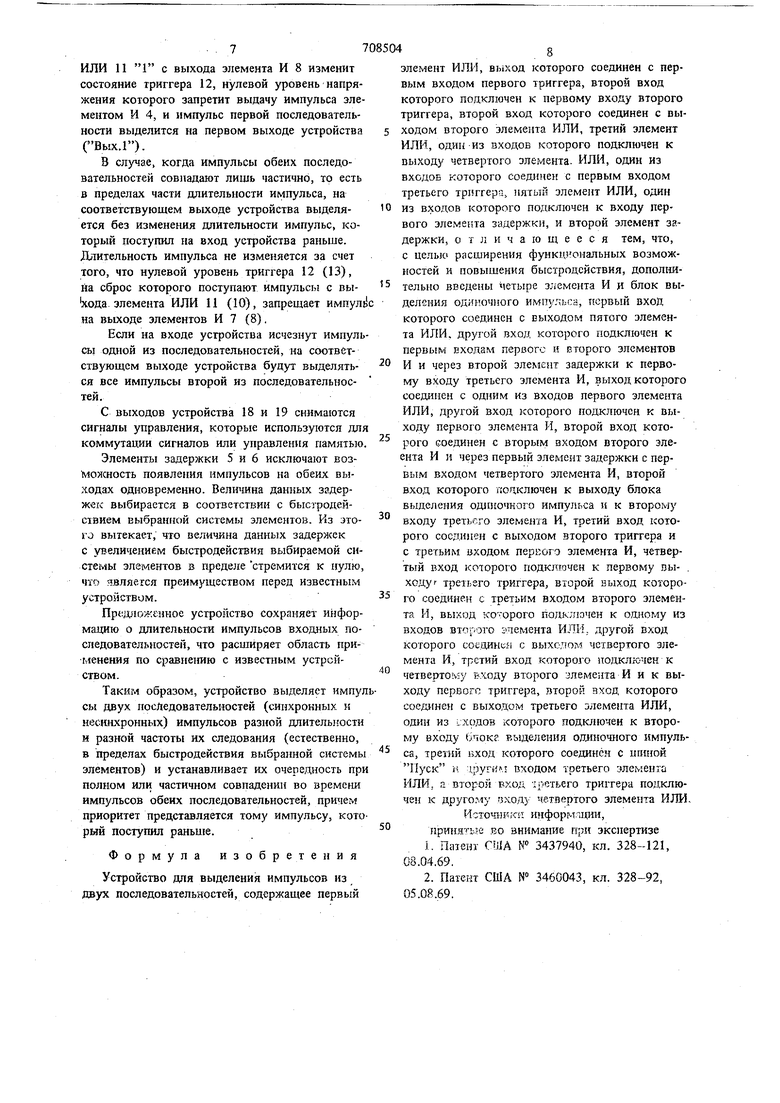

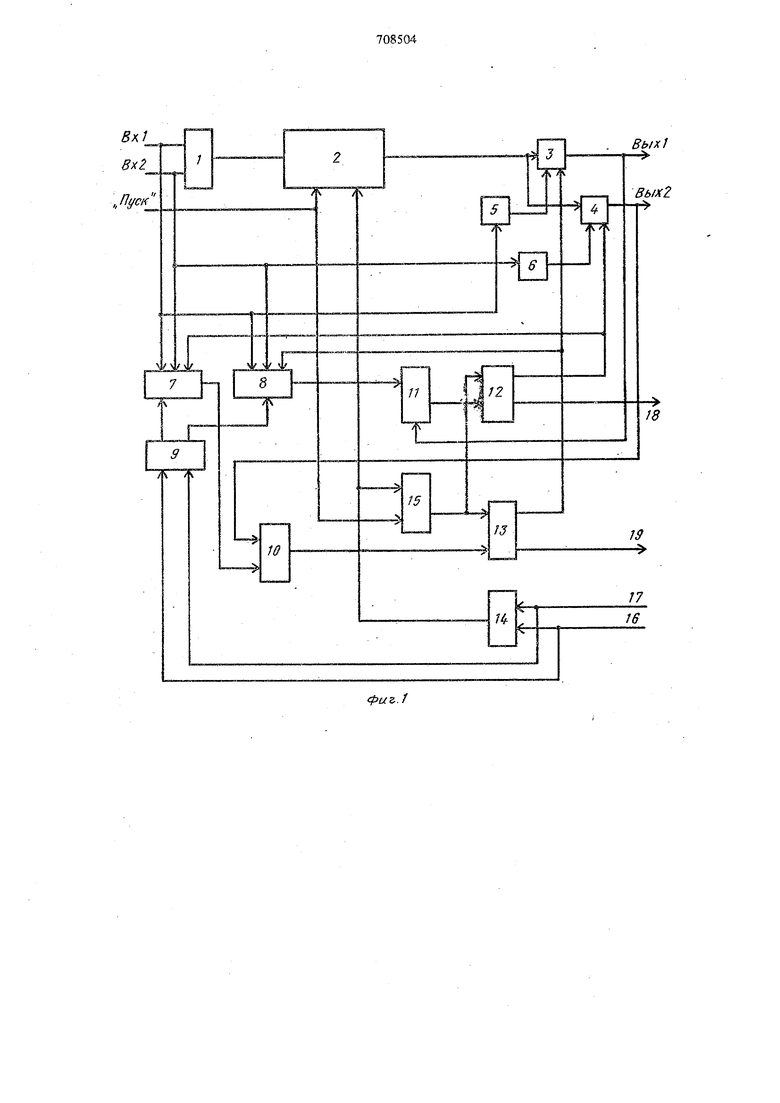

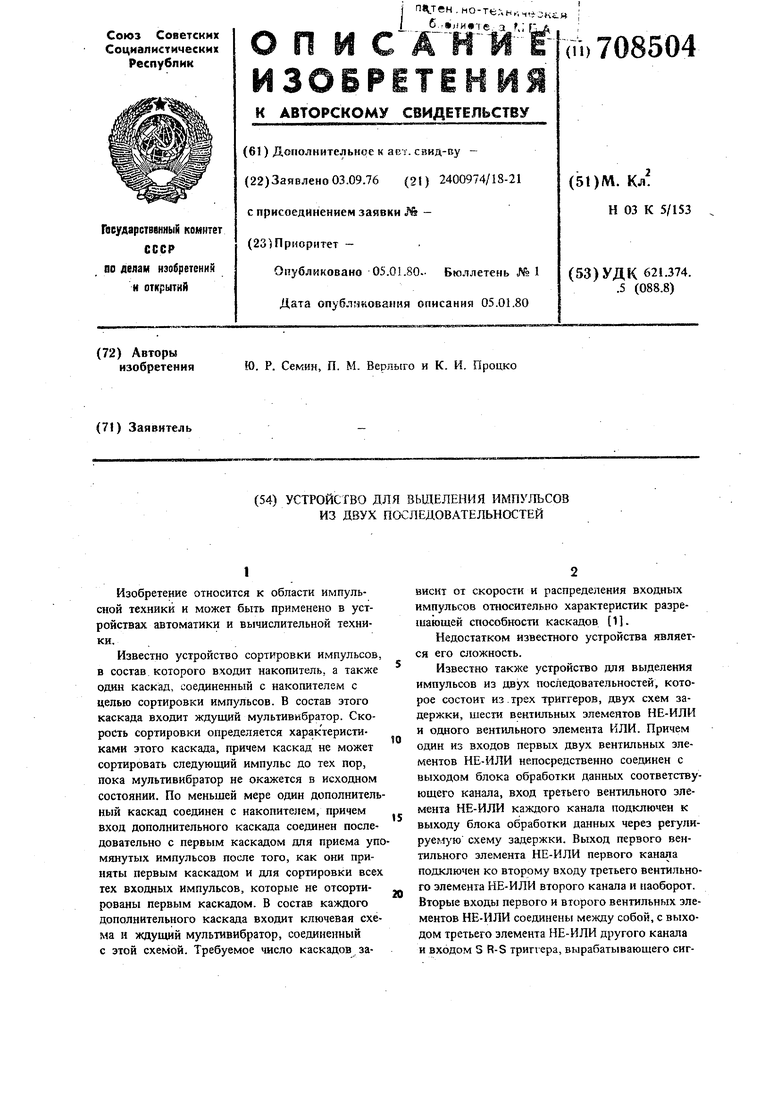

Известно также устройство для выделения импульсов из двух последовательностей, которое состоит нз.трех триггеров, двух схем задержки, шести вентильных элементов НЕ-ИЛИ и одного вентильного элемента ИЛИ. Причем один из входов первых двух вентильных элементов НЕ-ИЛИ непосредственно соединен с выходом блока обработки данных соответствующего канала, вход третьего вентильного элемента НЕ-ИЛИ каждого канала подключен к выходу блока обработки данных через регулируещю схему задержки. Выход первого вентильного элемента НЕ-ИЛИ первого канала подключен ко второму входу третьего вентильного элемента НЕ-ИЛИ второго канала и наоборот. Вторые входы первого и второго вентильных элементов НЕ-ИЛИ соединены между собой, с выходом третьего элемента НЕ-ИЛИ другого канала и входом S R-S триггера, вырабатывающего сигнал РВ обращения другого канала к памяти. Третий вход первого вентильного элемента НЕ-ИЛИ одного канала соединен с выходом второго вентильного элемента НЕ-ИЛИ другого канала и. вторым входом триггера того же канала, Третий вход второго вентильного элемента НЕ-ИЛИ первого канала соединен с третьим входом третьего вентильного элемента НЕ-ИЛИ второго канала и подключен к единичному выходу триггера управления работой блока очередности, нулевой выход которого подключен ю. третьему входу третьего вентильного элемента НЕ-ИЛИ первого канала, соединенног с третьим входом второго вентильного элемента НЕ-ИЛИ второго кайала. Четвертые входы второго и третьего вентильных элементов НЕИЛИ первого канала соединены между собой и подключены к входу R триггера R-S управления и к выходу РВ триггера второго канала. Вход S триггера управления соединен с выходом РА триггера R-S первого канала и с соединенными между собой четвертыми входами второго и третьего вентильных элементов второго канала. Пятые входы вторых и третьих вентильных элементов обоих каналах соеди нены между собой и подключены к выходу вентильного элемента ИЛ{1, входы которого со единены с выходами РА и РВ триггеров R-S каждого канала 2. Недостатком известного устройства является введение ограничелий на временное соотноше1ше поступаюндах последовательностей. В слу чае, когда устройство гарантирует приоритет сигналу одной последовательности, но раньше поступает сигнал второй последовательности, па его выходе выделяется сигнал второй (первой) поспедовательности с задержкой, определяемой схемой задержки, что уменьшает быстродейстаие известного устройства. Кроме того, известное устройство не имеет импульсных выхо дов. Цель изобретения - расширение функдиональных возможностей и повьинение быстродействия. Для этого в устройство для выделения импульсов из двух последовательностей, содержащее первый элемент ИЛИ, выход которого соединен с первым входом первого триггера, вто рой вход которого подключен к первому входу второго триггера, второй.вход которого соединен с выходом второго элемента ИЛИ, третий элемент ИЛИ, один из входов которого по ключен к выходу четвертого элемента ИЛИ,, один Из входов которого соединен с первым входом третьего триггера, пятый элемент ИЛИ, один из входов которого подключен к входу первого элемента задержки, и второй элемент задержки, дополнительно введены четыре элемента И и блок выделения одиночного импульса первый. вход которого соединен с выходом пятого элемента ИЛИ, другой вход которого подключен к первым входам первого и второго элементов И и через второй элемент задержки к первому входу третьего элемента И, выход которого соединен с одним из входов первого элемента ИЛИ, другой вход которого подключен к выходу первого элемента И, второй вход которого соединен с вторым входом второго элемента И и через первый элемент задержки с первым входом четвертого элемента И, второй вход которого подключен к выходу блока выделения одиночного импульса и к второму входу третьего элемента И, третий вход которого соединен с выходом второго триггера и с третьим входом первого элемента И, четвертый вход которого подключен к первому выходу третьего триггера, второй выход которого соединен с третьим входом второго элемента И, выход которого подключен к одному из входов второго элемента ИЛИ, другой вход которого соединен с выходом четвертого элемента И, третий вход которого подключен к четвертому входу второго элемента И и к выходу первого триггера, второй вход которого соединен с выходом третьего элемента ИЛИ, ода} из входов которого подключен к второму входу блока выделения одиночного импульс а, третий вход которого соединен с шиной Пуск и другим входом третьего элемента ИЛИ, а второй вход третьего триггера подключен к другому входу четвертого элемента ИЛИ. На фиг. 1 представлена структурная электрическая схема устройства, а на фиг. 2 - времен1 ые диаграммы работы устройства. Устройство для выделения импульсов из двух последовательностей содержит логический элемент ИЛИ 1, блок 2 выделения одиночного импульса из последовательности за время рабочего цикла; логические элементы И 3 и 4, элементы задержки 5 и 6, логические элементы И 7 и 8, триггер памяти 9, логические элементы ИЛИ 10 и И, R-S триггеры 12 и 13, логические элементы ИЛИ 14 и 15. Входы элемента ИЛИ 1 соединены с входами oOeitx последовательностей, а выход его - с импульсным входом блока 2 выделения одиночного импульса. Управляемые входы блока 2 подключены соответственно к входу импульса пуска устройства и выходу элемента ИЛИ 14. Выход блока 2 соединен параллельно с первыми входами элементов ИЗ, 4, выходы которых соединены с соответствующими выходами импульсов обеих последовательностей. Второй вход элемента И 3 подключен через элемент задержки 5 к входу импульсов первой последовательности, а второй вход элемента И 4 57через элемент задержки 6 к входу импульсов второй последовательности. Первые входы элементов И 7 и 8 параллельно соединены с входом импульсов первой последовательности, а их вторые входы - с входом ИПуЛЬСОВ ВТОрой последовательности. Третьи входы элементов И 7, 8 соединены с соответствующими выходами триггера памяти 9. Выходы элементов И 7 и 8 раздельно соединены с первыми входами элементов ИЛИ 10, 11. Второй вход элемента ИЛИ 10 подключен к выходу импульсов второй последовательности, а второй вход элемента ИЛИ 11 - к выходу импульсов первой последовательности. Четвертый вход элемента И 7, соединенный с вторым входом элемента И 4, подключен к единичному выходу триггера 12, а четвертый вход элемента И 8 - к соединенным между собой вторым входам элемента И 3 и единичному выходу триггера 13. Единичные входы триггеров 12 и 13 параллель но подключены к выходу элемента ИЛИ 15, а их входы сброса соответственно соединены с выходами элементов ИЛИ 11 и 10. Первый вход элемента ИЛИ 15 подключен к шине Пуск устройства, а его второй вход - к вы ходу элемента ИЛИ 14. Первый вход элемента ИЛИ 14 соединен с входом триггера 9, соответствующий выход которого подключен к тре ему входу элемента И 7, и входом 16 импульсов конца рабочего цикла первой последовател ности. Второй вход элемента ИЛИ 14 соединен с другим входом триггера 9 и входом 17 имПульсов конца рабочего цикла второй последовательности. Нулевые выходы триггеров 12 и 13раздельно соединены с выходами устройства 18 и 19. Устройство работает следующим образом. . Импульсы обеих последовательностей поступают на двухвходовой элемент ИЛИ 1, работа которого описывается уравнением Z А + В, где Z - выходной сигнал, А и В - входные сигналы, и на два четырехвходовых элемента И 7 и 8, работа которых описывается уравнением Z А-В-С-Д, где А, В, С, Д - ее входные сигналы. Выходные импульсы элемента ИЛИ 1 поступают на блок 2 выделения одиночного импульса. Блок 2 выделения одиночного импульса вы дает импульс, принадлежащий одной из последовательностей, если на управляемом ее входе изменился уровень напряжения. При поступлении с ншны Пуск импульса пуска триггеры 12,13 устанавливаются в 1. После снятия импульса пуска блок 2 выделяет импульс, принадлежащий одной из последовательностей, который поступает на первые входы трехвходовых элементов И 3, 4. При совпадеини 1 на входах каждого из элементов И 3 и 4 на соотБстствующем выходе устройства появится импульс одной из последовательностей, которьи через двухвходовой элемент ИЛР 11 для кмпульса первой последовательности и двухвходовой элемент ИЛИ 10 для импульса второй последовательности поступает на вход сброса соответствующего R-S триггера 12 или 13, егосостояние на противоположное. Нулевой уровень напряжения на выходе триггера 13 (12) запрещает выход импульса первой (второй) последовательности. Элементы 5 (6) предназначены для компенсации задержки входных импульсов на элементе 1 и блоке 2 с целью обеспечения одновреме 11ого поступления входных импульсов на оба входа элемсг та 3 (4). Элементы 5 и 6 могут СЫТ) рсалг;лсваны посредством последовательного включения необходимого количества логических элементов. Импульсом конца рабочего Щ5кла каждой из последовательностей с входов 16 и 17, поступаюишм через определенное время после выделения импульса на выходе устройства, подготавлнвается блок 2 выделения одиночного импульса к выделению одного имнульса входных послсдоБателыгостей, а R-S - триггеры 12 и 13 устанавливаются в единичное состояние, подготаолйвая элe гeнть И 3 и 4 к выделению следующего им 1ульса, поступающего с блока 2. Если импульсы обеих последовательностей подаются одаювремец, они выделяются одним из Э; ементов 7 или 8 в зависимости от состояния триггера памяти 9, управляемого импульсами концов рабочего цикла. Допусттиу, что в момент совпадения импульСО& обеих последовательностей, на выходе элемента И 7-, что означает, что предыдущий импульс принадлежал первой последовательности, поэтому необходимо запретить выход импульса этой последовательности на лервый выход (Вых.1) и выделить импульс на втором выходе (Вых.2), принадлежащий второй последовательности. Для этого выходной импульс элемента И 7 через двухвходовой элемент ИЛИ 10 поступает на сброс триггера 13, выходной уровень напряжения которого запрещ.ает прохождение на первый выход (Вых.1), устройства импульса первой последовательности. Выделенный на втором выходе (Вых.2) импульс второй последовательности подтверждает состояние триггера 13. Импульс конца рабочего цикла второй последовательности с входа 17 изменяет состояние триггера памяти 9 на противоположное и устанавливает триггеры 12 и 13 в исходное состояние. В этом случае при очередном совпадении импульсов обеих последовательностей через двухвходовой элемент

ИЛИ 11 1 с выхода элемента И 8 изменит состояние триггера 12, нулевой уровень напряжения которого запретит выдачу импульса элементом И 4, и импульс первой последовательности выделится на первом выходе устройства (Вых.1).

В случае, когда импульсы обеих последовательностей совпадают лишь частично, то есть в пределах части длительности импульса, на соответствующем выходе устройства выделяется без изменения длительности импульс, который поступил на вход устройства раньше. Длительность импульса не изменяется за счет того, что нулевой уровень триггера 12 (13), на сброс которого поступают импульсь; с выЬюда. злемента ИЛИ 11 (10), запрещает импул на выходе злементов И 7 (8).

Если на входе устройства исчезнут импульсь одной из последовательностей, на соответствующем выходе устройства будут выделяться все импульсы второй из последовательностей.

С выходов устройства 18 и 19 снимаются сигналы управления, которые используются для коммутации сигналов или управления памятью.

Элементы задержки 5 и 6 исключают возмоясность появления импульсов на обеих выходах одиовременио. Величина данных задержек выбирается в соответствии с быстродействием выбранной системы элементов. Кз этого вытекает, что величина данных задержек с увеличением быстродействия выбираемой системы элементов в пределе стремится к нулю, что является преимуществом перед известным устройством.

Предложенное устройство сохраняет информацию о длительности импульсов входных последовательностей, что расширяет область применения по сравне1гаю с известным устройством.

Таким образом, устройство выделяет импулсы двух последовательностей (синхронных и несинхронных) импульсов разной длительности и разной частоты их следования (естественно, в пределах быстродействия выбранной системы элементов) и устанавливает их очередность при полном или частичном совпадении во време ш импульсов обеих последовательностей, причем приоритет представляется тому импульсу, который поступил psHbUie.

Формула изобретения

Устройство для выделения импульсов из двух последовательностей, содержащее первый

элемент ИЛИ, вь1ход которого соединен с первым входом первого триггера, второй вход которого подключен к первому входу второго триггера, второй вход которого соединен с выходом второго элемента ИЛИ, третий элемент ИЛИ, один из входов которого подключен к выходу четвертого элемента. ИЛИ, один из входов которого соединен с первым входом третьего триггера, пятый элемент ИЛИ, один из входов которого подключен к входу первого элемента задержки, и второй элемент задержки, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей и повышения быстродействия, дополнительно введены четыре элемента И и блок выделения ОДИНОЧ1ЮГО импульса, первый вход которого соединен с выходом пятого элемента ИЛИ, другой вход которого подключен к первым входам первого к isioporo злементов И и через второй элемент задержки к первому входу третьего элемента И, выход которого соедипен с одним из входов первого элемента ИЛИ, другой вход которого подключен к выходу первого элемента И, второй вход которого соединен с вторым аходом второго элеента И и через первый элемент задержки с первым входом четвертого элемента И, второй вход которого подключен к выходу блока выделения одиночного импу1 ьса и к второму входу третьего элеме1гга И, третий вход которого соединен с выходом второго триггера и с третьил входом первого элемента И, четвертый вход Koioporo подключен к первому выходу третьего триггера, второй выход которого соединен с третьим входом второго элемента И, выход ко-орого подключен к одному из входов второго элемента ИЛИ, другой вход которого сосдаыйя с выходом четвертого элемента И, третий вход которого подключен к четвертому входу второго элемента И и к выходу первого триггера, второй зход которого соединен с выходом третьего элемента ИЛИ, один из 1.ходов которого подключен к второму входу бпок. выделения oд fнoчнoгo импульса, третий вход которого соединён с шиной Пуск i фуги , входом третьего элемента ИЛИ, а второй вход -третьего триггера подключен к другому 5лоду етвертого элемента ИЛИ

Источи} си информл1гии, принятьге во внимание при экспертизе

1.Патент США Н 3437940, кл. 328-121, 08.04,69.

2.Патент США № 3460043, кл. 328-92, 05.08.69.

puz.1

Dn п 0.,..Q

U

Вь/х1

п п п Г1 п п п

i

п

пп

д

д

п

пл

пп гт

фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от изменения заданной скорости вращения электропривода постоянного тока | 1985 |

|

SU1377957A1 |

| Устройство для определения экстремальных значений амплитуд сигналов | 1987 |

|

SU1429307A1 |

| Устройство преобразования параллельного кода в последовательный | 1982 |

|

SU1075408A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Устройство для защиты электрических машин | 1982 |

|

SU1037372A2 |

| Широтно-импульсный регулятор для управления вентильным преобразователем | 1983 |

|

SU1181074A1 |

| Анализатор занятости канала связи | 1984 |

|

SU1225021A1 |

| Устройство для защиты трехфазной нагрузки от изменения чередования фаз и обрыва фазы | 1982 |

|

SU1089693A1 |

| Устройство восстановления информации | 1978 |

|

SU792249A1 |

| Устройство для определения напряженного состояния массива горных пород | 1985 |

|

SU1285150A1 |

Авторы

Даты

1980-01-05—Публикация

1976-09-03—Подача