второй пары - с неуправляемым выходом звена.

3. Устройство по п. 1, о т л и чающееся тем, что блок анализа кода содержит пять элементов И, элемент ИЛИ, два триггера и распределитель импульсов, при этом первый и второй входы перйого элемента И соединены соответственно с первым и третьим входами блока, выход первого элемента И соединен с первым входом элемента ИЛИ, второй вход которого подключен к второму входу блока, первый вход второго элемента И соединен с четвертым входом блока, второй вход второго элемента И подключен к седьмому входу блока, вы ход второго элемента И - к третьему входу элемента ИЛИ и к входу устаноки в нуль распределителя, выход элемента ИЛИ соединен с входом установки в единицу первого триггера, вход установки в нуль которого подключен к пятому входу блока, (нестой вход блока соединен с объединенными первыми входами третьего и четвертого элементов И, вторые входы которых подключены к соответствующим выходам первого триггера, выход четвертого элемента И соединен с входом установки в единицу второго триггера, с суммирующим входом распределителя и со сбросовым выходом блока, выход третьего элемента И подключен к входу установки в нуль второго триггера, выход которого соединен с вторым входом пятого элемента И, подключенного выходом к пусковому выходу блока, 1с-й выход распределителя соединен с k-ым управляющим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсных последовательностей | 1974 |

|

SU658720A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство для отладки программ | 1982 |

|

SU1049914A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для индикации | 1978 |

|

SU734755A1 |

1. УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ, содержащее генератор импульсов, первые два тактовых выхода которого соединены с двумя тактовылш входами каждого из П звеньев п- званного элемента задержки, неуправляемый выход каждого (iTi-l)-ro звена элемегуа задержки соединен с сигнальным входом m -го его звена, а его управляемый выход соединен с соответствующим входом элемента ИЛИ, первые входы каждого элемента И из k -и группы блока двухоходовых элементов И соединены с соответствующикм выходами k -го регистра, отличающе е с я тем, что, с целью расширения функциональных возможностей, в него введены и элементов ИЛИ, дополнительный элемент ИЛИ, блок анализа кода, первый вход которого соединен с выходом элемента ИЛИ, а втсфойвход - с выходом п-го звена элемотта задержки, третий и четвертый входы блока анализа кода соединены с соответствующими входами устройства, пусковой выход блока анализа кода подсоединен к сигнальному входу первого звена элемента задержки, второй выход блока анализа кода соединен с первым входом дополнительного элемента ИЛИ, второй вход которого соединен с третьим тактовым выходом генератора импульсов, пятым входом блока анализа кода и третьим тактовым входом первого звена элемента задержки, третьи тактовые входы остальных звеньев соединены с выходом дополнительного элемента ИЛИ, К-й управляющий выход блока анализа кода соединен с вторыми входами элементов И из k -и группы блока двухвходовых элементов И, выходы каждого m -го элемента И каждой группы блока двухвходовых элементов И подсоединены к соответствующему входу m -го элемента ИЛИ в группе, а выход tn-ro элемента ИЛИ подсоединен к управляющему входу m -го звена элемента задержки, первый и второй тактовые выходы генератора импульсов подсоединены к шестому и седьмому входам блока анализа кода. (Л 2. Устройство по п. 1, отличающееся тем, что каждое звено элемента згщержки содержит два триггера и четыре элемента И, вход установки в единицу первого триггера соединен с сигнальны1.1 входом i I 1 звена, а вход установки в нуль с третьим тактовым входом звена, вы ходы первого триггера подсоединены к первым входам первой пары элеменел тов И, объединенные вторые входы которых соединены с вторым тактовым входом звена, выходы первой пары элементов И подсоединены к входам 00 установки в единицу и устанстеки в нуль. вт орого триггера соответственно, выхол которого соединен с объединенными первыми входами второй 1ары элементов И, вторые входы которых соединены между собой и подсоединены к первому тактовому входу звена элемента задержки, а третий вход одного из элементов И второй пары соединен с управляющим входом звена, выход трехвходового элемента И второй пары соединен с управляемЕЛМ выходом звена, а вы-ход двухвходового элемента И

1

Изобретение относится к вычислительной технике и может быть использовано для передачи двоичного позиционного кода с временным уплотнением.

Известно устройство для преобразования параллельного кода в последовательный, содержащее генератор импульсов, регистр, элементы И и ИЛИ, элемент задержки, дешифратор, выход которого соединен со схемой опроса регистра СI ,

Недостатком данного устройства является то, что оно преобразует параллельный код в последовательный в словах с неизменяющейся длиной сло7 ва. При преобразовании слов с изменяющейся длиной данное устройство не обеспечивает необходимой плотности передаваемой информации.

На иболее близким к изобретению является устройство, содержащее генератор импульсов, первые два тактовых вахока которого соединены с двумя тактовыми входами каждого из f) звеньев -элемента задержки, неуправляемый выход каждого (m-l)-oro звена элемента задержки соединен с сигнальным входом каждогогп-го его звена, а его управляемый выход соединен с соответствующим входом элемента ИЛИ, первые входы каждого элемента И из k-ой группы блока двухвходовых элементов И соединены с соответствующими входами k -го регистра 2

Недостатком известного устройства является то, что при опросе вазбужденного выхода регистра блокирую.

ется дальнейшая работа устройства задержки из-за ввода информации о состоянии регистра в первую ступень каждого звена элемента задержки, т.е. устройство пригодно только для преобразования параллельного кода с одним значащим разрядом двоично-позиционного кода, записанного в один регистр, и непригодно для преобразоQ вания других видов или кодов, записанных в несколько регистров, что значительно сужает функциональные возможноеги известного устройства и затрудняет применение его для преобразования кодов любого вида и для

5 преобразования параллельных кодов записанных в несколько регистров.

Целью изобретения является расишрение функциональных возможностей устройства преобразования параллельного кода в последовательный.

Поставленная цель достигается тем, в устройство преобразования парашлельного кода в последовательный, содержащее генератор импульсов, пер5 вые два тактовых выхода которого соединены с двумя тактовыми входами каждого из п звеньев п -звенного элемента задержки, неуправляемый выход кащюго (m-l)-ro звена элемента

д задержки соединен с сигнальным входом ffi -го его звена, а его управляемый выход соединен с соответствующим входом элемента ИЛИ, первые входы каждого элемента И из k-и группы блока двухвходовых элементов И соединены с соответствующими выходами К-го регистра, введены И элементов ИЛИ, дополнительный элемент ИЛИ,

блок анализа кода, первый вход которого соединен с выходом элемента ИЛИ а второй вход - с выходом П -го звена элемента эа,цержки, третий и четвертый входы блока анализа кода соедикены с соответствующими входами устройства, пусковой выход блока анализа кода подсоединен к сигнальному входу первого звена элемента задержки, второй выход блока анализа кода соединен с первым входом дополнительного элемента ИЛИ, второй вход которого соединен с третьим тактовым выходом генератора импульсов, пятым входом блока ансишза кода и третьим тактовым входом первого звена элемента задержки, третьи тактовые входы остальных звеньев которого соединены с выходом дополнительного эле.мента ИЛИ, k -и управляющий выход блока анализа кода соединен с вторыми входами элементов И из k-и группы блока двухвходовых элементов И, выходы каждого m -ого элемента И каждой группы блока двухвходовых элементов и подсоединены к соответствукацему входут го элемента ИЛИ в группе; а выход m -го элемента ИЛИ подсоединен к управляющему входу Srs-ro звена элемента задержки, первый и второй тактовые выходы генератора импульсов подсоединены к шестому и седЫЖзму входам блока анализа кода.

При этом каждое звено элемента задержки содерясит два триггера и четыре элемента И, вход установки в .вен с сигнальным входом звена, а вход установки в нуль - с треть им тактовым входом звена, выходы первого триггера подсоединены к, пер вым входам первой пары элементов И, объединенные вторые входы которых соединены с вторым тактовым входом звена, выходы первой пары элементов И подсоединены к входам установки в единицу и установки в нуль второго триггера соответственно, выход которого соединен с объединен ными первыми входами второй пары элементов И, вторые входы которых соединены между собой и подсоединены к первому тактовог-гу входу звена элемента задержки, а третий вход од ного из элементов И второй пары сое динен с управляю1Д 5М входом звена, выход трехвходового элемента И второй пары соединен с управляемом выходом звена, а выход двухвходового элемента И второй пары - с неуправляе Фам выходом звена. Кроме того, блок анализа кода со держит пять элементов И, элемент ИЛИ, два триггера и распределитель импульсов, при этом первый и второй входы первого элемента И соединены соответственно с первым и третьим

входами блока, выход первого элемента И соединен с первым входом элемента ИЛИ, второй вход которого подключен к второму входу блока, первый вход второго элемента И соединен с четвертым входом блока, второй вход второго элемента И подключен к седьмому входу блока, выход второго элемента И - к третьему входу элемента ИЛИ и к входу установки в нуль распределителя, выход элемента ИЛИ соединен с входом установки в единицу первого триггера, вход установки в нуль которого подключен к пятому входу блока, шестой вход блока соединен с объединенными первыми входами третьего и четвертого элементов И, вторые входы которых подключены к соответствующим выходам первого триггера, выход четвертого элемента И соединен с входом установки в единицу второго триггера, с cyм 5иpyющим входом распределителя и со сбросовым выходом блока, выход третьего эяемента И подключен к входу установки в куль второго триггера, выход которого соединен с вторым входом пятого элемента И ,подключенного выходом пусковому выходу блока, К -и выходраспределителя соединен с k-ым уп- равляющим выходом блока.

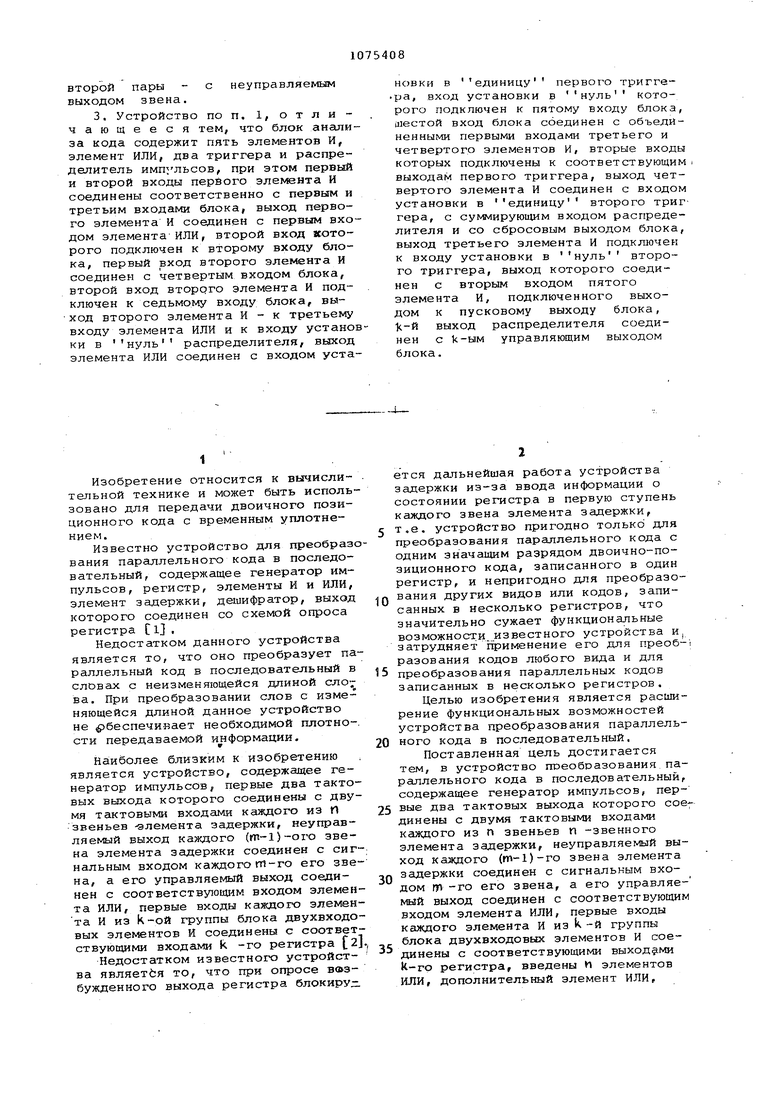

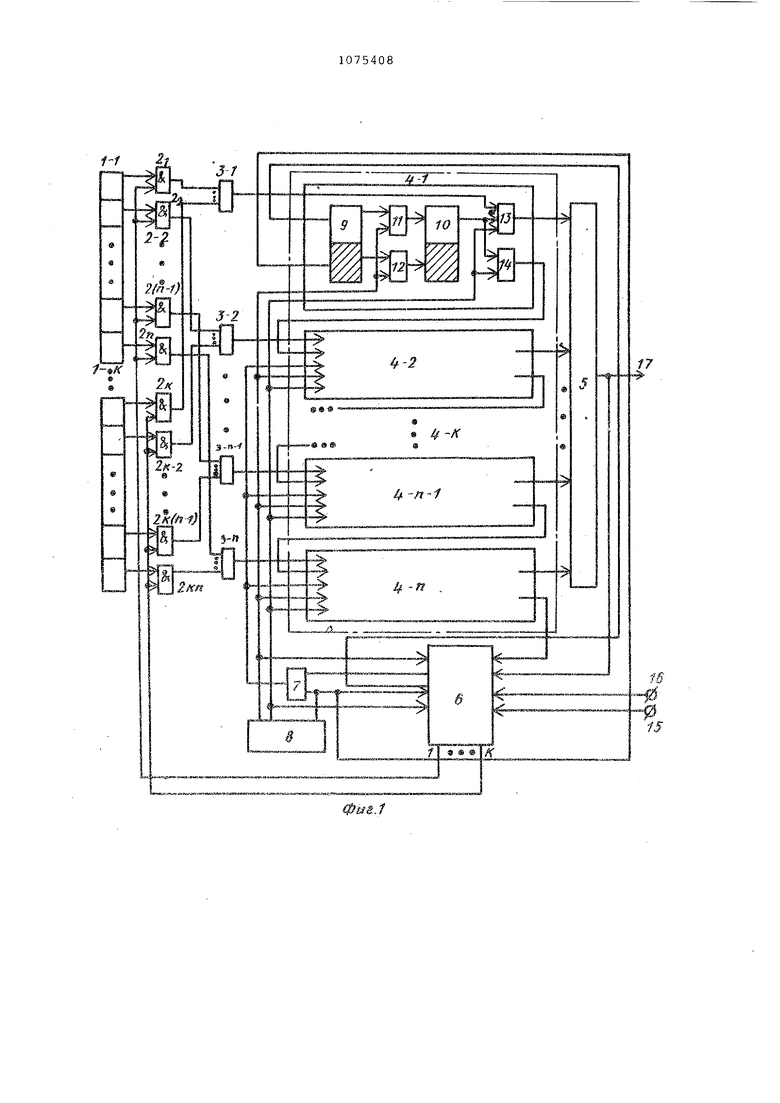

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 возможное конкретное выполнение блока анализа кода. Устройство содержит регистры 1-lfl-K, соответствующие выходы которого соединены с первыми входами каждого элемента И К-и группы блока двухвходовых элементов И 2-1-г2, элементы S-l-rB-n ИЛИ, выходы которых соединены с входами соответствующих звеньев 4-1т4-П элемента задержки, выходы которых подключены к входу элемента ИЛИ 5, блок 6 анализа кода, первый -вход которого соединен с выходом элемента ИЛИ, а второй вход - с выходом п -го звена элемент га задержки, третий и четвертый входа блока анализа коды соединены -с со- ответствующими входами устройства, дополнительный элемент ИЛИ 7, генератор 8 импульсов, первые два тактовых выхода которого соединены с двумя тактовыми входами каждого из звеньев задержки. Неуправляемый выход каждого (п-1)-го звена задержки соединен с сигнальным входом каждого звена, а его управляемой выход соединен с соответствующим входом элемента ИЛИ 5; триггеры 9 и 10 звена элемента задержки, первую пару элементов И 11 и 12 вторую пару элементов И 13 и 14, первый пусковой вход 15 устройства, второй управляю11№1й вход 16 устройства, вы- ход 17 устройства. Блок анализа кода (фиг. 2) содер жит элементы И 18-22, элемент ШШ 23,. триггеры 24 и 25, распределитель 26 импульсов, При этом первый и второй входы первого элемента И 2 соединены с первым и третьим входам блока соответственно, выход первого элемента И 21 соединен с первым вхо дом элемента ИЛИ 23,. второй вход ко торого подключен к второму входу блока, первый вход второго элемента И 22 соединен с четвертым входом блока, второй вход второго элемента И 22 подключен к седьмому входу блока, выход .Второго элемента и 22 к третьему входу элемента ИЛИ 23 и к входу установки в нуль распре делителя 26, выход элемента ИЛИ 23 соединен с входом установки в еди первого триггера 25, вход установки в нуль которого подключен к пятому входу блока, шестой вход блока соединён с объединенными первыми входами третьего 20 и четвертого 19 элементов И, вторые входы которых подключены к соответствующим выходам первого триггера 25, выход четвертого элемента И 19 соед нен с входом усзгановки в единицу второго триггера, с суммирующим входом распределителя и сбросовым выхо дом блока, выход третьего элемента И 20 подключен к входу установки в нуль второго триггера 24, выход которого соединен с вторым входом пятого элемента И 18, подключенного выходом к пусковому входу блока, выход распределителя 26 соединен с К-м управляющим выходом блока. Устройство работает следующим образом. По сигналу Пуск , фop /шpyeмoму блоком б анализа (совпа,цан1адему « с Т1) и поступающему на сигнальный вгход первого звена 4-1 элемента задер« ки, устанавливается в единицу триггер 9 первого звена 4-1 элемента задержки , По тaктoвo 1y импульсу Т2, приходя щему затем на второй тактовый вход звена 4-1 и на второй вход элемента И 11, устанавливается в единицу триггер 10. По тактовому импульсу ТЗ, приходящему на третий тактовый вход звена 4-1,, устанавливается нуль триггер 9„ Следующим тактовым импульсом Т1, поступающим на первый тактовый вход звена 4-1 элемента задержки, опрашивается состояние триггера 10 и сигналом с выхода элемента И 14 (неуправляемый выход звена), поступающим на сигнальный вход второго звена 4-2, устанавливается в единицу триггер 9 второго звена 4-2, и при наличии сигн.ала на управляющем входе первого звена 4--1 с выхода первого разряда первого из регистров 1-1 формируется с выхода э.лемента И 13 кодовый импульс на вход элемента ИЛИ 5. По следующим трем тактовым импульсам, приходящим на тактовые входы второго звена 4-2 элемента задержки, формируется аналогичным обраэог-i сигнал со своего неуправляемого выхода на сигнальный вход третьего звена 4-3 и опращивается состояние управляющего входа второго звена 4-2, При наличии сигнала формируется второй кодовый импульс на управляемом выходе второго звена 4-2 элемента 3 адержки, Остальные звенья 4-к,44-п элемента задержки аналогичным образом форг-ируют сигналы с неуправляемых выходов и оправдывают состояние управл.яюшлх входов и формируют кодовые импул.ьсы на вкоды элементов ИЛИ 5, с выхода элемента ИЛИ 5 формируется первое кодовое слово, Блок 6 анализа кода работает в , двух режимах: в первом режиме по.але опроса всехвыходов первого из регистров 1-1 по сигналу, приходящем от неуправляемого выхода 4-П звена элемента задержки через элемент ИЛИ :23, устанавливается в единицу . триггер 25, сигнал с прямого вых(5да которого стробируется.тактовым импульсом Т2 и поступает с выхода элемента И 19 на второй выход Сброс блока б анализа кода по этому сигналу звенья 4-244-п элемента задержки, кроме первого, устакавливаются в исходное состояние. Одновременно сигнал с выхода элемента И 19 устанавливает в единицу триггер 24 и поступает на управляющий вход распределителя 26 импульсов, который выдает импульс на своем втором выходе. Таким образом, снимается сигнал, разрешающий.выдачу сигналов с выходов первого из регистров 1-1 через первую уруппу элементов И блока . двухвходовых элементов И 2-1 и через элементы ИЛИ 3-1-гЗ-п и вьщается сигнал на входы второй группы элементов И блока двухвходовых элементов, разрешающий выдачу информации с второго регистра 1-2 через элементы 3-1тЗ-и на управляющие входы звеньев 4-1т-4-П элемента задержки. Тактовый импульс устанавливает триггер 25 в нуль, а приходящий . за ним тактовый импульс Т1 разрешает выдачу сигнала с выхода триггера 24 на вход 15 Пуск блока 6 анализа кода. По тактовог у импульсу Т2 затем триггер 24 устанавливается в нуль. Сигнал Пуск поступает на сигнальный вход первого звена 4-1 элемента задержки и начинается опрос второго регистра 1-2. Таким образом осуществляется циклический опрос всех регистров 1-1т1-К, Во втором режиме блок 6 анализа кода анализирует кодовые импульсы, поступающие с выхода элемента ИЛИ 5 при наличии сигнала на входе 16 Режим. На фиг, 2 приведена простейшая схема блока анализа кода, позволяющая преобразовывать единично-позиционные коды и кода постоянной длины, как описано в первом режиме . При приходе импульса кода с выхода элемента ИЛИ 5 через элемент Н 18 на вход элемента ИЛИ 5 он уста навливает в единицу триггер 25 и формирует сигнал Сброс, по ко Topofvjy все звенья 4-2т4-п эле мента задержки, кроме первого, устанавливаются в исходное состояние, и сигнал Пуск в первое звено 4-1 эле мента задержки, а также снимает раз решение с входов первой группы 2-142-п элементов И и выдает разреш ние на входы в.торой группы 2-2т2-11 элементов И блока двухвходовых элементов И, как было описано-в первом режиме, Далее осуществляется последовательный опрос второго регистра 1-2 аналогично первому и формируется второе кодовое слово. Таким образом формируются слова в последовательном коде, соответствующем сострянию регистров l-l-l-K.. Причем наличие блока 6 анализа кода, формирующего сбросовые и пусковые импульсы, и эле мента задержки позволяет формировать слдаа азличной длительности в зави сиьости от ВИДА заданного режима. Например, во втором режиме при преобразовании единично-позиционных кодов нулевые разряды, идущие за еди ницей, не несут информации и поэтому для повышения плотности передачи информации возникает необходимость формировать слова укороченной длительности, определяемой положением единицы на выходе регистра, что и позволяет сделать предлагаемое устройство. Подключение неуправляемых выходов других звеньев к входам блока анализа кода и организация управления ими в объеме структуры блока анализа кода в первом режиме работы позволяет производить преобразование параллельных кодов различных форматов без изменения структуры электрической схемы устройства. Для преобразования кодов различной длительности другого вида (не двоично-позиционных) в структуру блока б анализа кода между входом от элемента ИЛИ 5 и первым входом элемента ИЛИ 5 и первым входом элемента И 21 необходимо установить счетчик импульсов в зависимости от вида преобразуемого кода. Например, при преобразовании кода 2 из 4-х счет;4ик двух импульсов при наличии второго импульса, сигнал переполнения с выхода счетчика поступает на вход элементов И 18 и 19 для формирования сигналов Сброс и Пуск, Таким образом, расширение функциональных возможностей за счет введения в устройство блока анализа кода, управляющего пуском и сбросом эле мента задержки и подключением выходов регистров 1-1т1-К управляющим .входам элемента задержки, заключается в том, что устройство позволяет преобразовать двоичные параллельные коды в последовательные коды постоянной длины, двоично-позиционный и другие виды кодов в последовательные коды переменной длины.

-12,

sL

J/

:|iK.4

XT«™J-#1

&

InuM

2e

/Л-/;

Ш

jr-2

{}

.

9/f

e e

e

2V

Sc

e

Г-& 3-n-f

ff}рсяомиюиимягж-чв:

J I«««« «

I i

L«J

/7

фив. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования параллельного кода в последовательный | 1975 |

|

SU520703A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Насос | 1917 |

|

SU13A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования импульсных последовательностей | 1974 |

|

SU658720A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-23—Публикация

1982-04-05—Подача