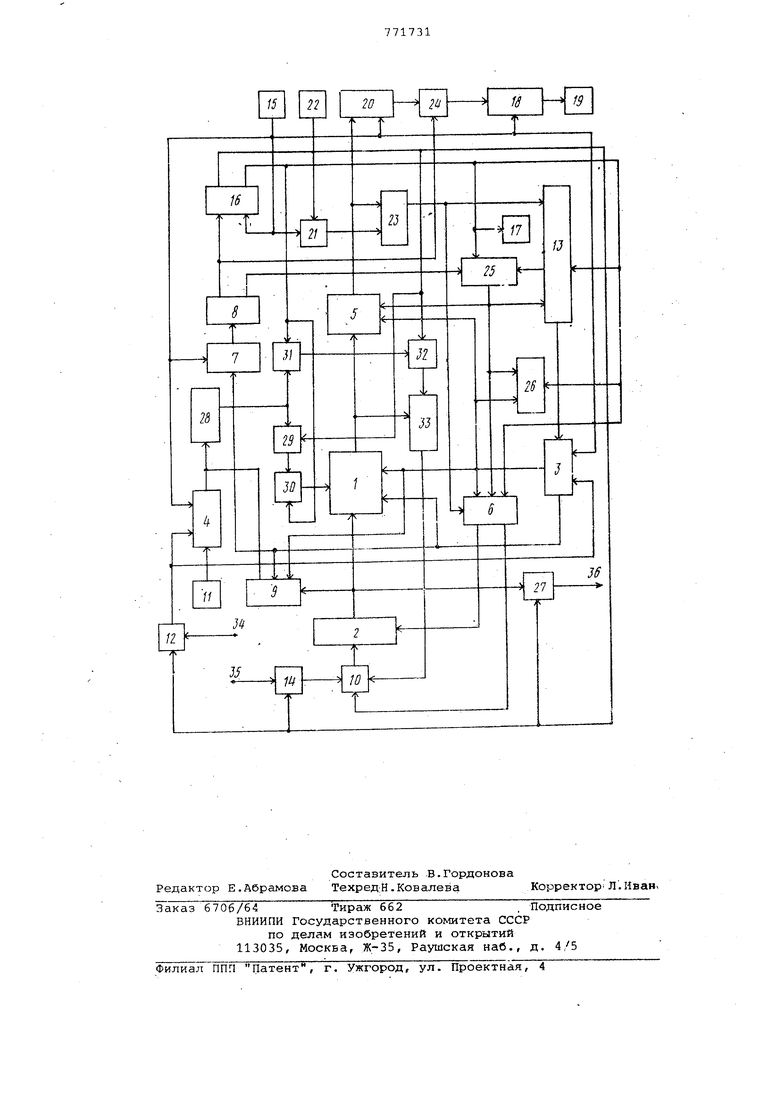

ции, первым входам формирователя контрольных импульсов, второго блоков контроля и первого блока контроля, второй вход которого соединен с выходом накопителя, первый вход первого регистра адреса подключен к выходам первой группы элементов И, первые входы которых соединены с первым входом уатройсува, второй вход которого подключен х первнм входам второй группы элементов И, выход первого генератора одиночных импульсов соединен с первыми входами первого триггера, элемента ИЛИ, BTOpoiO тригг ера, третьего триггера к вторыми входами счетчика и первого регистра адреса, третий вход которого подключен к первому выходу бпоха управления, вход перв.ого дешифратора соединен с выходом счетчика, а первый выход дешифратора под ключен к первому входу элемента И и ко второму вхолу первого триггера первый выход которого соединен со вторыми входами первой, второй и тре тьей групп элементов И, второй выход первого триггера подключе н ко входу второго блока индикации, первому входу блока упра.вления, вторым входом второго блока контроля и формирователя контрольных импульсов, выход первого блока контроля подключен ко- второму входу третьего триггера и первому входу четвертого три гера, выход которого соединен со вторым входом блока управления и третьим входом формирователя контрол ных импульсов, выход второго генера тора одиночных импульсов подключен ко второму входу элемента ИЛИ, выход которого соединен со вторым входом четвертого триггера,, второй вход второго триггера подключен к выходу элемнета И, второй вход которого со единен с выходом третьего триггера, выход второго триггера подключен ко входу третьего блока индикации, вхо ды блока местного управления подклю чены соответственно ко вторым выходам первого дешифратора, первого триггера и блока управления, а выхо блока местного управления соединен со вторым входом второго блока контроля, с третьими входами первого блока контроля и блока, управления и четвертым входом формирователя кс трольных импульсов г2 Недостатком этого устройства является снижение надежности и скоpocTi; контроля с увеличением числа адресоВ( с накопителе вследствие при менения многократного последоёатель ного обхода адресов при поразрядном контроле накопителя. Целью настоящего изобретенчк явг ляется поаьвиенне Сыстродёйствкя и нгдежности устройства. поставленная цель достигается тем, что устройство содержит второй регистр адреса, третий генератор эдиночных импульсов, второй дешифратор, коммутатор, вторую и третью группы элементов ИЛИ и четвертую и пятую группы элементов и, причем входы второго регистра адреса подключены соответственно ,к вьаходам первого генератора одиночных импульсов, третьего генератора одиночных импульсов и первой группы элементов И, а выход второго регистра адреса соединен с четвертым входом первого блока индикации и входом второго дешифратора, выход которого подключен к первым входам четвертой и пятой групп элементов И, выходы кото- . рых соединены соответственно с первыми входами второй и третьей групп элементов ИЛИ, вторые входы четвертой группы элементов И и третьей группы элементор ТОЙ подключены к первому входу первого триггера, втлрой вход которого соединен со вторыми входами второй группы элементов ИЛИ и пятой группы элементов И, выходы третьей группы элементов. ИЛИ соединены с- первым входом коммутаю ра, второй вход которого подключен к выходу накопителя, а выход - к третьим входам первой- группы элементов ИЛИ, выходы второй группь: элементов ИЛИ подключены к четвертому входу накопителя. На чертеже изображена блок-схема предложенного устройства. Устройство содержит накопитель 1, регистр числа 2, первый регистр адреса 3 и второй регистр адреса 4, выполненные в виде счетчиков, первый блок контроля 5, формирователь контрольных импульсов б, счетчик 7, дешифратор 8, первый блок индикации 9, первую группу элементов ИЛИ 10, третий генератор одиночных импульсов 11, первую группу элементов И 12, блок управления 13, вторую группу элементов И 14, первый генератор одиночных импульсов 15, первый- триггер 16, второй блок индикации 17, второй триггер 18, третий блок индик-ации 19, третий триггер 20, элемент ИЛИ 21, второй генератор одиночных импульсов 22, четвертый триггер 23, элемент И 24, блок местного управления 25, второй блок контроля 26, третью группу элементов К 27, второй дешифратор 28, ЧЕ тнертую группу элементов И 25, вторую группу элементов ИЛИ 30, пятук группу элементов И 31, третью группу элементов ИЛИ 32, коммутатор 33, первый вход устройства 34, второй вход устройства 35 и выход устройстба 36. входы регистра числа., 2 подключе-; ны соответственно к выходу первой группы элементов ИЛИ 10 и первому выходу формирователя контрольных импульсов б, второй выход которого

соединен с первьами входами первой группы элементов ИЛИ 10, вторые входы которых подключены к выходам второй группы элементов И 14, выход регистра числа 2 соединен с первыми входами первого блока индикации 9, .накопителя 1 и третьей группы элементов И 27, выходы которой подключены к выходу устройства 36. Первый выход первого регистра адреса 3 соединен со вторыми входами накопителя 1 и первого блока индикации 9 и первым входом счетчика 7. Второй выход первого регистра адреса 3 подключен к третьим входам накопителя 1 и первого блока индикации 9, первым входам формирователя контрольных импульсов б, первого 5 и второго 26 блоков .контроля, второй вход блока 5 соединен с выходом накопителя. Первый вход первого регистра .адреса 3 подключен к выходам первой группы элементов И 12, первы входы которых соединены-с первым входом устройства 34, второй.вход 35 которого подключен к первым входам второй группы элементов Н 14. Выход первого генератора одиночных импульсов 15 соединен с первыми входами первого триггера 16, элемента ИЛИ 21, второго 18 и третьего 20 триггеров и вторыми входами счетчика 7 и первого регистра гщреса 3, третий вход которого подключен к певому выходу блока управления 13. Вход первого дешифратора 8 соединен с выходом счетчика 7, первый выход дешифратора 8 подключен к первоглу входу элемента И 24 и ко второму входу первого триггера 16, первый выход которого соединен со вторыми входами первой 12, второй 14 и третьей 27 групп элементов И. Второй выход первого триггера 16 подключен ко входу второго блока индикации 17, первому входу блока управления 13, вторым входам второго блока контроля 26 и формирователя контрол ных импульсов 6, йлход первого блока контроля 5 подключен ко второму входу третьего триггера 20 и первому входу четвертого триггера 23, выход которого соединен со вторым входом блока управления 13 и треть входом формирователя контрольных импульсов 6. выход второго генератора одиночных импульсов 22 подключен ко второму входу элемента ИЛИ 21, выход которого соединен со вторым входом четвертого триггера 23. Второй вход второго .триггера 18 подключен к выходу элемента И 24, второй вход которого соединен с выходом третьего триггера 20, а выход второго триггера 18 подключен ко входу третьего блока индикгщий 19. Входы блока местного управления 25 подключены соответственно ко вторым выходам первого дешифратора 8, первого триггера 16 и блока управления 13, а выход блока местного управлен 25 соединен со вторым входом второго блока контроля 26, с третьими входами первого блока контроля 5 и блока управления 13 и с четвертым входом формирователя 6. Входы второго регистра адреса 4 подключены соответственно к выходам первого 15 и третьего 11 генераторов одиночных импульсов и первой группы элементов И 12, а выход - к четвертому входу nepBoio блока индикации 9 и входам второго дешифратора 28. Выход дешифратора 28 соединен с первыми входами четвертой 29 и пятой 31 групп элментов И, выходы которых соединены соответственно с первыми входами второй 30 и третьей 32 групп элементов ИЛИ. Вторые входы четвертой групы элементов И 29 и третьей группы элементов ИЛИ 32 подключены к первому входу первого триггера 16, второй вход которого соединен со втрыми входами второй группы элементо ИЛИ 30 и пятой группы элементов И 31. Выходы третьей группы элементов ИЛИ 32 соединены с первым входом комутатора 33., второй вход которого подключен к выходу накопителя, а выход - к третьим входам первой групы Элементов ИЛИ 10. Выходы второй группы элементв ИЛИ 30 подключены к четвертому входу накопителя 1.

Устройство работает следующим образом.

Для автономного контроля работоспособности оперативного запоминающего устройства отводится отрезок времени, в течение которого формируется контрольный тест (тяжелый код), производится запись этого кода, считывание, проверка правильности считанной информации и формирование сигнала исправности (или неисправности) оперативного запоминающего устройства.

Накопитель 1 состоит из набора отдельных модулей (например, полупроводниковых интегральных микросхем) , образующих необходимое число строк и столбцов и соединенных между собой известным способом. Информационные выходы модулей, составляющих один столбец, не имеют соединения между собой.

Генератор одиночных импульсов 15 служит для вызова режима автономного контроля. Сигнал вызова режима автономного контроля формируется либо после подачи на вход устройства питающих напряжений, либо командным путем, либо после нажатия специалЪной кнопки.

Генератор одиночных импульсов 22 предназначен для повторного пуска автономного контроля после его .останова. Генератор одиночных им- пульсов 11.служит для построчной

локализации ошибки в числовом тракте во время автономного контроля. Сигнсшы этих генераторов могут формироваться либо комайдным путем, либо после нажатия соответствующей кнопки. .

Сигнал вызова автономного контроля, поступающий от генератора 15 (например, после подачи на вход устройства питающих напряжений), устанавливает в нулевое состояние регистры адреса 3 и 4, счетчик 7, триггер 18, триггер 23и триггер 20 и в единичное состояние триггер 16. Низкий уровень сигнала с нулевого выхода триггера 16 поступает на соответствующие входы элементов И 12, 14 и 27 и блокирует устройство по входным и выходным цепям от внешних устройств-пользователей. Сигналы с парафазных выходовтриггера 16 поступают на первые входы элементов И 29 и 31 и первые входы элементов ИЛИ 30 и 32. При этом происходит блокировка дешифратора 28, формирующего си.гналы выбора строк, по вход накопителя 1 и разблокировка этого , дешифратора по входу коммутатора 33 с одновременной параллельной коммутцией входных цепей выбора строк накопителя 1 и разкоммутацией входных цепей выбора информации иЗ строк комутатора 33. Нулевому состоянию счетчика 7 соответствует возбуждение первого выхода дешифратора 8, в результате чего блок/ 25 формируе на своем выходе команду Запись. Запись тяжелого кода начинается с первой ячейки каждой строки накопителя 1 , при этом во все разряды нечетных ячеек строк записываются О а во все разряды четных ячеек строк 1. Регистр адреса 3 последовательно перебирает все адреса одной строки, а формирователь6, реагируя на состояние младшего разряда регистра адреса 3, формирует на своих выхода в требуемой последовательности сигнлы установки в О или 1 регистра числа.2. Тяжелый код с регистра числа 2 записывается в накопитель 1. Регистр адреса 3 переключается в очередное состояние в конце кшкдого обращения к выбранному адресу сигналом, поступающим на его счетный вход с блока управления 13.

После обхода йсех адресов одной строки регистр адреса 3 снова оказывается в йулеврм состоянии, а счетчик 7 переключается в очередное состояние, которому соответствует возбуждение второх- о выхода дешифратора 8, в результате чего блок 25 формирует на своем выходе команду Чтение с записью обратного кода.

Чтение тяжелого кола, записанног при первом обходе адресов строк, начинается с первой ячейки каждой стрки накопителя 1. Информация с накопителя 1 поступает в блок контроля

5, который производит позарядное сравнение информации, поступившей с каждой строки, с эталонным сигналом, который формируется в блоке контроля 5 с учетом состояния младшего разряда регистра адреса 3 и выполняемой команды.

После чтения происходит запись обратного тяжелого кода по выбранному адресу каждой строки, при этом во все разряды нечетных ячеек строк записываются 1, а во все разряды четных ячеек строк - О.

После вторичного обхода всех адресов одной строки регистр адреса 3 снова оказывается в нулевом состоянии, а счетчик 7 переключается в новое состояние, которому соответствует возбуждение очередного выхода дешифратора 8, в результате чего блок 25 формирует на своем выходе команду Чтение с записью нулей.

Чтение обратного тяжелого кода, записанного при втором обходе адресов строк, начинается с первой ячейки каждой строки накопителя 1. При этом информация с накопителя 1 поступает в блок контроля 5.

После чтения происходит запись нулей по вьабранному адресу каждой строки, т..е. во все разряды нечетных и четных ячеек строк записываются О.

После.третьего обхода всех адресов одной строки регистр адреса 3 снова оказывается в нулевом состоянии, при этом происходит полное заполнение счетчика 7. В результате этого возбуждается последний выход дешифратора 8.

Сигнал с последнего выхода дешифратора 8 поступает на нулевой установочный вход триггера 16 и переключает его в нулевое состояние, чт приводит к разблокировке устройства по входным и выходным цепям с внешними устройствами-пользователями оперативного запоминакидего устройства.

Сигнал с последнего выхода дешифратора 8 поступает также на один из входов элемента И 24. На другой вход этого элемента подается высоки уровень сигнала с нулевого выхода триггера 20 (при отсутствии сбоя В режиме автоконтроля), в результате чего на единичный установочный вход триггера 18 поступает сигнал, который переключает триггер 18 в единичное состояние.

состояние триггера 16 и триггера 18. отображается соответствующими блоками индикации 17 и 19.

Выше была рассмотрена и описана работа устройства при отсутствии сбоев (ошибок) в контрольной информации ,в режиме автономного контроля. В случае выхода из строя какого-либо элемента числового тракта накопителя 1, ухода его параметров за допустимые пределы и при других неисправностях происходит искажение записанной в накопитель 1 контрольной информации. Ошибка обнаруживается блоком контроля 5. Сигнал ошибки поступает на единичные установочные входы триггеров 20 и 23 и переключает их в единичное состояние. Высокий уровень сигисша с единичного выхода триггера 23 поступает на соответствующие входы блока управления 13 и формирователя 6. Происходит останов автоконтроля, т.е. прекращаетс формирование временной диаграммы блоком правления 13 и формирователем 6. При останове автономного контроля режим чтения в устройстве не прекращается, поэтому считанная информация сохраняется на выходе накопителя 1.

Для определения истинного состава информации, записанной в накопитель 1, служит блок 26.. Для локализации неисправной строки с помощью генератора 11 (например, путем нажатия специальной кнопки) формируются одиночные импульсы, которые поступают на счетный вход регистра адреса 4. Дешифратор 28, реагируя на состояние регистра адреса 4, формирует на своих выходах сигналы выбора строк, которые через элементы И 31 и элементы ИЛИ 32 поступают на вход ком: 1утатора 33. С выхода коммутатора информация одной строки через элемеш-ы ИЛИ 10 поступает в регистр числа 2. С помощью блока индикации 9 определяется неисправный адрес, неисправная строка и состав информации в числовом тракте накопителя 1. Сравнивая состояние элементов индикации числового тракта блока 9 и элементов индикации блока 26, определяют неисправные разряды числового тракта.

После локализации неисправного адреса, строки и разряда числового тракта производится переход к контролю следующих адресов. Для этого с помощью генератора (например, путем нажатия специальной кнопки) формируется сигнал повторного пуска автономного контроля, который устанавливает триггер 23 в нулевое состояние, в результате чего блок управления 13 и формирователь б возобновляют формирование временной диагра лы с момента останова, до конца режима автономного контроля или до следукяцего останова автокоя-. :гроля.

Если в устройстве произошел хотя ,бы один сбой, то после окончания режима автономного контроля (т.е. после трехкратного обхода адресов) триггер 20 остается в единичном состоянии, в результате чего триггер

18 не переключается в единичное сое гояние, и блок индикации указывает наличие сбоя в устройстве.

Технико-экономические преимущества описываемого устройства заключаются в значительном сокращении времени на обнаружение и локализацию неисправностей в оперативном запоминающем устройстве с самоконтролем за счет отказа от метода поразрядiioro контроля при многократном поoследовательном обходе адресов накопителя, применяемом в прототипе, и использования метода контроля всего слова при трехкратном последовательно-параллельном обходе адресов, что. повышает быстродействие и

s надежность устройства.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее накопитель, регистр числа, первый регистр адреса, первый бЛок контроля и второй блок контроля, формирователь контрольных импульсов, счетчик, первый дешифратор, первый, второй и третий блоки индикации, первую группу элементов , .первую, вторую и третью группы элементов И, блок управления, первый и второй генераторы одиночных импульсов, первый, второй, третий и четвертый триггеры, элемент ИЛИ, элемент И, блок местного управления, причем входы регистра числа подключены соответственно, к выходу первой группы элементов ИЛИ и перво / выходу Фop гиpoвaтeля контрольных импульсов, второй выход которого соединен с первыми входaivHi первой группы элементов ИЛИ, вторые входы которых подключены к выходам второй группы элементов И, выход регистра числа соединен с первыло входами первогр блока индикации, накопителя и третьей группы элементов И, выходы которых подключены к выходу устройства, первый выход первого регистра адреса соединен со вторыми входами накопителя и первого блока индикации и первым входомсчетчика, второй выход первого регистра адреса подключен к третьим входам накопителя и первого блока индикации, перBbLM входам формирователя контрольных импульсов, второго блока контроля и первого блока контроля, второй вход которого соединен с выходом накопителя, первый вход первого регистра адреса подключен к выхо дам первой группы элементов И, первые входы которых соединены с первым входом устройства, второй вход которого подключен к первым входам второй группы элементов И, выход первого генератора одиночных импульсов соединен с первыми входами первого триггера, элемента ИЛИ, второго триггера, третьего триггера и вторыми входами счетчика и первого регистра адреса, третий вход которого подключен к первому выходу блока управления, вход первого дешифратора соединен с выходом счетчика, а первый выход дешифратора подключен к первому входу элемента И и ко второму входу первого триггера, первый выход которого соединен со вторыми входами первой, второй и третьей групп элементов И, второй выход первого триггера подключен ко входу второго блокаиндикации, первому входу блока управления, вторым входам второго блока контроля и формирователя контрольных импульсов, выход первого блока контроля подключен ко второму входу третьего триггера и первому входу четвертого триггера, выход которого соединен со вторым входом блока управления и третьим входом формирователя контрольных импульсов, выход второго генератора одиночных импульсов подключен ко второму входу элемента-или, выход которого соединен со вторым входом четвертого триггера, второй вход второго триггера подключен к выходу элемента И, второй вход которого соединен с выходом третьего триггера, выход второго триггера подключен ко входу третьего блока индикации, входы блока местного управления подключены соответственно ко вторым выходам первого дешифратора, первого триггера и блока управления, а выход местного управления соединен со вторым входом второго блока контроля , с третьими входами первого блока контроля и блока управления и четвертым входом формирователя контрольных импульсов, отличающееся тем. Что, с целью повышения быстродействия и надежности устройства, оно содержит второй регистр адреса, третий генератор одиночных импульсов, второй дешифратор, коммутатор, вторую и третью группы 5 элементов ИЛИ и четвертую и пятую группы элементов И, причем входы второго регистра адреса подключены соответственно к выходам первого генератора одиночных импульсов, третьего генератора одиночных импульсов; и первой группы элементов И, а выход второго регистра адреса соединен с четвертым входом первого блока индикации и входом второго дешифратора, выход которого подключен к

первым входам четвертой и пятой групп элементов И, выходы которых соединены соответственно с первыми входами второй и третьей групп элементов

Q ИЛИ, вторые входы четвертой группы элементов И и третьей группы элементов ИЛИ подключены к первому входу первого триггера, второй вход которого соединен со вторыми входами второй группы .элементов ИЛИ и

пятой группы элементов И, выхода третьей группы элементов ИЛИ соединены, с первьгм входом коммутатора, второй вход которого подключен к выходу накопителя/ а выход - к тре0 тьим входам первой группы элементов ИЛИ, выходы второй группы элементов ИЛИ подключены к четвертому входу накопителя.

5 Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 329578, кл, G 11 С 29/00, 1970.

2.Авторское свидетельство СССР по заявке 2530307/18-24,

кл, G 11 с 29/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Запоминающее устройство | 1980 |

|

SU903973A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

Авторы

Даты

1980-10-15—Публикация

1978-07-27—Подача